Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Цель изобретения - повышение точности.

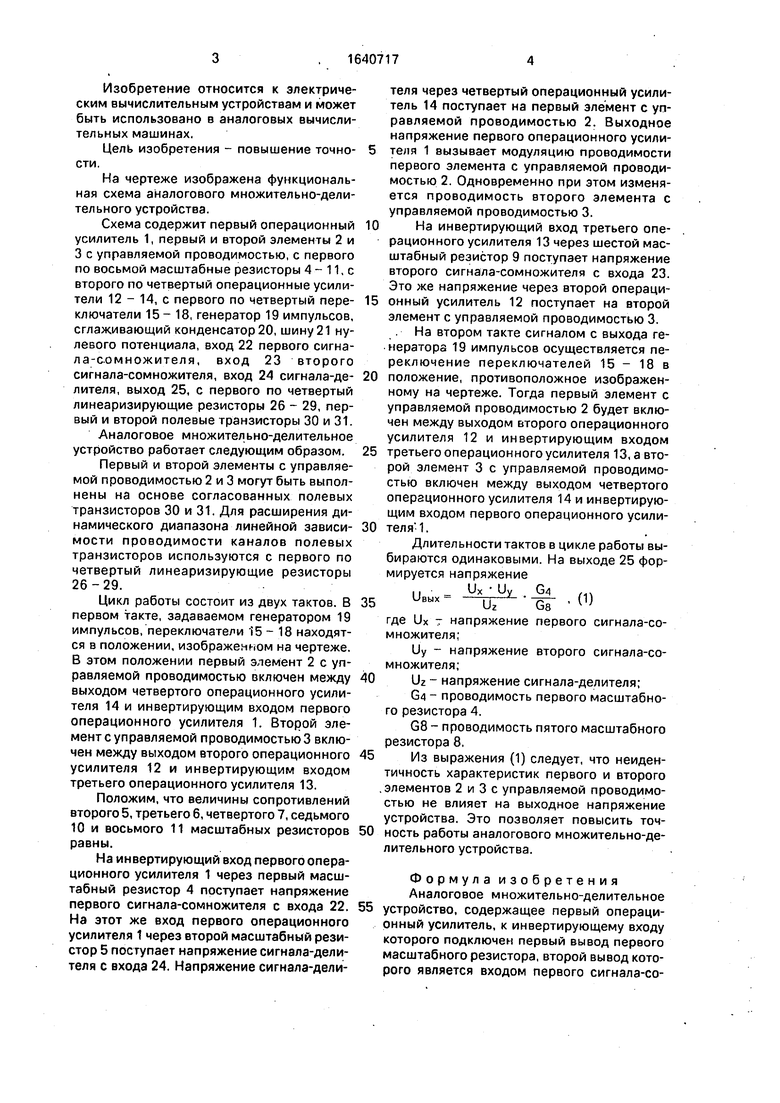

На чертеже изображена функциональная схема аналогового множительно-дели- тельного устройства.

Схема содержит первый операционный усилитель 1, первый и второй элементы 2 и 3 с управляемой проводимостью, с первого по восьмой масштабные резисторы 4 - 11, с второго по четвертый операционные усилители 12 - 14, с первого по четвертый переключатели 15- 18, генератор 19 импульсов, сглаживающий конденсатор 20, шину 21 нулевого потенциала, вход 22 первого сигна- ла-с.омножителя, вход 23 второго сигнала-сомножителя, вход 24 сигнала-делителя, выход 25, с первого по четвертый линеаризирующие резисторы 26 - 29, первый и второй полевые транзисторы 30 и 31.

Аналоговое множительно-делительное устройство работает следующим образом.

Первый и второй элементы с управляемой проводимостью 2 и 3 могут быть выполнены на основе согласованных полевых транзисторов 30 и 31. Для расширения динамического диапазона линейной зависимости проводимости каналов полевых транзисторов используются с первого по четвертый линеаризирующие резисторы 26-29.

Цикл работы состоит из двух тактов. В первом такте, задаваемом генератором 19 импульсов, переключатели 15-18 находятся в положении, изображенном на чертеже. В этом положении первый элемент 2 с управляемой проводимостью включен между выходом четвертого операционного усилителя 14 и инвертирующим входом первого операционного усилителя 1. Второй элемент с управляемой проводимостью 3 включен между выходом второго операционного усилителя 12 и инвертирующим входом третьего операционного усилителя 13.

Положим, что величины сопротивлений второго 5, третьего 6, четвертого 7, седьмого 10 и восьмого 11 масштабных резисторов равны.

На инвертирующий вход первого операционного усилителя 1 через первый масштабный резистор 4 поступает напряжение первого сигнала-сомножителя с входа 22. На этот же вход первого операционного усилителя 1 через второй масштабный резистор 5 поступает напряжение сигнала-делителя с входа 24. Напряжение сигнала-делителя через четвертый операционный усилитель 14 поступает на первый элемент с управляемой проводимостью 2. Выходное напряжение первого операционного усилителя 1 вызывает модуляцию проводимости первого элемента с управляемой проводимостью 2. Одновременно при этом изменяется проводимость второго элемента с управляемой проводимостью 3.

0 На инвертирующий вход третьего операционного усилителя 13 через шестой масштабный резистор 9 поступает напряжение второго сигнала-сомножителя с входа 23. Это же напряжение через второй операци5 онный усилитель 12 поступает на второй элемент с управляемой проводимостью 3. . На втором такте сигналом с выхода генератора 19 импульсов осуществляется переключение переключателей 15 - 18 в

0 положение, противоположное изображенному на чертеже. Тогда первый элемент с управляемой проводимостью 2 будет включен между выходом второго операционного усилителя 12 и инвертирующим входом

5 третьего операционного усилителя 13, а второй элемент 3 с управляемой проводимостью включен между выходом четвертого операционного усилителя 14 и инвертирующим входом первого операционного усили0 теля 1.

Длительности тактов в цикле работы выбираются одинаковыми. На выходе 25 формируется напряжение

Ux Uy GA

5

UE

- О)

UzG8

где Ux т напряжение первого сигнала-сомножителя:

Uy - напряжение второго сигнала-сомножителя;0 Uz - напряжение сигнала-делителя;

G4 - проводимость первого масштабного резистора 4.

G8 - проводимость пятого масштабного резистора 8.

5 Из выражения (1) следует, что неидентичность характеристик первого и второго .элементов 2 и 3 с управляемой проводимостью не влияет на выходное напряжение устройства. Это позволяет повысить точ- 0 ность работы аналогового множительно-де- лительного устройства.

Формула изобретения Аналоговое множительно-делительное 5 устройство, содержащее первый операционный усилитель, к инвертирующему входу которого подключен первый вывод первого масштабного резистора, второй вывод которого является входом первого сигнала-сомножителя устройства, входом сигнала-делителя устройства является первый вывод второго масштабного резистора, второй вывод которого соединен с инвертирующим входом первого операционного усилителя, второй операционный усилитель, между инвертирующим входом и выходом которого включен третий масштабный резистор, к инвертирующему входу второго операционного усилителя подключен первый вывод четвертого масштабного резистора, второй вывод которого является входом второго сигнала-сомножителя устройства, третий операционный усилитель, между инвертирующим входом и выходом которого вклю- чен пятый масштабный резистор, к инвертирующему входу третьего операционного усилителя подключен первый вывод шестого масштабного резистора, второй вывод которого соединен с вторым выводом четвертого масштабного резистора, первый и второй элементы с управляемой проводимостью, управляющие входы которых соединены с выходом первого операционного усилителя, неинвертирующие входы перво- го, второго и третьего операционных усилителей соединены с шиной нулевого потенциала, выход третьего операционного усилителя является выходом устройства, о т личающееся тем, что, с целью повыше- ния точности, в него введены четвертый операционный усилитель, седьмой и восьмой масштабные резисторы, с первого по четвертый переключатели, генератор импульсов и сглаживающий конденсатор, при- чем к первому выводу второго масштабного резистора подключен первый вывод седьмого масштабного резистора, второй вывод которого соединен с первым выводом

восьмого масштабного резистора и с инвер- тирующим входом четвертого операционного усилителя, к выходу которого подключен второй вывод восьмого масштабного резистора, выход четвертого операционного усилителя подключен к переключающему контакту первого переключателя, первый вывод которого соединен с первым выводом первого элемента с управляемой п, сводимостью, второй вывод которого подключен к первому выводу второго переключателя, переключающий контакт которого соединен с инвертирующим входом первого операционного усилителя, выход второго операционного усилителя подключен к переключающему контакту третьего переключателя, первый вывод которого соединен с первым выводом второго элемента с управляемой проводимостью и с вторым выводом первого переключателя, первый вывод которого подключен к второму выводу третьего переключателя, второй вывод второго элемента с управляемой проводимостью соединен с первым выводом четвертого переключателя и с вторым выводом второго переключателя, первый вывод которого подключен к второму выводу четвертого переключателя, переключающий контакт которого соединен с инвертирующим входом третьего операционного усилителя и с первой обкладкой сглаживающего конденсатора, вторая обкладка которого соединена с выходом третьего операционного усилителя, управляющие входы первого, второго, третьего и четвертого переключателей подключены к выходу генератора импульсов, неинвертирующий вход четвертого операционного усилителя соединен с шиной нулевого потенциала

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1980 |

|

SU888140A1 |

| Множительно-делительное устройство | 1986 |

|

SU1405077A1 |

| Аналоговое множительное устройство | 1985 |

|

SU1280401A1 |

| Аналоговое множительное устройство | 1986 |

|

SU1319047A1 |

| Элемент с управляемой проводимостью | 1986 |

|

SU1334164A1 |

| Множительное устройство | 1980 |

|

SU924720A1 |

| Множительно-делительное устройство | 1991 |

|

SU1791824A1 |

| Аналоговое множительное устройство | 1987 |

|

SU1497625A1 |

| Четырехквадратное множительно-делительное устройство | 1987 |

|

SU1474686A1 |

| Аналоговое множительно-делительное устройство | 1989 |

|

SU1644174A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности. Аналоговое множительно-делительное устройство содержит первый операционный усилитель 1, первый 2 и второй 3 элементы с управляемой проводимостью, с первого по восьмой масштабные резисторы 4...11, с второго по четвертый операционные усилители 12...14, с первого по четвертый переключатели 15.,.18, генератор 19 импульсов, сглаживающий конденсатор 20, шину 21 нулевого потенциала, вход 22 первого сигнала-сомножителя, вход 23 второго сигнала-сомножителя, вход 24 сигнала-делителя, выход 25, четыре линеаризирующих резистора 26.,.29, первый 30 и второй 31 полевые транзисторы. Работа устройства основана на передаче одного сигнала-сомножителя и сигнала-делителя через элементы 2,3с управляемой проводимостью и модуляции их проводимости другим сигна- лам-сомножителем. С целью повышения точности первый 2 и второй 3 элементы с управляемой проводимостью периодически переключаются в каналах передачи сигналов. 1 ил. (Л С о & VI

| Тимонтеев В.Н | |||

| и др | |||

| Аналоговые перемножители сигналов в радиоэлектронной аппаратуре | |||

| М.: Радио и связь, 1982, с | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Перемножитель аналоговых сигналов | 1985 |

|

SU1242992A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-07—Публикация

1989-04-03—Подача