1

Изобретение относится к электрй,ческим вычислительным устройствам, в частности к умножителям с переменной крутизной, и может быть использовано в аналоговых вычислительных машинах.

Один из известных умножителей содержит дифференциальные усилительные каскады, генераторы стабильного тока, управляемые элементы с дифференциальным включением LlJЭто устройство характеризуется сравнительно низкой точностью работы.

Известно также множительно-делительное устройство, содержащее дифференциальные усилительные каскады, дифференциальные преобразователи напряжение-ток, источник тока, блок опорных напряжений, линеаризующие диоды и нагрузочные резисторы L 21.

Недостатком этого устройства яв- . ляетйя малая точность работы вследствие узкого динамического диапазона сигнала-делителя и зависимости полосы пропускания одного из сигналов-сомножителей от величины сигнала-делителя .

Целью изобретения является повышение точности работы за счет расширения динамического диапазона сигнала-делителя, и полосы пропускания одного из сигналов-сомножителей.

10

С этой целью в известное множительно-делительное устройство, содержащее первый, второй и третий дифференциальные усилительные каскады, первый и второй дифференциаль15ные преобразователи напряжение-ток, источник тока, блок опорных напряжений, первьй,второй, третий и четвертый линеаризйрукядие диоды, первый и второй нагрузочные резисторы,

20 первый и второй выходы первого дифференциального усилительного каскада соединены соответственно с первым и вторым выходами второго дифференциального усилительного каскада, первый выход блока опорных напряжений соответственно через первый и второй нагрузочные резисторы подключен к первому и второму выходам первого дифференциального усилительного каскада, являющимися выходами множительно-делительного устройства, второй выход блока опорных напряжений через первый и второй линеаризирующие диоды подкхаочен соответственно к первому и второму выходам первого дифференциального преобразоватепя напряжение-ток и соответственно к первому и второму входам первого дифферен1щальногоусилительного каскада, входы первого дифференщ1ального преобразователя напряжение-ток являются первым входом множительно-делительного устройства, токозадающий вход третьего дифференциального усилительного каскада соединен с выходом источника тока, вход которого подключен к третьему выходу блока опо-рных напряжений, четвертый выход которого соответственно через третий и . четвертый линеаризирующий диоды подключен к первому и второму выходам второго дифференциального преобразователя напряжение-ток, пятый и шестой выходы блока опорных напряжений подключены соответственно к входам питания первого и второго дифференциальных преобразователей напряжение-ток, введены первый и вт рой управляемые источники тока и формирователь управляющих напряжений, причем первый и второй выходы первого и второго управляемых источников тока-соединены соответственно с первым и вторым выходами соответственно первого и второго преобразователей напряжение-ток, вхды первого и второго управляемых источников тока подключе11ы соответственно к первому и второму выходам формирователя управляющих напряжений, первый и второй выходы второго дифференциального преобразователя напряжение-ток подключены соответственно к первому и второму вход третьего дифференциального усилительного каскада, первый и второй выходы которого подключены к токозадающим входам соответственно первого и второго дифференциальных усилительных каскадов, первый вход второго дифференциального усилительног

каскада соединен с вторым входом первого дифференциального усилительного каскада, первый вход которого

подключен к второму входу IITOIW

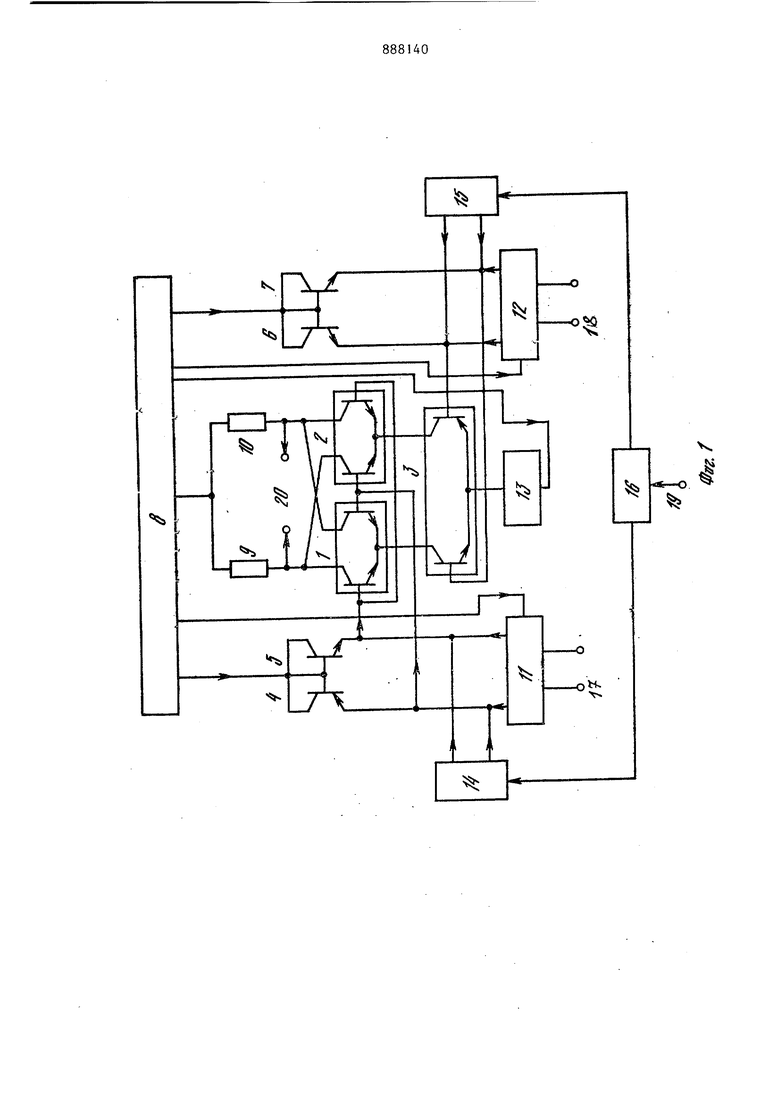

дифференпдального усилителыи; ,/ кас када, первый и второй входы второго дифференциального преобразователя напряжение-ток являются вторым входом множительно-делительного устройства, третьим входом которого является вход формирователя управляющих напряжений, а формирователь управляющих напряжений содержит первый, второй и третий операционные усилители, диодно-резистивный мост, источник эталонного напряжения и масштабные резисторы, инвертирующий вход первого операционного усилителя через первый масштабный резистор

соединен с входом формирователя

управляющих напряжений, а через второй масштабный резистор - с выходом источника эталонного напряжения, первая диагональ диодно-резистивно5 го моста подключена между инвертирующим входом и выходом первого операционного усилителя, вторая диагональ диодно-резистивного моста подключена к первым выводам соответственно третьего и четвертого масштабных резисторов, вторые вьшоды которых подключены к инвертирующим входам соответственно второго и третьего операционных усилителей, выход источника эталонного напряжения через пятый и шестой масштабные резисторы подключены соответственно к инвертирующим входам второго и третьего операционных усилителей, выходы которых являются соответственно первым и вторым выходами формирователя управляющих напряжений, между инвертирующими входами и выходами второго и третьего операционных усилителей подключены соответственно седьмой и восьмой масштабные резисторы, неинвертирующие входы первого, второго и третьего операционных усилителей соединены с шиной нулевого потенциала.

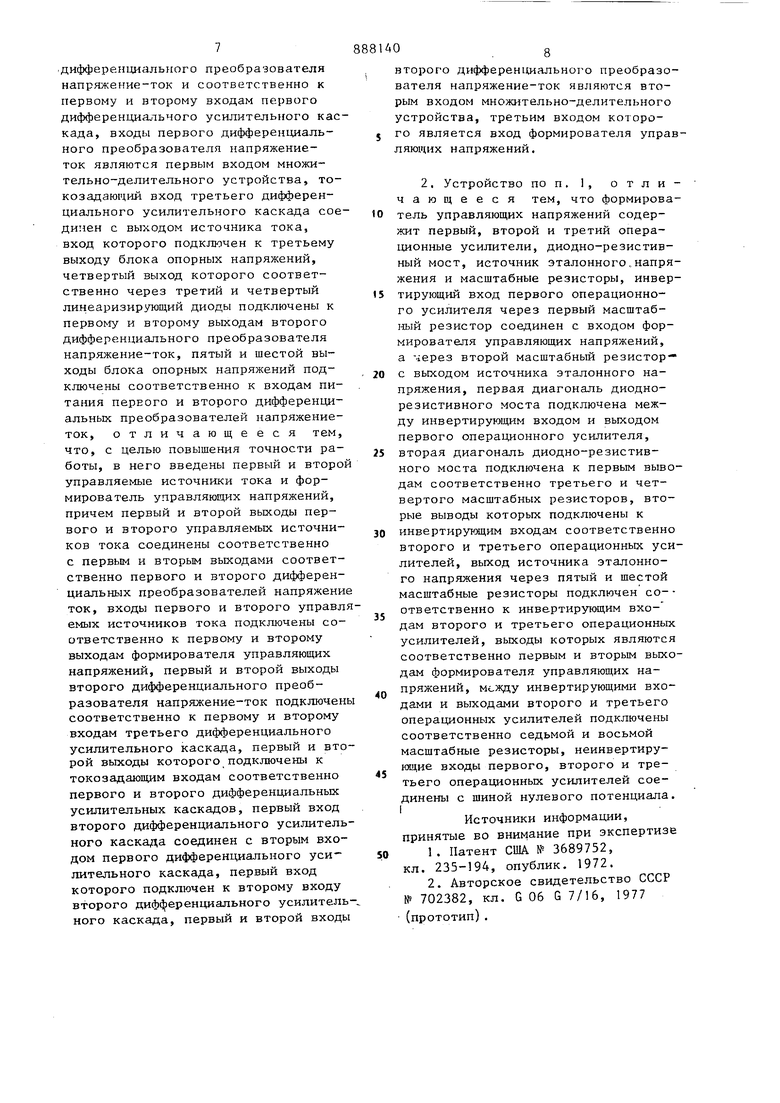

0 Функциональная схема предлагаемого множительно-делительного устройства изображена на фиг. 1; на фиг. 2 - функциональная схема формирователя управляющих напряжений.

5 Устройство содержит первый 1,

второй 2 и третий 3 дифференциальные усилительные каскады, первый 4, второй 5, третий 6 и четвертый 7 5 линеаризирующие диоды, блок 8 опорных напряжений, первый 9 и второй 10 нагрузочные резисторы, первый 11 и второй 12 дифференциальные преобразователи напряжение-ток, источник 13 тока, первый 14 и второй 15 управляемые источники тока, формирова ты1ь 16 управлякщих напряжений, пер вый 17, второй 18 и третий 19 входы и выход 20 множительно-делительного устройства, вход 21, первый 22 и второй 23 выходы формирователя управляющих напряжений, первый 24, второй 25 и третий 26 операционные усилители, источник 27 эталонного напряжения, первый 28, второй 29, третий 30, четвертый 31, пятьш 32, шестой 33, седьмой 34 и восьмой 35 масштабные резисторы, диодно-резистивный мост 36, шину 37 нулерого потенциала. Множительно-делительное устройство работает следукяцим образом. В режиме умножения один из преоб разуемых сигналов подается на вход 17, в результате на выходах преобразователей 11 происходит противофа ное изменение токов. Первый преобра зователь 11 и диоды 4 и 5, в качестве которых могут быть использованы транзисторы в диодном включении, представляют собой логарифмический усилитель с противофазными выходс1ми, поэтому результируюпщй си нал на входах блоков 1 и 2 каскадов пропорционален логарифму отношения токов, протекающих через диоды 4 и 5. Аналогично, от воздействия второго преобразуемого сигнала с входа 18, на входах каскада 3 сигнал пропорционален логарифму отношения токов, протекающих через диоды 6 и 7. Вследствие того, что первый и вт рой выходы как каскада I, так и кас када 2 взаимно противофазны и ни один из входных сигналов, поступающих на входы и токозадающие входы каскадов 1 и 2, на выход 20 не проходит, сигнал на выходе 20 пропорци овален произведению сигналов, дейст вующих на входах 17 и 18. При этом отсутствие любого из входных сигналов дает на выходе нулевое напряжение. При линейном возрастании напряже ния на третьем входе 19 происходит поочередное формирование управляю04щих напряжений на первом 22, а затем ня втором 23 выходах формирователя 16. Управляющие напряжения подаются на входы источников 14 и 15, выходные токи каждого из которых на первом и втором выходах изменяются синфазно и линейно. Поэтому во сколько раз возрастет (или уменьшится) напряжение на входе 19, во столько же раз уменьшится (или возрастет) напряжение на вькоде 20, т.е. осуществляется режим деления. Если, например, динамический диапазон изменения уровня сигнала на входе 19 принять равным 40 дБ, то токи преобразователей 11 и 12 остаются без изменений, а токи, протекающие через диоды 4, 5, 6 и 7, поочередно уменьшаются только на 20 дБ, при этом токи источников 14 и 15 увеличиваются менее, чем вдвое. Благодаря этому множительно-делительное устройство имеет более широкую полосу пропускания по входам I7 и 18 и больший динамический диапазон изменения уровня сигнала, действующего на входе 19, что значительно повьш1ает точность работы. Формула изобретения 1. Множительно-делительное устройство, содержащее первый, второй и третий дифференциальные усилительные каскады, первый и второй дифференциальные преобразователи напряжениеток, источник тока, блок опорных напряжений, первый, второй, третий и четвертый линеаризирующие диоды, первый и второй нагрузочные резисторы, первый и второй выходы первого дифференциального усилительного каскада соединены соот етственно с первым и вторым выходами второго дифференциального усилительного каскада, первый выход блока опорных напряжений через первый и второй нагрузочные резисторы подключены соответственно к первому и второму выходам первого дифференциального усилительного каскада, являющимися выходами множительно-делительного устройства, второй выход блока опорных напряжений через первый и второй линеаризирующие диоды подключен соответственно к первому и второму выходам первого

-дифференциального преобразователя напряжение-ток и соответственно к первому и второму входам первого диффepeндиaJ ьчoгo усилительного каскада, входы первого дифференциального преобразователя напряжениеток являются первым входом множительно-делительного устройства, токозадающий вход третьего дифференциального усилительного каскада соединен с выходом источника тока, вход которого подключен к третьему выходу блока опорных напряжений, четвертый выход которого соответственно через третий и четвертый линеаризирующий диоды подключены к первому и второму выходам второго дифференциального преобразователя напряжение-ток, пятый и шестой выходы блока опорных напряжений подключены соответственно к входам питания первого и второго дифференциальных преобразователей напряжениеток, отличающееся тем, что, с целью повышения точности работы, в него введены первый и второ управляемые источники тока и формирователь управляющих напряжений, причем первый и второй выходы первого и второго управляемых источников тока соединены соответственно с первым и вторым выходами соответственно первого и второго дифференциальных преобразователей напряжени ток, входы первого и второго управл емых источников тока подключены соответственно к первому и второму выходам формирователя управляющих напряжений, первый и второй выходы второго дифференциального преобразователя напряжение-ток подключен соответственно к первому и второму входам третьего дифференциального усилительного каскада, первый и второй выходы которого подключены к токозадающим входам соответственно первого и второго дифференциальных усилительных каскадов, первый вход второго дифференциального усилительного каскада соединен с вторым входом первого дифференциального усилительного каскада, первый вход которого подключен к второму входу второго дифференциального усилительного каскада, первый и второй входы

881АОg

, второго дифференциального преобразователя напряжение-ток являются вторьм входом множительно-делительного устройства, третьим входом котороJ го является вход формирователя управляющих напряжений.

2. Устройство по п. 1, отличающееся тем, что формирователь управляющих напряжений содержит первый, второй и третий операционные усилители, диодно-резистивный мост, источник эталонного,напряжения и масщтабные резисторы, инвертирующий вход первого операционного усилителя через первый масщтабный резистор соединен с входом формирователя управляющих напряжений, а через второй масштабный резистор 20 с выходом источника эталонного напряжения, первая диагональ диоднорезистивного моста подключена между инвертирующим входом и выходом первого операционного усилителя,

25 вторая диагональ диодно-резистивного моста подключена к первым выводам соответственно третьего и четвертого масштабных резисторов, вторые выводы которых подключены к

30 инвертирующим входам соответственно второго и третьего операционных усилителей, выход источника эталонного напряжения через пятый и шестой масштабные резисторы подключен со- ответственно к инвертирующим входам второго и третьего операционных усилителей, выходы которых являются соответственно первым и вторым выходам формирователя управляющих напряжений, между инвертирующими входами и выходами второго и третьего операционных усилителей подключены соответственно седьмой и восьмой масштабные резисторы, неинвертирующие входы первого, второго и третьего операционных усилителей соединены с шиной нулевого потенциала.

Источники информации, принятые во внимание при экспертизе 50 1. Патент США № 3689752, кл. 235-194, опублик. 1972.

2. Авторское свидетельство СССР № 702382, кл. G 06 G 7/16, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1982 |

|

SU1119037A1 |

| Четырехквадрантное множительное устройство | 1978 |

|

SU769559A1 |

| ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2252452C1 |

| Перемножающее устройство | 1987 |

|

SU1465896A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Аналоговое множительно-делительное устройство | 1989 |

|

SU1640717A1 |

| Времяимпульсное множительно-делительное устройство | 1985 |

|

SU1264209A1 |

| ЦИФРОУПРАВЛЯЕМЫЙ ЛОГАРИФМИЧЕСКИЙ УСИЛИТЕЛЬ | 2013 |

|

RU2568932C2 |

| Множительно-делительное устройство | 1981 |

|

SU995098A1 |

| Четырехквадрантное множительное устройство | 1980 |

|

SU957225A1 |

Авторы

Даты

1981-12-07—Публикация

1980-03-24—Подача