Изобретение относится к вычислительной технике и может быть использовано в аппаратуре обработки дискретных сигналов.

Цель изобретения - упрощение устройства.

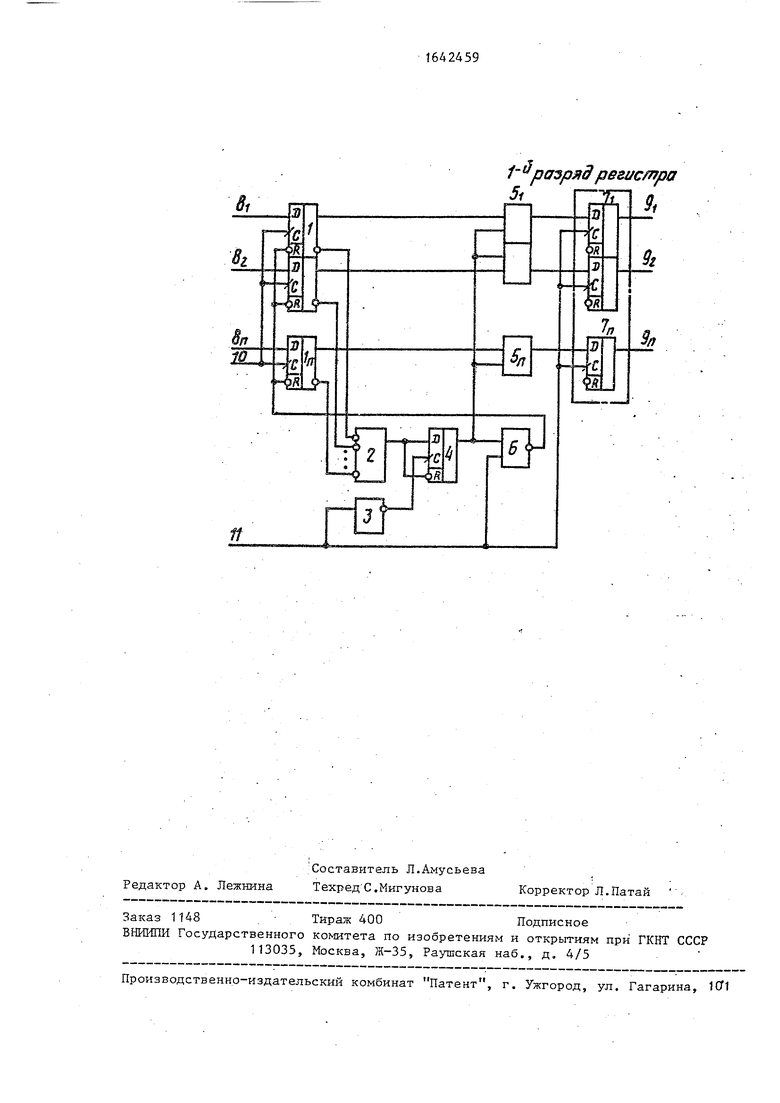

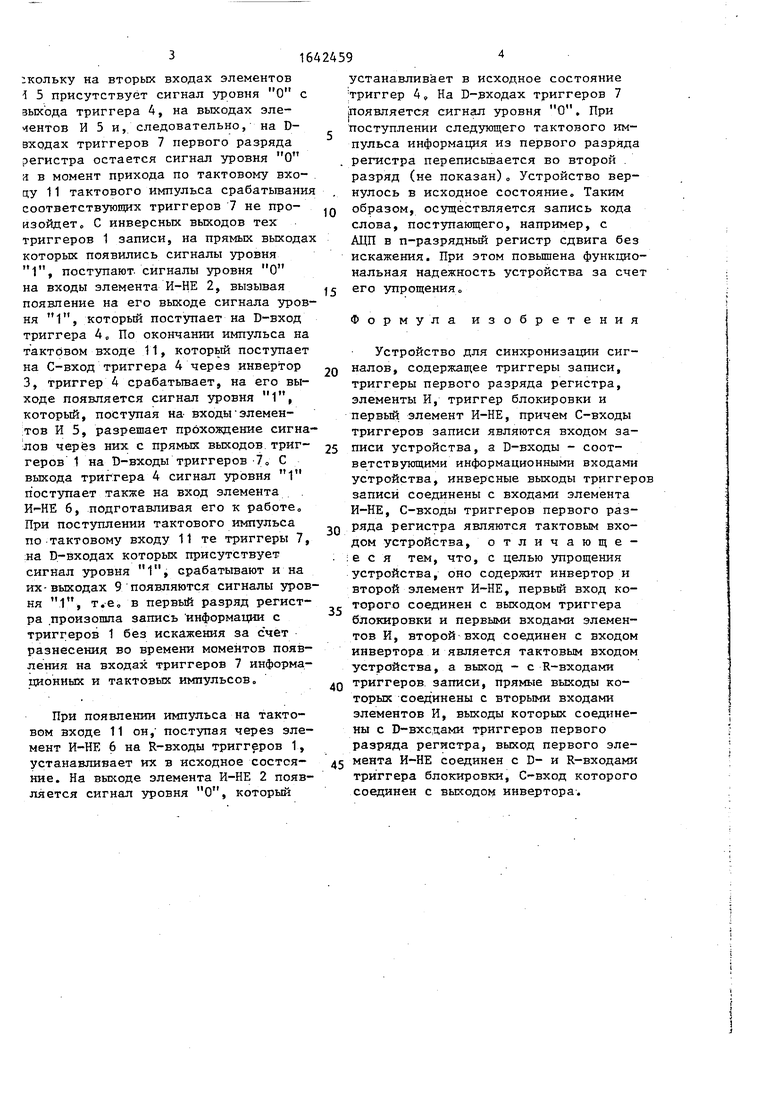

На чертеже приведена электрическая схема устройства для синхронизации сигналов„

В состав устройства входят триггеры 1 записи, первый элемент И-НЕ 2, инвертор 3, триггер 4 блокировки, элементы И 5, второй элемент И-НЕ 6 и триггеры 7 первого разряда регистра.

В устройстве используются D-триг- геры, срабатывающие по фронту CHI- нала на С-входе.

На чертеже обозначены 8 - информационные входы, соединенные с D- входами триггеров 1 записи; 9 - выходы триггеров 7, являющиеся выходами устройства; 10 - управляющий вход записи, соединенный с С-входами триггеров 1; 11 - тактовый вход, соединенный с С-входами триггеров 7, одним из входпв элемента И-НЕ 6 и через инвертор 3 с С-входом триггера 4 блокировки Прямые выходы триггеров 1 записи соединены с одним из входов соответствующих элементов 5 И, а инверсные - с входами элемента И-НЕ 2, выход которого соединен с D- и R- входами триггера 40 Выход триггера 4 соединен с другими входами элементов И 5 и элемента И-НЕ 6, выход которого соединен с R-входами триггеров 1

Устройство работает следующим образом

В исходном состоянии на прямых выходах триггеров 1, на выходе элемента И-НЕ 2,на выходе триггера 4, на выходах элементов,И 5 и на выходах 9 присутствуют сигналы уровня О,а на инверсных выходах триггеров 1 и на выходе элемента И-НЕ 6 - сигналы уровня 1.

На входы 8 устройства поступает, например, с АЦП код слова в виде сигналов уровней 1 и О. При появлении сигнала на входе 10 записи триггеры 1, на D-входах которых присутствует сигнал уровня 1, переключаются и на их выходах появляются сигналы уровня 1, которые поступают на первые входы элементов И 5. Пос

Ј

:кольку на вторых входах элементов 1 5 присутствует сигнал уровня О с зыхода триггера 4, на выходах эле- чентов И 5 и, следовательно, на D- входах триггеров 7 первого разряда регистра остается сигнал уровня О л. в момент прихода по тактовому вхо- цу 11 тактового импульса срабатывания соответствующих триггеров 7 не произойдет. С инверсных выходов тех триггеров 1 записи, на прямых выходах которых появились сигналы уровня 1, поступают сигналы уровня О на входы элемента И-НЕ 2, вызывая появление на его выходе сигнала уровня 1, который поступает на D-вход триггера 4„ По окончании импульса на тактовом входе 11, который поступает на С-вход триггера 4 через инвертор 3, триггер 4 срабатывает, на его выходе появляется сигнал уровня 1, который, поступая на входы элементов И 5, разрешает прохождение сигналов через них с прямых выходов триггеров 1 на D-входы триггеров 70 С выхода триггера 4 сигнал уровня 1 поступает также на вход элемента И-НЕ 6, подготавливая его к работе. При поступлении тактового импульса по тактовому входу 11 те триггеры 7, на D-входах которых присутствует сигнал уровня 1, срабатывают и на их- выходах 9 появляются сигналы уровня 1, т.е, в первый разряд регистра произошла запись информации с триггеров 1 без искажения за счет разнесения во времени моментов появления на входах триггеров 7 информационных и тактовых импульсов

При появлении импульса на тактовом входе 11 он, поступая через элемент И-НЕ 6 на R-входы триггеров 1, устанавливает их в исходное состояние. На выходе элемента И-НЕ 2 появляется сигнал уровня О, который

10

15

устанавливает в исходное состояние триггер 4, На D-зходах триггеров 7 появляется сигнал уровня О. При поступлении следующего тактового импульса информация из первого разряда регистра переписывается во второй разряд (не показан)„ Устройство вернулось в исходное состояние. Таким образом, осуществляется запись кода слова, поступающего, например, с АЦП в n-разрядный регистр сдвига без искажения. При этом повышена функциональная надежность устройства за счет его упрощения.

Формула изобретения

20

25

30

Устройство для синхронизации сигналов, содержащее триггеры записи, триггеры первого разряда регистра, элементы И, триггер блокировки и первый элемент И-НЕ, причем С-входы триггеров записи являются входом записи устройства, а D-входы - соответствующими информационными входами устройства, инверсные выходы триггеров записи соединены с входами элемента И-НЕ, С-входы триггеров первого разряда регистра являются тактовым входом устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит инвертор и второй элемент И-НЕ, первый вход которого соединен с выходом триггера блокировки и первыми входами элементов И, второй вход соединен с входом инвертора и является тактовым входом устройства, а выход - с Н-входами триггеров записи, прямые выходы которых соединены с вторыми входами элементов И, выходы которых соединены с D-вхсцами триггеров первого разряда регистра, выход первого эле- 45 мента И-НЕ соединен с D- и R-входами триггера блокировки, С-вход которого соединен с выходом инвертора.

35

40

устанавливает в исходное состояние триггер 4, На D-зходах триггеров 7 появляется сигнал уровня О. При поступлении следующего тактового импульса информация из первого разряда регистра переписывается во второй разряд (не показан)„ Устройство вернулось в исходное состояние. Таким образом, осуществляется запись кода слова, поступающего, например, с АЦП в n-разрядный регистр сдвига без искажения. При этом повышена функциональная надежность устройства за сче его упрощения.

Формула изобретения

/ разряд регистра

А

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации приема сигналов | 1987 |

|

SU1513435A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1522271A1 |

| Устройство для измерения динамической погрешности аналого-цифровых преобразователей | 1987 |

|

SU1529453A1 |

| Устройство для сбора данных | 1984 |

|

SU1213427A1 |

| ИОНИЗАЦИОННЫЙ ФИЛЬТР ДЛЯ ОЧИСТКИ ВОЗДУХА | 1992 |

|

RU2009717C1 |

| Устройство для считывания графической информации | 1989 |

|

SU1654852A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

| Статистический анализатор условной функции распределения размахов колебаний напряжения | 1982 |

|

SU1092423A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре обработки дискретных сигналов. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет того, что устройство содержит инвертор и второй элемент И-НЕ. 1 ил.

| Устройство для ввода информации в сдвиговый регистр | 1970 |

|

SU474051A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для синхронизации приема сигналов | 1987 |

|

SU1513435A1 |

Авторы

Даты

1991-04-15—Публикация

1989-02-01—Подача