1 регистр

Z peeucfff/}

(/

| название | год | авторы | номер документа |

|---|---|---|---|

| Расширитель импульсов | 1981 |

|

SU1014133A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1260953A1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| Устройство для синхронизации сигналов | 1989 |

|

SU1642459A1 |

| Устройство для управления электропитанием и формирования сигнала блокировки | 1989 |

|

SU1709317A1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2110831C1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1176328A1 |

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре обработки дискретных сигналов. Целью изобретения является расширение области применения устройства за счет возможности синхронизации многоразрядных кодов. Для достижения цели в устройство, содержащее триггеры 1 записи, триггеры первого 6 и второго 7 разрядов регистра сдвига, введены элемент И-НЕ 2, триггер 4 блокировки и блок 3 сравнения, выходы которого соединены с выходами триггеров 1 записи и триггеров 6 первого разряда. При этом перепись информации в триггеры 7 второго разряда будет только тогда, когда коды в триггерах 1 и 6 будут одинаковыми. 1 ил.

10

со

Olib 00 сл

315

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре обработки дискретных сигналов.

Цель изобретения - расширение области применения устройства за счет возможности синхронизации многозарядных сигналов.

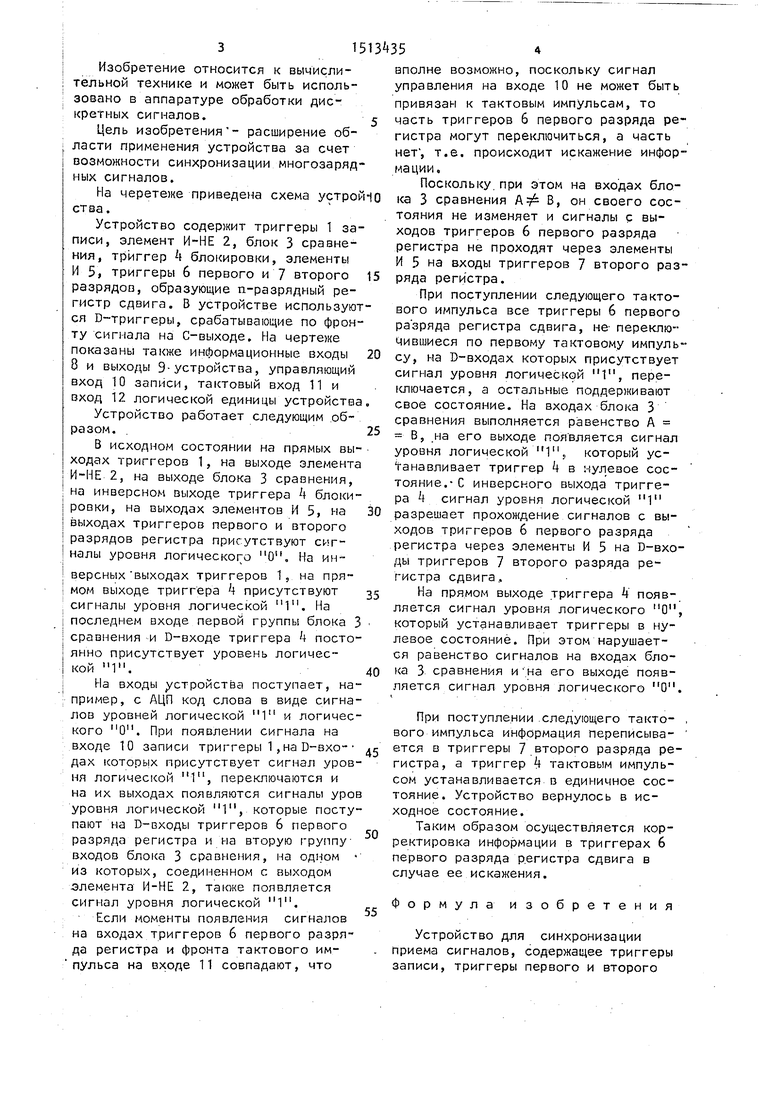

На черетеже приведена схема устрой ства.

Устройство содержит триггеры 1 записи, элемент И-НЕ 2, блок 3 сравнения, триггер k блокировки, элементы И 5, триггеры 6 первого и 7 второго разрядов, образующие п-разрядный регистр сдвига. В устройстве используются D-триггеры, срабатывающие по фронту сигнала на С-выходе. На чертеже показаны также информационные входы 8 и выходы 9-устройства, управляющий вход 10 записи, тактовый вход 11 и вход 12 логической единицы устройства

Устройство работает следующим .образом. .

В исходном состоянии на прямых выходах триггеров 1, на выходе элемента И-НЕ 2, на выходе блока 3 сравнения, на инверсном выходе триггера + блокировки, на выходах элементов И 5, на выходах триггеров первого и второго разрядов регистра присутствуют сигналы уровня логического О. На ин

версных выходах триггеров 1, на прямом выходе триггера 4 присутствуют сигналы уровня логической 1. На последнем входе первой группы блока 3 сравнения и D-входе триггера 4 постоянно присутствует уровень логичес

На входы устройства поступает, например, с АЦП код слова в виде сигнаи логичесПри появлении сигнала на входе 10 записи триггеры 1 ,на D-BXO- дах которых присутствует сигнал уровня логической 1, переключаются и на их выходах появляются сигналы уров уровня логической 1, которые поступают на D-входы триггеров 6 первого разряда регистра и на вторую группу входов блока 3 сравнения, на одном из которых, соединенном с выходом -Элемента И-НЕ 2, также появляется сигнал уровня логической 1. Если моменты появления сигналов на входах триггеров 6 первого разряда регистра и фронта тактового импульса на входе 11 совпадают, что

лов уровней логической 1 кого О,

вполне возможно, поскольку сигнал управления на входе 10 не может быть привязан к тактовым импульсам, то часть триггеров 6 первого разряда регистра могут переключиться, а часть нет , т.е. происходит искажение информации.

Поскольку,при этом на входах блока 3 сравнения А В, он своего состояния не изменяет и сигналы с выходов триггеров 6 первого разряда регистра не проходят через элементы И 5 на входы триггеров 7 второго разряда реги стра.

При поступлении следующего тактового импульса все триггеры 6 первого разряда регистра сдвига, не переключившиеся по первому тактовому импуль су, на D-входах которых присутствует сигнал уровня логической 1, пере

свое состояние. На входах блока 3 сравнения выполняется равенство А В, на его выходе появляется сигнал уровня логической который ус- taнaвливaeт триггер k в состояние.- С инверсного выхода триггера k сигнал уровня логической 1 разрешает прохождение сигналов с выходов триггеров 6 первого разряда регистра через элементы И 5 на D-входы триггеров 7 второго разряда регистра сдвига.

На прямом выходе триггера 4 появляется сигнал уровня логического О, который устанавливает триггеры в нулевое состояние. При этом нарушается равенство сигналов на входах блока 3 сравнения и .на его выходе появляется сигнал уровня логического О.

При поступле.нии .следующего такто- , вого импульса информация переписыва- ется ЕЗ триггеры 7 второго разряда регистра, а триггер тактовым импульсом устанавливается в единичное состояние. Устройство вернулось в исходное состояние.

Таким образом осуществляется корректировка информации в триггерах 6 первого разряда регистра сдвига в случае ее искажения.

Формула изобретения

Устройство для синхронизации приема сигналов, содержащее триггеры записи, триггеры первого и второго

регистров, элементы И, причем С-вхо- ды триггеров записи являются входом записи, а D-входы - соответствующими информационными входами устройства, прямые выходы триггеров записи соединены с D-входами триггеров первого регистра, выходы которых соединен с первыми входами соответствующих элементов И, С-входы .триггеров первого и второго регистров являются тактовым входом устройства, а выходы триггеров второго регистра - информационными выходами устройства, отличающееся тем, что, с целью расширения области применения за счет возможности синхронизации многоразрядных сигналов, в него введены элемент И-НЕ, триггер блокировки и блок сравнения, входы первой

и второй групп которого, кроме последних, соединены соответственно с прямыми выходами триггеров первого регистра и триггеров записи, последний вход первой группы и D-вход триггера блокировки являются входом логической единицы устройства, а последний вход второй группы соединен с выходом элемента И-НЕ, входы которого соединены с инверсными выходами триггеров записи, выход блока сравнения соединен с R-входом триггера блокировки, С-вход которого соединен с С-входами триггеров первого регистра, прямой выход - с R-входами триггеров записи, а инверсный - с вторыми входами элементов И, выходы которых соединены с D-входами соответствующих триггеров второго регистра.

| Авторское свидетельство СССР № , кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № , кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-10-07—Публикация

1987-11-25—Подача