1

(21)447.3910/24

(22)15.08.88

(46) 15.04,91. Бюл„ № 14

(72) В.И. Гостев и А.А. Варанов

(53) 681.327(088.8)

(56)Авторское свидетельство СССР № 1117623, кл. G 06 F 3/00, 1984,

Патент США № 4151596,

кло G 06 F 3/00, 1979.

i

(54) УСТРОЙСТВО ДЛЯ ВЫВОДА ДАННЫХ ИЗ МИКРОКАЛЬКУЛЯТОРА

(57)Изобретение относится к вычислительной технике и может быть использовано в учебных лабораториях при автоматизации экспериментальных исследований, Целью изобретения является расширение области применения устройства за счет автоматизации вывода данных из микрокалькулятора. Устройство содержит микрокалькулятор 1, состоящий из вычислителя 2, клавиатуры 3 и индикатора 4, первый 5, второй 6 и третий 7 блоки согласова- ,ния уровней, коммутатор 8, блок 9 Декодирования, блок 10 управления, блок 11 буферной памятно Применение устройства позволяет выключить ошибки оператора при выводе данных и использовать микрокалькулятор в простейших системах автоматизированного управления. 6 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода данных в микрокалькулятор | 1988 |

|

SU1635169A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| ТРЕНАЖЕР МНЕМОСХЕМ | 1990 |

|

RU2101772C1 |

| СИСТЕМА ИНДИКАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2001 |

|

RU2206872C2 |

| Устройство для отображения графической информации | 1984 |

|

SU1327090A1 |

| Устройство для обмена информацией | 1974 |

|

SU732848A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

сь

J N

4-

Ьэ

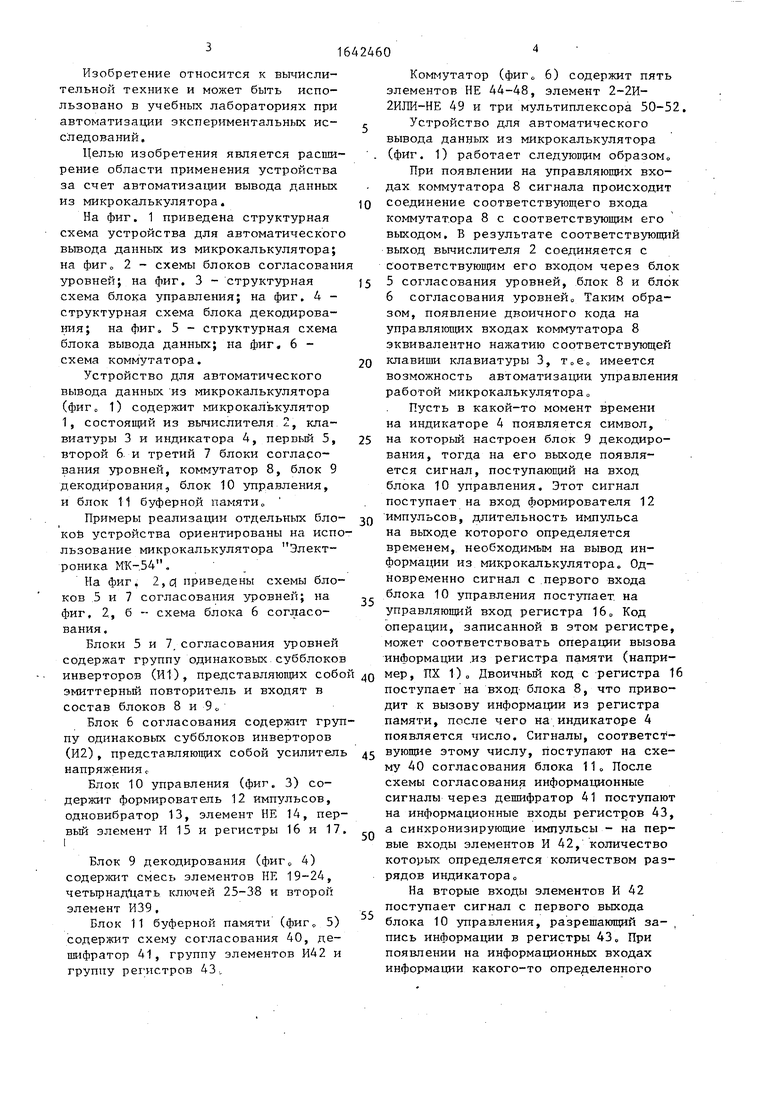

Фиг.1

Изобретение относится к вычислительной технике и может быть использовано в учебных лабораториях при автоматизации экспериментальных ис- следований.

Целью изобретения является расширение области применения устройства за счет автоматизации вывода данных из микрокалькулятора.

На фиг. 1 приведена структурная схема устройства для автоматического вывода данных из микрокалькулятора; на фиг о 2 - схемы блоков согласовани уровней; на фиг. 3 - структурная схема блока управления; на фиг. 4 - структурная схема блока декодирования; на фиг. 5 - структурная схема блока вывода данных; на фиг. 6 - схема коммутатора.

Устройство для автоматического вывода данных из микрокалькулятора (фиг„ 1) содержит микрокалькулятор 1, состоящий из вычислителя 2, клавиатуры 3 и индикатора 4, первый 5, второй 6 и третий 7 блоки согласования уровней, коммутатор 8, блок 9 декодирования, блок 10 управления, и блок 11 буферной памяти

Примеры реализации отдельных бло- ков устройства ориентированы на использование микрокалькулятора Электроника МК-54.

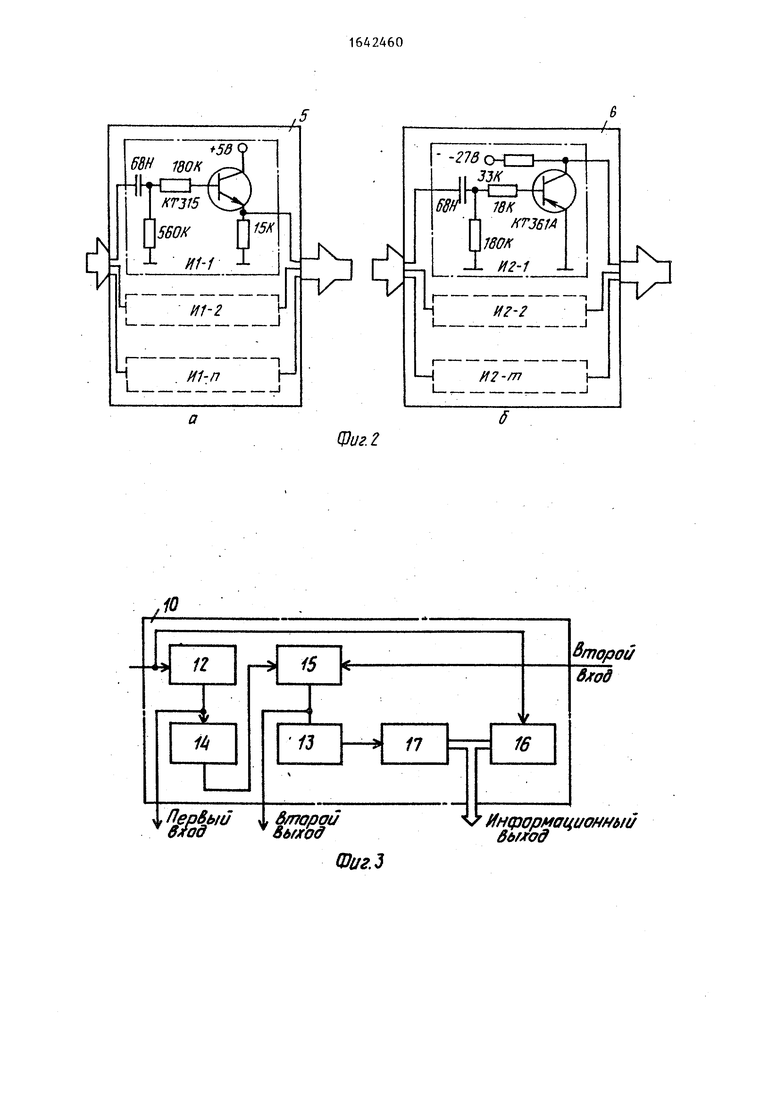

На фиг. 2, а приведены схемы блоков 5 и 7 согласования уровней; на фиг, 2, б -- схема блока 6 согласования .

Блоки 5 и 7.согласования уровней содержат группу одинаковых субблоков инверторов (И1), представляющих собо эмиттерный повторитель и входят в состав блоков 8 и 9„

Блок 6 согласования содержит группу одинаковых субблоков инверторов (И2), представляющих собой усилитель напряжения f

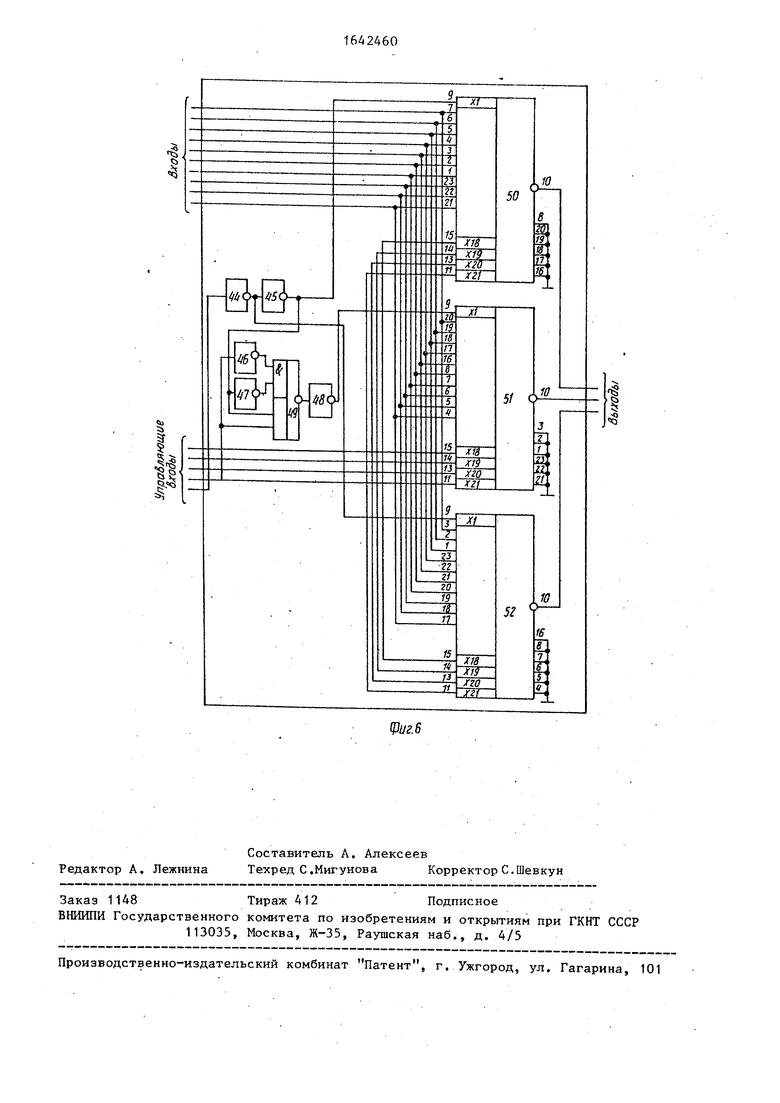

Блок 10 управления (фиг. 3) содержит формирователь 12 импульсов, одновибратор 13, элемент НЕ 14, первый элемент И 15 и регистры 16 и 17.

Блок 9 декодирования (фиг„ 4) содержит смесь элементов НЕ 19-24, четырнадцать ключей 25-38 и второй элемент И39,

Блок 11 буферной памяти (фиг,, 5) содержит схему согласования 40, дешифратор 41, группу элементов И42 и группу регистров 43,

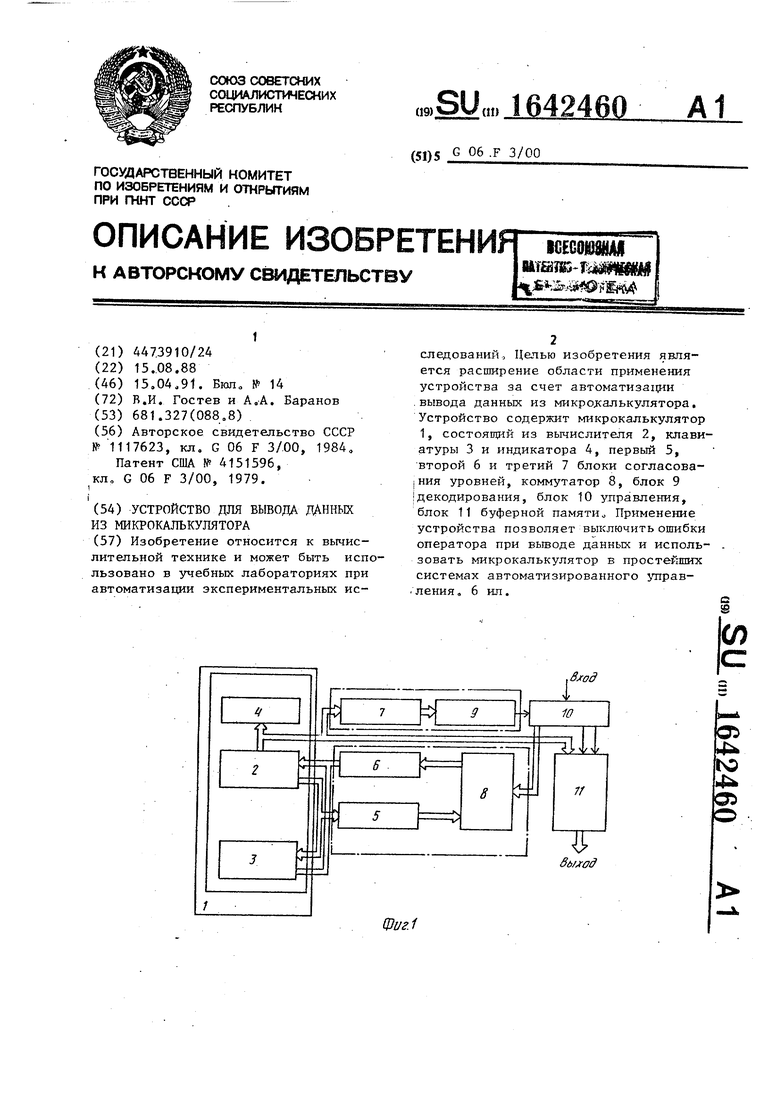

Коммутатор (фиг о 6) содержит пять элементов НЕ 44-48, элемент 2-2И- 2ИЛИ-НЕ 49 и три мультиплексора 50-52

Устройство для автоматического вывода данных из микрокалькулятора (фиг. 1) работает следующим образом

При появлении на управляющих входах коммутатора 8 сигнала происходит соединение соответствующего входа коммутатора 8 с соответствующим его выходом, В результате соответствующий выход вычислителя 2 соединяется с соответствующим его входом через блок

5согласования уровней, блок 8 и блок

6согласования уровней Таким образом, появление двоичного кода на управляющих входах коммутатора 8 эквивалентно нажатию соответствующей клавиши клавиатуры 3, т„е0 имеется возможность автоматизации управления работой микрокалькулятора о

Пусть в какой-то момент времени на индикаторе 4 появляется символ, на который настроен блок 9 декодирования, тогда на его выходе появляется сигнал, поступающий на вход блока 10 управления. Этот сигнал поступает на вход формирователя 12 импульсов, длительность импульса на выходе которого определяется временем, необходимым на вывод информации из микрокалькулятора Одновременно сигнал с первого входа блока 10 управления поступает на управляющий вход регистра 16„ Код операции, записанной в этом регистре, может соответствовать операции вызова информации из регистра памяти (например, ПХ 1)0 Двоичный код с регистра 1 поступает на вход блока 8, что приводит к вызову информации из регистра памяти, после чего на индикаторе 4 появляется число. Сигналы, соответствующие этому числу, поступают на схему 40 согласования блока 11„ После схемы согласования информационные сигналы через дешифратор 41 поступают на информационные входы регистров 43, а синхронизирующие импульсы - на первые входы элементов И 42, количество которых определяется количеством разрядов индикатора о

На вторые входы элементов И 42 поступает сигнал с первого выхода блока 10 управления, разрешающий запись информации в регистры 43„ При появлении на информационных входах информации какого-то определенного

5

разряда индикатора -одновременно по .ляется и синхронизирующий импульс именно этого разряда, Поэтому инфоция записывается в соответствующий регистр. По окончании записи инфорции в регистры 43 импульс с выход формирователя 12 импульсов заканчиется. После прихода из внешней сисмы импульса запроса данных с выход элемента И 15 сигнал поступает на вторые управляющие входы регистров при этом происходит вывод данных Кроме того, этот сигнал приводит к срабатыванию одновибратора 13, по пульсу которого осуществляется счивание с регистра 17 двоичного кода команды С/П (продолжения счета прораммы) . Так как во время останова информация в микрокалькуляторе не разрушилась, то продолжение выполнения программы не вызывает затруднений. Двоичный код поступает на вход коммутатора 8, и происходит запуск выполнения программы,

Фрагмент программы, обеспечивающий автоматический вывод данных , следующий.

В необходимое место исходной программы включается операция вызова на индикатор хранящегося символа ПХО (при этом подразумевается, что символ хранится в регистре 0, но может и в любом другом)„ После вызова символа программа останавливается для вывода данных (операция С/П)„ Таким образом, вычисления останавливаются, на индикаторе отображается требуемый символ, обозначающий разрешение вывода данных Формирование и запись символа производятся до начала выполнения программы. Так, для микрокалькулятора Электроника МК-54 это делается при помощи последовательности операций, например

t

15 ВП 99

ВП

хПО,

при этом формируется и записывается символ ЕБ,

Алгоритм выполнения любой программы имеет вид ,„„0.„(текст программы до момента вывода данных) ПХО С/П «.о.(дальнейший текст программы после вывода данных)„

0

5

Таким образом обычное выполнение программы происходит до тех пор, пока не будет вызван символ из регистра, после этого происходит останов выполнения программы, запускается работа блоков устройства и данные автоматически выводятся из микрокалькулятора. После вывода данных выполнение программы продолжается или до последующего вывода данных, или до момента ее естественного останова.

Формула изобретения

Устройство для вывода данных из микрокалькулятора, содержащее вычислитель, входы которого соединены с информационными выходами клавиатуры, управляющие входы которой соединены с первой группой выходов вычислите

5

соединена с входами индикатора, о т- л и чающееся тем, что, с целью расширения области применения за счет автоматизации вывода данных из микрокалькулятора, в него введены первый, второй и третий блоки согласования уровней, коммутатор, блок декодирования, блок управления, блок буферной памяти, выходы которого являются информационными выходами устройства, первый и второй управляющие входы блока буферной памяти соединены с соответствующими выходами блока управления, группа управляющих выходов которого соединена с управляющими входами коммутатора, выходы которого соединены с входами второго блока согласования уровней, выходы которого соединены с входами вычислителя, первая группа выходов которого соединена с входами первого блока согласования уровней, выходы которого соединены с информационными входами коммутатора, информационные входы блока буферной памяти соединены с входами индикатора и третьего блока согласования уровней, выходы которого соединены с входами блока декодирования, выход которого соединен с первым входом блока управления, второй вход которого является управляющим входом устройства .

Qox/vg лнннолЬоиаосЬни л

91

ЛОС/ОШд

мт,

t п& gad ц

U

U.

Н

$

г

т

Z tnfa

09V2V9t

goxgnodotug

gox§ пюдс/ац

ггпф

(WZMt

Авторы

Даты

1991-04-15—Публикация

1988-08-15—Подача