1

(21)4786671/24 (22)30.01.90 (46)15.11.91. Бюл. №42

(71)Научно-производственное объединение Кибернетика

(72)Л.В.Друзь и Ю.П.Рукоданов (53)681.327.11(088.8)

(56)Авторское свидетельство СССР № 714388, кл. G 06 F 3/06, 1980.

Авторское свидетельство СССР № 1434445, кл. G 06 F 13/00, 1987.

(54) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ ОТ ДАТЧИКОВ

(57)Изобретение относится к вычислительной технике и может быть использовано в

системах обработки информации, поступающей от дискретных датчиков однотипных объектов. Целью изобретения является расширение области применения устройства за счет получения обобщенной информации о состоянии задействованных датчиков. Устройство содержит элементы ИЛИ 1,20, блок сравнения 4, блок индикации 6, регистр 7, формирователь импульсов 8, блок памяти 9, мультиплексор 10, дешифраторы 11, 12, мажоритарный элемент 13, счетчики 2, 14 и 15, триггеры 16, 21 и 22, датчики 23, элементы И 17-19. В устройстве обеспечивается формирование суммарных сигналов о состоянии объектов на определенных этапах их функционирования. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сбора и обработки информации | 1988 |

|

SU1524078A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| Устройство для ввода информации | 1985 |

|

SU1282107A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Устройство для ввода информации | 1989 |

|

SU1644120A2 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для индикации | 1989 |

|

SU1649602A1 |

| Устройство для сопряжения памяти с процессором | 1983 |

|

SU1142838A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

Объект 1 I Объект п Объект

Ё

О

о

00

ю

00

ТИ

Фаг 1

Изобретение относится к вычислительной технике и может быть использовано в системах обработки информации, поступающей от дискретных датчиков однотипных объектов.

Цель изобретения - расширение области применения устройства за счет получения обобщенной информации о состоянии задействованных датчиков.

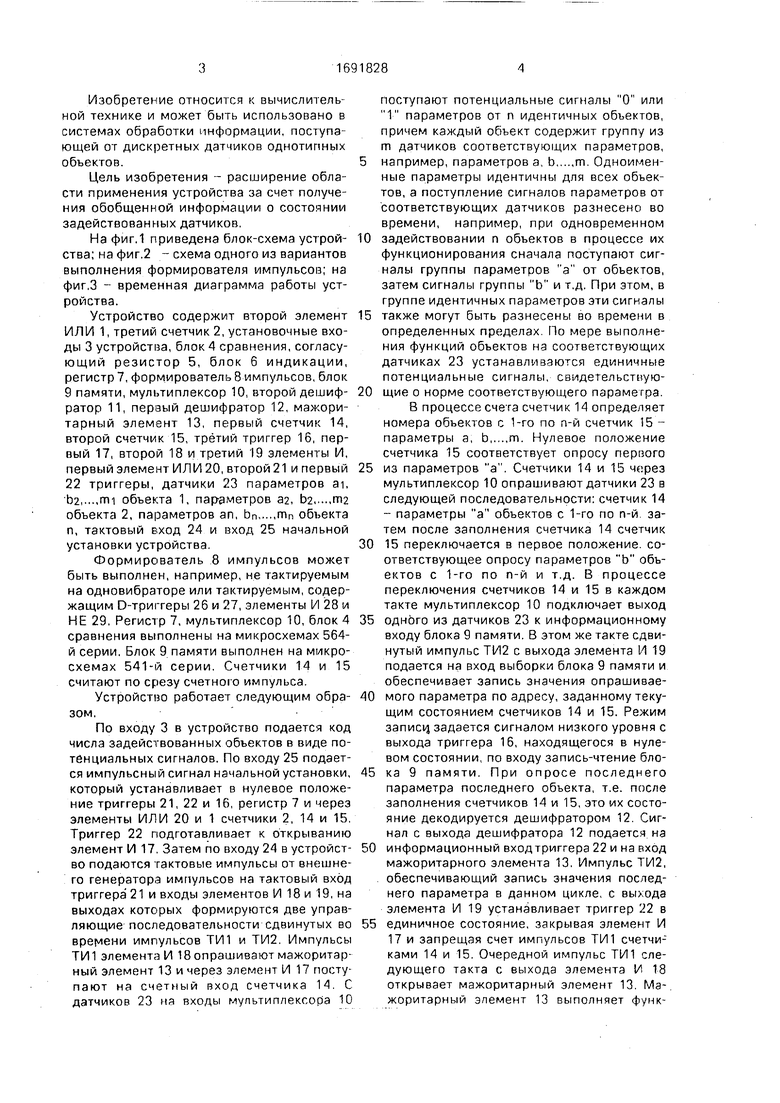

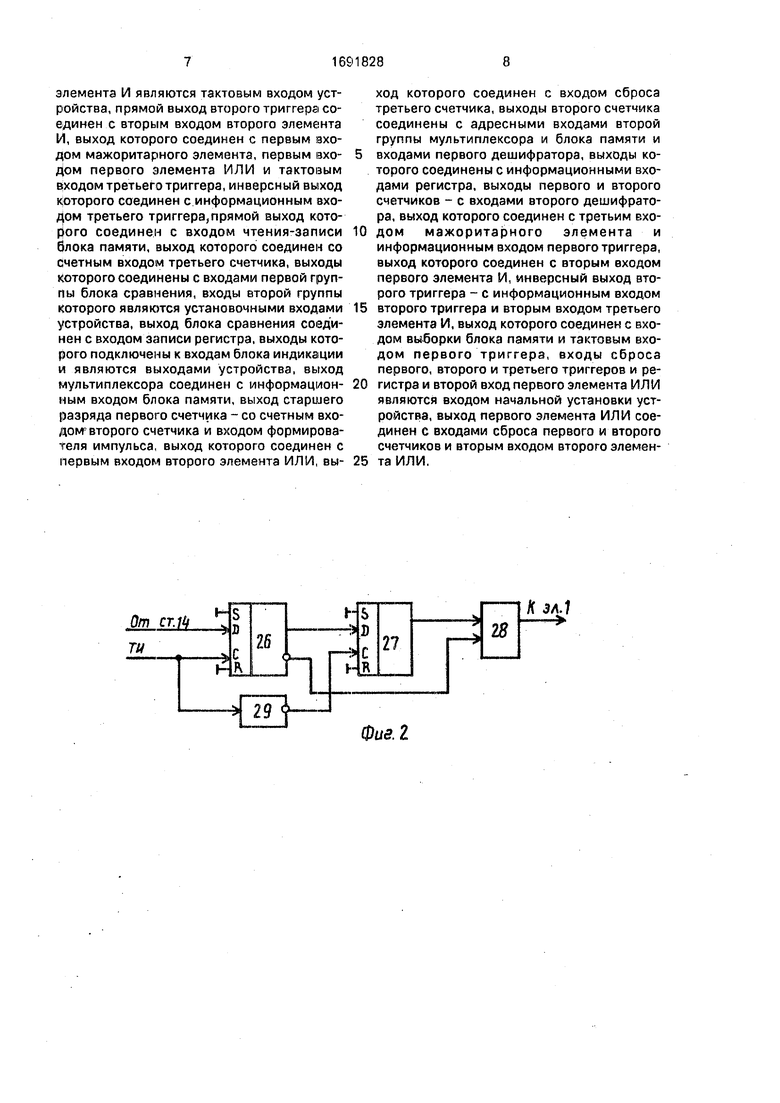

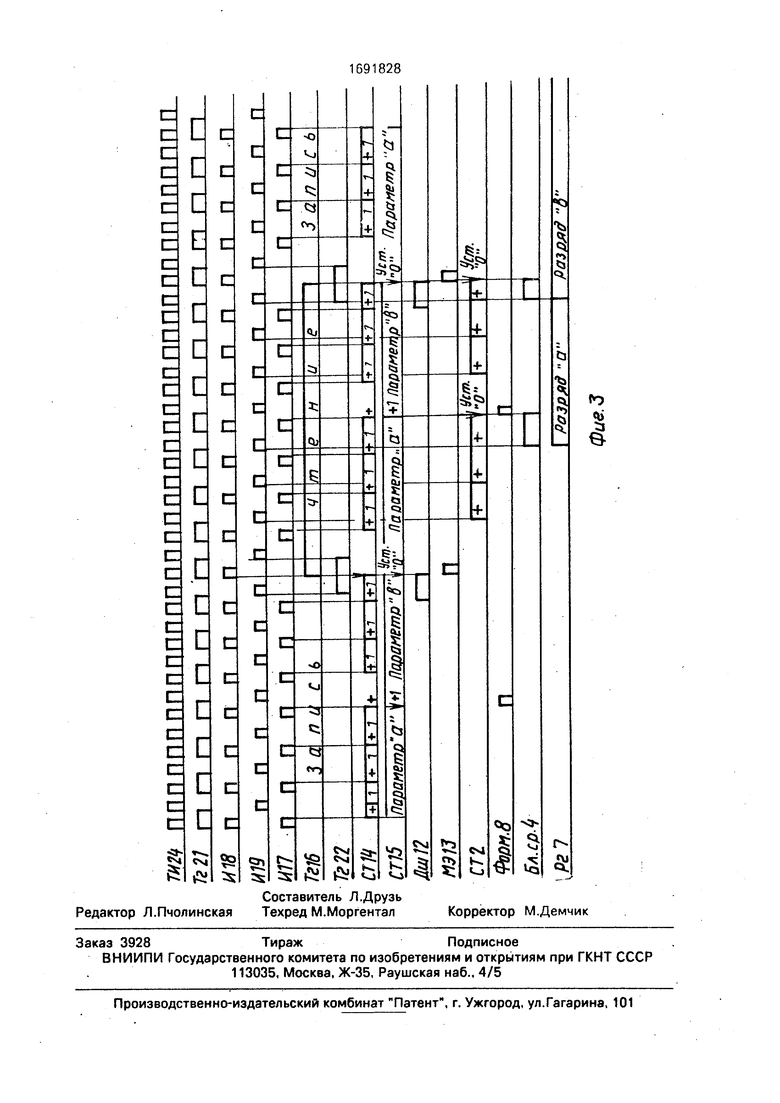

На фиг,1 приведена блок-схема устройства; на фиг.2 - схема одного из вариантов выполнения формирователя импульсов; на фиг.З - временная диаграмма работы устройства.

Устройство содержит второй элемент ИЛИ 1, третий счетчик 2, установочные входы 3 устройства, блок 4 сравнения,согласующий резистор 5, блок 6 индикации, регистр 7, формирователь 8 импульсов, блок 9 памяти, мультиплексор 10, второй дешифратор 11, первый дешифратор 12, мажоритарный элемент 13, первый счетчик 14, второй счетчик 15, третий триггер 16, первый 17, второй 18 и третий 19 элементы И, первый элемент ИЛИ 20, второй 21 и первый 22 триггеры, датчики 23 параметров ai,

b2mi объекта 1, пар-аметров 32, b2,...,iri2

объекта 2, параметров an, bnmn объекта

п, тактовый вход 24 и вход 25 начальной установки устройства.

Формирователь 8 импульсов может быть выполнен, например, не тактируемым на одновибраторе или тактируемым, содержащим D-триггеры 26 и 27, элементы И 28 и НЕ 29, Регистр 7, мультиплексор 10, блок 4 сравнения выполнены на микросхемах 564- й серии. Блок 9 памяти выполнен на микросхемах 541-й серии. Счетчики 14 и 15 считают по срезу счетного импульса.

Устройство работает следующим образом,

По входу 3 в устройство подается код числа задействованных объектов в виде потенциальных сигналов. По входу 25 подается импульсный сигнал начальной установки, который устанавливает в нулевое положение триггеры 21, 22 и 16, регистр 7 и через элементы ИЛИ 20 и 1 счетчики 2, 14 и 15. Триггер 22 подготавливает к открыванию элемент И 17. Затем по входу 24 в устройство подаются тактовые импульсы от внешнего генератора импульсов на тактовый вход триггера 21 и входы элементов И 18 и 19, на выходах которых формируются две управляющие последовательности сдвинутых во времени импульсов ТИ1 и ТИ2. Импульсы ТИ1 элемента И 18 опрашивают мажоритарный элемент 13 и через элемент И 17 поступают на счетный вход счетчика 14. С датчиков 23 ня входы мультиплексора 10

поступают потенциальные сигналы О или 1 параметров от п идентичных объектов, причем каждый объект содержит группу из m датчиков соответствующих параметров,

например, параметров a, bm. Одноименные параметры идентичны для всех объектов, а поступление сигналов параметров от соответствующих датчиков разнесено во времени, например, при одновременном

0 задействовании п объектов в процессе их функционирования сначала поступают сигналы группы параметров а от объектов, затем сигналы группы Ь и т.д. При этом, в группе идентичных параметров эти сигналы

5 также могут быть разнесены во времени в определенных пределах По мере выполнения функций объектов на соответствующих датчиках 23 устанавливаются единичные потенциальные сигналы, свидетельствую0 щие о норме соответствующего параметра.

В процессе счета счетчик 14 определяет

номера объектов с 1-го по n-й счетчик 15 параметры a, b,.,.,m. Нулевое положение

счетчика 15 соответствует опросу первого

5 из параметров а. Счетчики 14 и 15 через мультиплексор 10 опрашивают датчики 23 в следующей последовательности: счетчик 14 - параметры а объектов с 1-го по n-й затем после заполнения счетчика 14 счетчик

0 15 переключается в первое положение соответствующее опросу параметров Ь объектов с 1-го по n-й и т.д. В процессе переключения счетчиков 14 и 15 в каждом такте мультиплексор 10 подключает выход

5 одного из датчиков 23 к информационному входу блока 9 памяти. В этом же такте сдвинутый импульс ТИ2 с выхода элемента И 19 подается на вход выборки блока 9 памяти и обеспечивает запись значения опрашивае0 мого параметра по адресу, заданному текущим состоянием счетчиков 14 и 15. Режим записц задается сигналом низкого уровня с выхода триггера 16, находящегося в нулевом состоянии, по входу запись-чтение бло5 ка 9 памяти. При опросе последнего параметра последнего объекта, т.е. после заполнения счетчиков 14 и 15, это их состояние декодируется дешифратором 12. Сигнал с выхода дешифратора 12 подается на

0 информационный входтриггера 22 и на вход мажоритарного элемента 13. Импульс ТИ2, обеспечивающий запись значения последнего параметра в данном цикле, с выхода элемента И 19 устанавливает триггер 22 в

5 единичное состояние, закрывая элемент И 17 и запрещая счет импульсов ТИ1 счетчиками 14 и 15. Очередной импульс ТИ1 следующего такта с выхода элемента И 18 открывает мажоритарный элемент 13. Мажоритарный элемент 13 выполняет функцию формирователя одиночного импульса, он открывается при совпадении на его входах двух сигналов из трех, т.е. сигнала дешифратора 12 и импульса ТИ1 и самоблокируется. Импульс с выхода эле- мента 13 устанавливает триггер 16, работающий в счетном режиме в единичное состояние и через элемент ИЛИ 20 обнуляет счетчики 14 и 15. Триггер 16 задает режим чтения сигналом высокого уровня по входу запись-чтение блока 9 памяти. После обнуления счетчиков 14 и 15 снимается сигнал с выхода дешифратора 12 и очередной импульс ТИ2 устанавливает триггер 22 снова в нулевое положение. Триггер 22 открывает элемент И 17 и разрешает подачу счетных импульсов на счетчики 14 и 15. Устройство переходит в режим чтения из блока 9 памяти, при этом импульсы чтения, так же как и записи, задаются последовательностью ТИ2 с выхода элемента И 19, а адреса ячеек памяти - счетчиками 14 и 15, В процессе чтения каждое состояние счетчика 15 параметров объектов декодируется дешифратором 11, сигналы с выходов которого подаются на входы соответствующих разрядов регистра 7. Так как в ячейках блока 9 памяти значения параметров п объектов записаны последовательно по группам (а,

bm), то и считываются они в этой же по-

следовательности. При этом, счетчик 2 подсчитывает число единичных значений параметров в группе, т.е. фактически определяет число объектов, находящихся в норме по каждому из параметров. Например, если задействовано п объектов, и в цикле записи значения параметров ai, азап объектов были 1,то в цикле чтения из соответствующих ячеек блока 9 памяти считывается п 1 и счетчик 2 фиксирует это число, кото- рое подается на первые входы блока 4 сравнения. На другие входы блока 4 сравнения по входам 3 постоянно подается число п задействованных объектов. При равенстве указанных чисел блок 4 выдает сигнал раз- решения записи в регистр 7. При этом в регистре 7 сигналом с дешифратора 11 устанавливается в единичное состояние разряд, соответствующий данному параметру, и свидетельствует о готовности заданного числа объектов по данному параметру. Счетчик 2 в процессе чтения периодически обнуляется через элемент ИЛИ 1 импульсов формирователя 8, который формируется по срезу импульса переноса с выхода старшего разряда счетчика 14. Этим обеспечивается цикличность просмотра ячеек памяти всех объектов по данному текущему параметру, После каждого циклического обнуления счетчик 2 снова готов к подсчету числа единиц по следующему параметру и т.д. После заполнения адресных счетчиков 14, 15, т.е. после считывания всех ячеек памяти дешифратор 12 снова формирует сигнал, который устанавливает в единичное состояние триггер 22, через элемент 13 - триггер 16 в нулевое состояние,обнуляет счетчики 14, 15 и 2 и переводит устройство снова в режим записи и т.д. К концу каждого цикла чтения в регистре 7 в единичное состояние устанавливаются разряды, соответствующие параметрам, по которым все заданное число объектов находится в рабочем состоянии. Сигналы с выходов регистра 7 по выходам устройства выдаются для управления внешним устройством и параллельно поступают в блок 6 индикации. По блоку 6 индикации оператор оценивает готовность заданного числа объектов по каждому из параметров на различных этапах функционирования

этих объектов.

В предложенном устройстве за счет введения мультиплексора, трех счетчиков, двух дешифраторов, трех триггеров, трех элементов И, элемента ИЛИ и мажоритарного элемента обеспечивается формирование суммарных сигналов о состоянии объектов на определенных этапах их функционирования и представление этой обобщенной информации оператору, что улучшает оперативные возможности управления и расширяет область применения устройства.

Ф ормулэ изобретения Устройство для ввода информации от датчиков, содержащее мультиплексор, блок памяти, первый и второй счетчики, блок сравнения, первый, второй и третий триггеры, первый, второй и третий элементы И,- первый элемент ИЛИ, первый дешифратор, информационные входы мультиплексора являются информационными входами устройства, выходы первого счетчика соединены с адресными входами первой группы мультиплексора и блока памяти, выход первого элемента И соединен со счетным входом первого счетчика, первый вход первого элемента И - с выходом второго элемента И, первый вход которого является тактовым входом устройства, выход третьего элемента И соединен с тактовым входом первого триггера, отличающееся тем, что, с целью расширения области применения за счет получения обобщенной информации о состоянии задействованных датчиков, в устройство введены формирователь импульса, третий счетчик, второй элемент ИЛИ, второй дешифратор, регистр, блок индикации, мажоритарный элемент, тактовый вход второго триггера и первый вход третьего

элемента И являются тактовым входом устройства, прямой выход второго триггера соединен с вторым входом второго элемента И, выход которого соединен с первым входом мажоритарного элемента, первым вхо- дом первого элемента ИЛИ и тактовым входом третьего триггера, инверсный выход которого соединен с информационным входом третьего триггера,прямой выход которого соединен с входом чтения-записи блока памяти, выход которого соединен со Счетным входом третьего счетчика, выходы Которого соединены с входами первой группы блока сравнения, входы второй группы Которого являются установочными входами устройства, выход блока сравнения соединен с входом записи регистра, выходы которого подключены к входам блока индикации и являются выходами устройства, выход мультиплексора соединен с информацией- ным входом блока памяти, выход старшего разряда первого счетчика - со счетным входом второго счетчика и входом формирователя импульса, выход которого соединен с первым входом второго элемента ИЛИ, вы-

ход которого соединен с входом сброса третьего счетчика, выходы второго счетчика соединены с адресными входами второй группы мультиплексора и блока памяти и входами первого дешифратора, выходы которого соединены с информационными входами регистра, выходы первого и второго счетчиков - с входами второго дешифратора, выход которого соединен с третьим входом мажоритарного элемента и информационным входом первого триггера, выход которого соединен с вторым входом первого элемента И, инверсный выход второго триггера - с информационным входом второго триггера и вторым входом третьего элемента И, выход которого соединен с входом выборки блока памяти и тактовым входом первого триггера, входы сброса первого, второго и третьего триггеров и регистра и второй вход первого элемента ИЛИ являются входом начальной установки устройства, выход первого элемента ИЛИ соединен с входами сброса первого и второго счетчиков и вторым входом второго элемента ИЛИ.

Е С

с с

ЕС

с Е

I

Авторы

Даты

1991-11-15—Публикация

1990-01-30—Подача