3

Изобретение откосится к вычислительной технике и может быть исполь зовано в составе спе1Ц1ализированных быстродействующих вычиспительных сис тем обработки изображений.

Цель изобретения - повышение быстродействия .

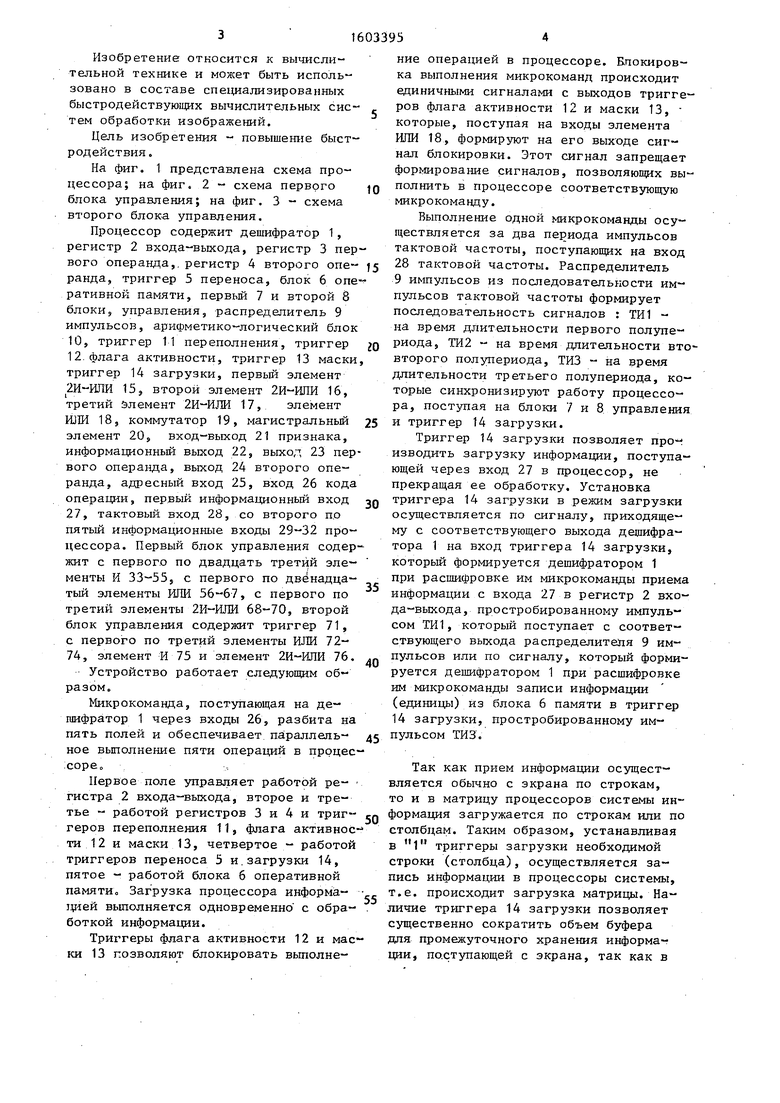

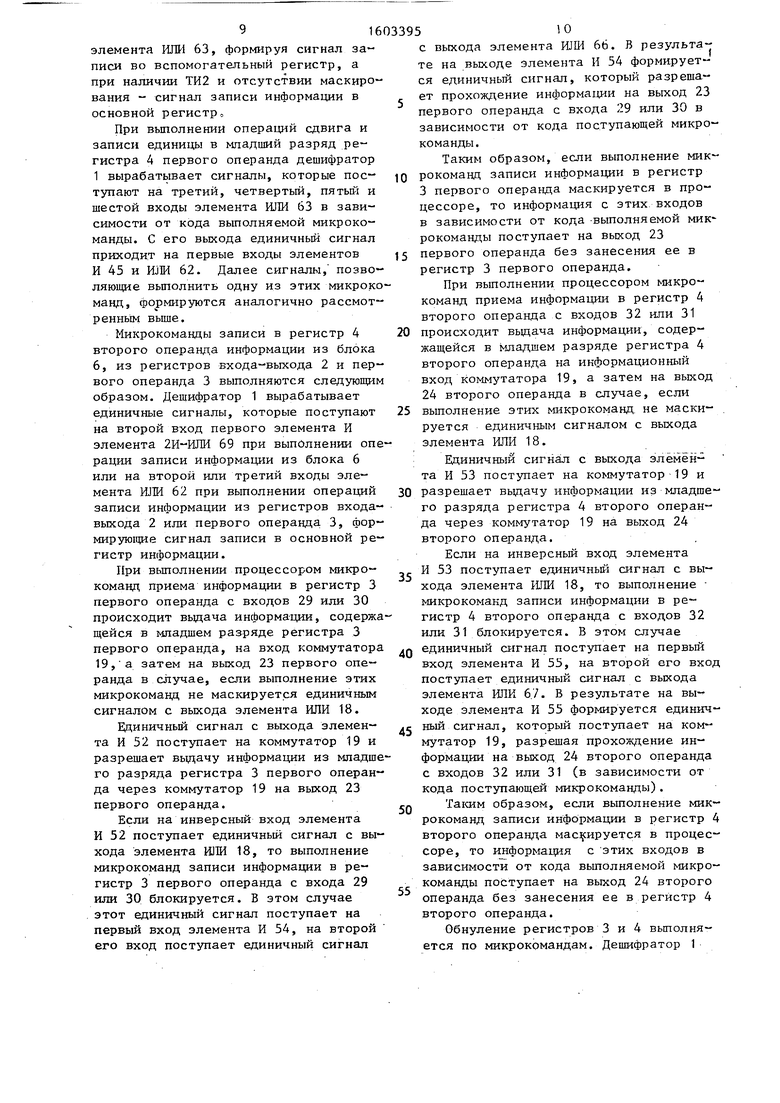

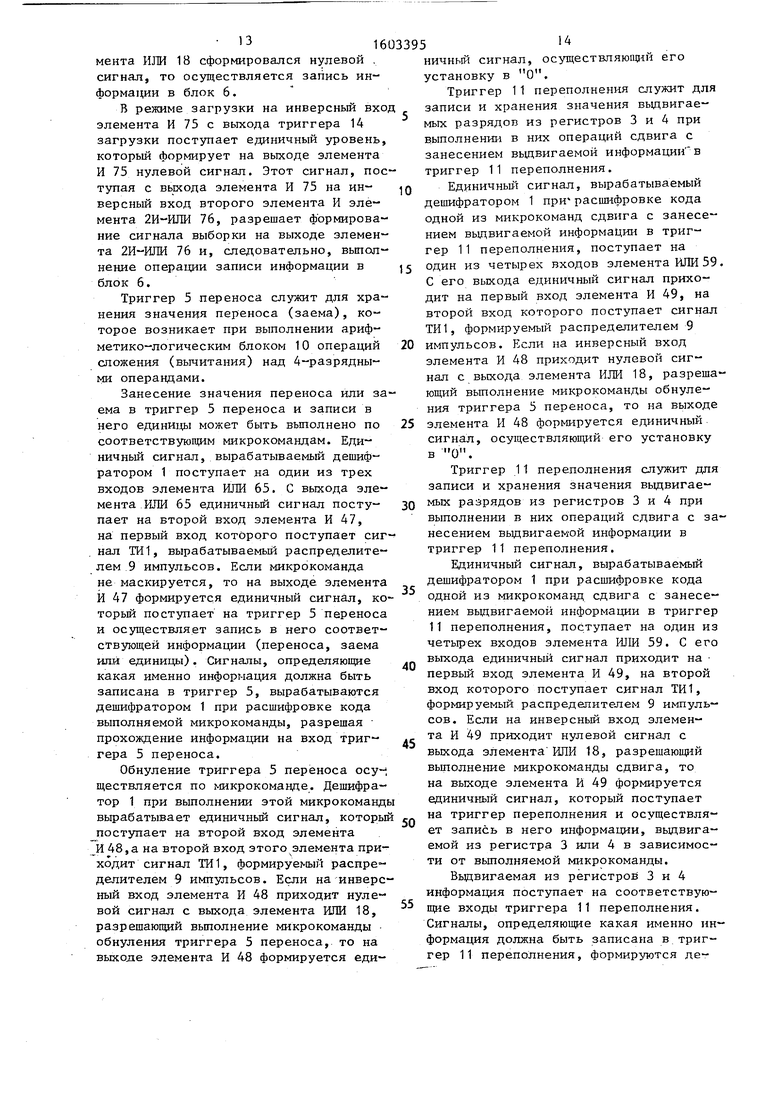

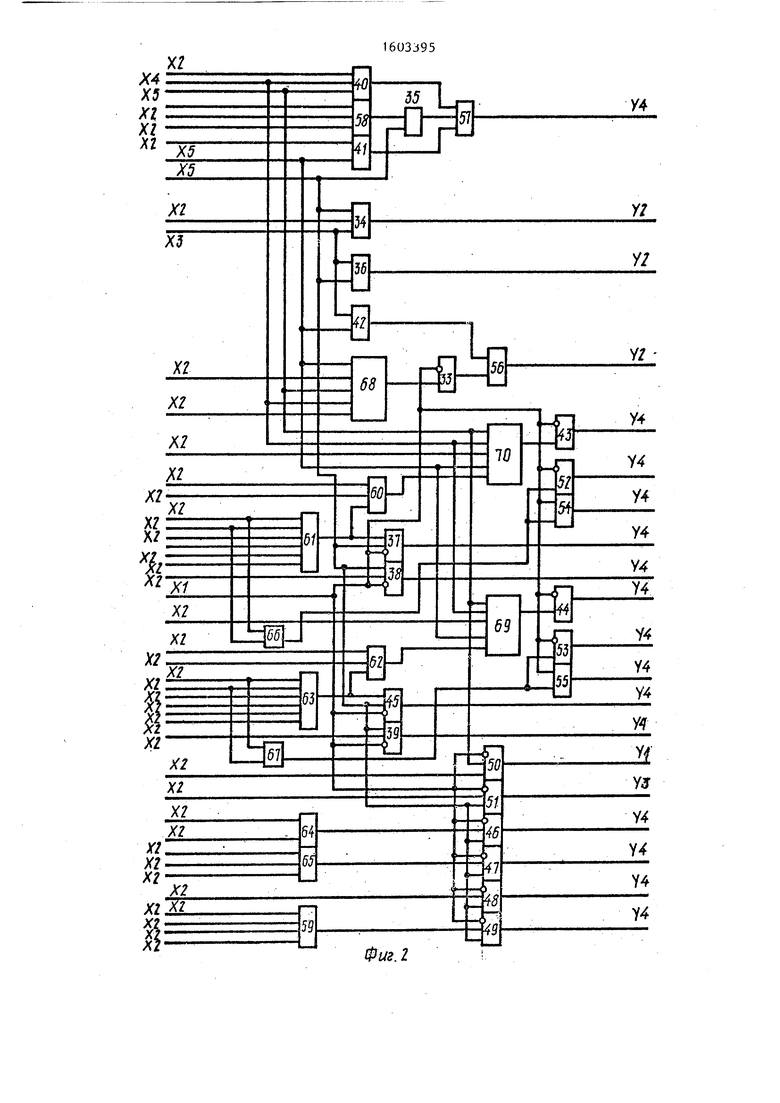

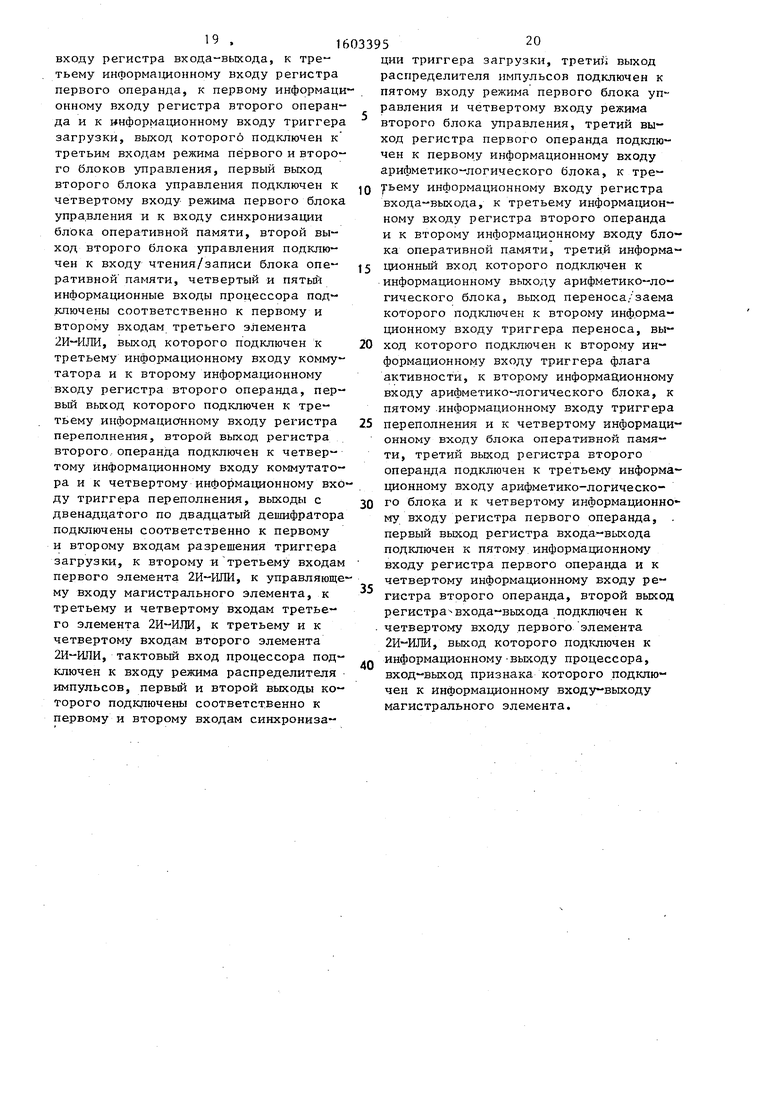

На фиг. 1 представлена схема процессора; на фиг. 2 - схема первого блока управления; на фиг. 3 - схема второго блока управления.

Процессор содержит дешифратор 1, регистр 2 входа-выхода, регистр 3 певого операнда,, регистр 4 второго one ранда, триггер 5 переноса, блок 6 оп ративной памяти, первьй 7 и второй 8 блоки, управления, распределитель 9 импульсов, арифметико-логический бло 10, триггер 11 переполнения, триггер 12. флага активности, триггер 13 маски триггер 14 загрузки, первьй элемент 2И-ИПИ 15J второй элемент 2И-ИПИ 16, третий Элемент 2И-ИЛИ 17, элемент ШШ 18, коммутатор 19, магистральный элемент 20, вход-выход 21 признака, информахщонный выход 22, выход 23 первого операнда, выход 24 второго операнда, адресный вход 25, вход 26 кода операции, первый информационньш вход 27, тактовый вход 28, со второго по пятый информационные входы 29-32 процессора. Первый блок управления содер жит с первого по двадцать третий элементы И 33-55, с первого по двенадцатый элементы ИЛИ 56-67, с первого по третий элементы 2И-ИЛИ 68-70, второй блок управления содержит триггер 71, с первого по третий элементы ИЛИ 72- 74, элемент И 75 и элемент 2И-ИЛИ 76

Устройство работает следующим образом.

Микрокоманда, поступающая на дешифратор 1 через входы 26, разбита на пять полей и обеспечивает па:раллель- ное выполнение пяти операций в пррцес -соре

Первое поле управляет работой ре- гистра 2 входа-выхода, второе и третье - работой регистров 3 и 4 и триггеров переполнения 11, флага активное ти 12 и маски 13, четвертое - работой триггеров переноса 5 и.загрузки 14, пятое - работой блока 6 оперативной памяти Загрузка процессора информа- 1щей выполняется одновременно с обработкой информации.

Триггеры флага активности 12 и маски 13 позволяют блокировать вьшолне

20

|Q

5 5

5

0

5

0

ние операцией в процессоре. Кпокиров- ка выполнения микрокоманд происходит единичными сигналами с выходов триггеров флага активности 12 и маски 13, которые, поступая на входы элемента ИЛИ 18, формируют на его выходе сигнал блокировки. Этот сигнал запрещает формирование сигналов, позволяющих выполнить в процессоре соответствующую микрокоманду.

Выполнение одной микрокоманды осуществляется за два периода импульсов тактовой частоты, поступающих на вход 28 тактовой частоты. Распределитель 9 импульсов из последовательности импульсов тактовой частоты формирует последовательность сигналов : ТИ1 - на время длительности первого полупериода, ТИ2 - на время длительности вто- второго полупериода, ТИЗ - на время длительности третьего полупериода, которые синхронизируют работу процессора, поступая на блоки 7 и 8 управления и триггер 14 загрузки.

Триггер 14 загрузки позволяет про изводить загрузку информации, поступающей через вход 27 в процессор, не прекращая ее обработку. Установка триггера 14 загрузки в режим загрузки осуществляется по сигналу, приходящему с соответствующего выхода дещифра- тора 1 на вход триггера 14 загрузки, который формируется дешифратором 1 при расшифровке им микрокоманды приема информации с входа 27 в регистр 2 входа-выхода, простробированному импульсом ТИ1, который поступает с соответствующего выхода распределителя 9 импульсов или по сигналу, который формируется дешифратором 1 при расшифровке им микрокоманды записи информации (едигшцы) из блока 6 памяти в триггер 14 загрузки, простробированному импульсом ТИЗ .

Так как прием информации осуществляется обычно с экрана по строкам, то и в матрицу процессоров системы ин- формация загружается по строкам или по столбцам. Таким образом, устанавливая в 1 триггеры загрузки необходимой строки (столбца), осуществляется запись информации в процессоры системы, т.е. происходит загрузка матрицы. Наличие триггера 14 загрузки позволяет существенно сократить объем буфера для промежуточного хранения информации, поступающей с экрана, так как в

этом случае необходим 6yi|jep не на весь экран, а только на одну строку.

Сброс режима загрузки осуществляется по микрокоманде записи информации из блока 6 в триггер 14 загрузки в случае, если в триггер 14 записывается ноль.

Регистр 2 входа-выхода служит для преобразования последовательной ин- формадии, поступающей через вход 27, в параллельную и передачи ее на вькод 22. Регистр 2 входа-выхода осуществляет прием входной информации, прием информации с регистра 3 первого операнда, прием информации из блока 6.

Прием последовательной информации, поступающей через вход 27 в регистр 2 входа-выхода, осуществляется по соответствующей микрокоманде. По этой микрокоманде дешифратор 1 вырабатывает сигнал, устанавливающий триггер 14 загрузки в режим загрузки. Единичный сигнал с выхода триггера 14 загрузки поступает на второй вход элемента И 36 и на первый вход элемента И 42. На первый вход элемента И 36 поступает сигнал ТИ1, а на второй вход элемента И 42 - сигнал ТИ2, который вьфабатывается распределителем 9 импульсов. С выхода элемента И 42 сигнал поступает на один из входов элемента ИЛИ 56. В результате этого на выходах элементов И 36 и ИЛИ 56 формируются импульсы, которые поступают на регистр 2 входа-выхода и осуществляют запись в него информации, приходящей с входа 27. ;

Во время выполнения микрокоманды приема входной информации в регистр 2 входа-выхода осуществляется выдача информации, содержащейся в младшем разряде этого регистра, с его в ыхода на третий вход элемента 2И-ИЛИ 15. На первый вход элемента 2И-ИПИ 15 поступает единичный сигнал с соответствующего выхода дешифратора 1, который показывает, что вьшолняется микрокоманда приема входной информации, и разрещает прохождение содержимого мпадшего разряда регистра 2 входа-выхода через элемент 2И-ИПИ 15 на вькод 22 процессора.

В процессоре предусмотрена микрокоманда, которая позволяет осуществлять передачу информации, поступающей через вход 27 на выход 22, минуя регистр 2 входа-выхода. Во время ее выполнения информация с входа 27

.

i

603395

поступает на второй вход элемента 2И-1 1Ш 1 15, а на четвертый его вход поступает единичный сигнал соответствующего выхода дешифратора 1 и разрешает прохождение информации с выхода элемента 2И-ШЫ 15 на выход 22 процессора.

Вьшолнение микрокоманд обнуления содержимого регистра 2 входа-выхода осуществляется только в режиме загрузки. С выхода триггера 14 загрузки единичный сигнал проходит на третий вход элемента И 34. На два других входа этого элемента поступают сигнал с де-

10

15

20

25

30

35

40

45

50

55

шифратора 1 , показываюш й, что выполняется микрокоманда обнуления регистра 2 входа-выхода и сигнал ТИ1 с распределителя 9 импульсов. На выходе элемента И 34 формируется сигнал, который, поступая на регистр 2 входа-выхода, осуществляет его обнуление.

Запись информации, содержащейся в регистре 3 первого опера ща или в блоке 6, в регистр 2 входа-выхода происходит при выполнении процессором соот- ветствую1цих микрокоманд. Дешифратор 1 расшифровывает код одной из этих макрокоманд и вырабатывает единичньй сигнал, поступающий на второй вход второго элемента И элемента 2И-ИШ{ 68 элемента при осуществлении переписи информации в регистр 2 входа-выхода из регистра 3 первого операнда, или единичньй сигнал, поступающий на второй вход первого элемента И элемента 2И-ИЛИ 68 при осуществлении записи информации в регистр 2 входа-выхода из блока 6. На первые входы первого и второго элементов И элемента 2И-ИЛИ 68 поступают стробирующ е импульсы ТИЗ и ТИ2 соответственно, вырабатываемые распределителем 9 импульсов, а на третий вход первого элемента И элемента 2И-ШШ 68 поступает единичный -сигнал выборки с выхода элемента 2И-ИЛИ 76. Сформировавшиеся единичные сигналы с выхода элемента 2И-ИЛИ 68 поступают на вход элемента И- 33. Если на его инверсном входе находится нулевой уровень (выполнение этих микрокоманд не замаскировано), то с выхода элемента И 33 единичный сигнал поступает на второй вход элемента ИЛИ 56, ас его выхода - регистр 2 входа-выхода, осуществляя запись с него информации. Регистр 3 первого операнда служит для преобразования последовательной информации, поступающей через входы

29, 30 или через вход-выход 21, в параллельную и передачи ее на выход 23 первого операнда или на вход-выход 21

По соответствующим микрокомандам в регистре 3 первого операнда может быть выполнен сдвиг его содержимого вправо (в сторону младших разрядов) или влево (в сторону старших разрядов с занесением содержимого вьщвигаемого разряда в триггер 11 переполнения, а также может быть записана единица в младший разряд регистра 3 первого операнда.

Прием информации в регистр 3 пер- вого операнда с входов 29 и 30 и входа-выхода 21 осуществляется по микрокоманд аме

Информация с входов 29 и 30 поступает на второй и третий входы элемента 2И-ИЛИ 16. На первый и четвертый входы этого элемента поступают единичные сигналы с соответствующих выха дов дешифратора 1, которые показывают Что выполняется одна из микрокоманд приема информации в регистр 3 первого операнда с входов 29 и 30 и разрешают прохождение информации с одного из этих входов через элемент 2И-ШШ 16 на вход регистра 3 первого операнда.

При выполнении микрокоманды записи информации, поступающей через вход- выход 21 на магистральный элемент 20, в регистр 3 первого операнда дешифратор 1 вырабатывает единичньй сигнал, который разрешает прохождение информации с его выхода на вход регистра 3 первого операнда.

Запись информации в регистр 3 первого операнда вьтолняется в два этапа Сначала по импульсу ТИ1 с распределителя 9 импульсов, информация записывается во вспомогательный регистр, а затем по импульсу ТИ2 с распределителя 9 импульсов - в основной. Единич- ный сигнал с дешифратора 1, определяющий, что выполняется одна из этих микрокоманд, поступает на первый, второй или четвертый вход элемента ИЛИ 61, формируя при наличии импульса ТИ1 и отсутствии маскирования через элемент И 3/ сигнал записи во вспомогательный регистр, а при наличии сигнала ТИ2 и отсутствии маскирования через элементы ИЛИ 60, 2И-ИЛИ 70 и И 43 - сигнал записи информации в основной регистр 3 первого операнда.

При вьшолнении операхщй сдвига и записи единицы в младший разряд ре

Q 5

0 5 0

5

о 5 .

5

гистра 3 первого операнда дешифратор

1вырабатывает единичные сигналы, которые поступают на третий, пятый и шестой входы элемента ИЛИ 61 в зависимости от кода выполняемой микрокоманды. С е го выхода единичньй сигнал приходит на третий вход элемента

ИЛИ 60 и на второй вход элемента И 37. Далее сигналы, позволяющие выполнить с одну из этих микрокоманд, формируются аналогично рассмотренным вьш1е.

Микрокоманды записи в регистр 3 пер- первого операнда информации из блока 6, из регистров 2 - и 4 выполняются следующим образом. Дешифратор 1 выра-. батывает единичные сигналы, которые поступают на второй вход первого элемента И элемента 2И-ИЛИ 70 при выполнении операции записи информации из блока 6 или.на первый или второй входы элемента ИЛИ 60 при выполнении операций записи информации из регистров

2или 4 соответственно в регистр 3 первого операнда.

Регистр 4 второго операнда служит для преобразования последовательной информации, поступающей через входы 32 или 31, в параллельную и передачи ее на вход 24 второго операнда. Регистр 4 второго операнд а осуществляет приём информации, поступающей через входы 32 или 31, прием информации с регистров 2 и 3 и прием информации из блока 6.

По соответствующим микрокомандам в регистре 4 второго операнда может быть выполнен сдвиг его содержимого вправо (в сторону младших разрядов) или влево (в сторону старших разрядов) с занесением (без занесения) содержимого выдвигаемого разряда в триггер 11 переполнения, а также может быть записана единица в младший разряд регистра 4 второго операнда.

Информация с входов 32 и 31 поступает на второй и третий входы элемента 2И-И11И 17. На первый и четвер-. тый входы этого элемента поступают единичные сигналы с соответствуюпдах выходов дешифратора 1, которые показывают, что выполняется одна из микрокоманд приема информации в регистр 4 второго операнда с входов 32, 31, и разрешают прохождение информации с одного из ;этих входов на вхор регистра 4 второго операнда.

Единичный сигнал с дешифратора 1 поступает на первый или второй входы

элемента ИЛИ 63, формируя сигнал записи во вспомогательный регистр, а при наличии ТИ2 и отсутствии маскиро вания - сигнал записи информации в основной регистр.

При выполнении операций сдвига и записи единицы в мпадший разряд регистра 4 первого операнда дешифратор 1 вырабатывает сигналы, которые поступают на третий, четвертый, пятый и шестой входы элемента ИЛИ 63 в зависимости от кода выполняемой микрокоманды. С его выхода единичньш сигнал приходит на первые входы элементов И 45 и ШШ 62. Далее сигналы, позволяющие выполнить одну из этих микрокоманд, формируются аналогично рассмот- ренньгм вьше.

Микрокоманды записи в регистр 4 второго операнда информации из блока 6, из регистров входа-выхода 2 и первого операнда 3 выполняются следующим образом. Дешифратор 1 вырабатывает единичные сигналы, которые поступают на второй вход первого элемента И элемента 2И-ШШ 69 при выполнении операции записи информации из блока 6 или на второй или третий входы элемента ШШ 62 при выполнении операций записи информации из регистров входа- выхода 2 или первого операнда 3, формирующие сигнал записи в основной регистр информации.

При вьшолнении процессором микрокоманд приема информации в регистр 3 первого операнда с входов 29 или 30 происходит вьщача информации, содержащейся в младшем разряде регистра 3 первого операнда, на вход коммутатора 19, а затем на выход 23 первого операнда в случае, если выполнение этих микрокоманд не маскируется единичным сигналом с выхода элемента ИЛИ 18.

Единичный сигнал с выхода элемента И 52 поступает на коммутатор 19 и разрешает выдачу информации из младшего разряда регистра 3 первого операнда через коммутатор 19 на выход 23 первого операнда.

Если на инверсный вход элемента И 52 поступает единичный сигнал с выхода элемента И1Ш 18, то выполнение микрокоманд записи информации в регистр 3 первого операнда с входа 29 или 30 блокируется. В этом случае этот единичный сигнал поступает на первый вход элемента И 54, на второй его вход поступает единичный сигнал

5

0

с выхода элемента ШШ 66. В результате на выходе элемента И 54 формируется единичный сигнал, который разрешает прохождение информахщи на выход 23 первого операнда с входа 29 или 30 в зависимости от кода поступающей микрокоманды.

Таким образом, если выполнение микрокоманд записи информации в регистр 3 первого операнда маскируется в процессоре, то информация с этих входов в зависимости от кода -выполняемой мик рокоманды поступает на выход 23 первого операнда без занесения ее в регистр 3 первого операнда.

При выполнении процессором микрокоманд приема информации в регистр 4 второго операнда с входов 32 или 31 происходит выдача информации, содержащейся в младшем разряде регистра 4 второго операнда на информационный вход коммутатора 19, а затем на выход 24 второго операнда в случае, если

вьшолнение этих микрокоманд не маски- . руется единичным сигналом с выхода элемента ИЛИ 18.

Единичный сигнал с выхода элемента И 53 поступает на коммутатор19 и разрешает выдачу информации из младшего разряда регистра 4 второго операнда через коммутатор 19 на выход 24 второго операнда.

Если на инверсньш вход элемента И 53 поступает единичньй сигнал с выхода элемента ИЛИ 18, то выполнение микрокоманд записи информации в регистр 4 второго операнда с входов 32 или 31 блокируется. В этом случае единичный сигнал поступает на первый вход элемента И 55, на второй его вход поступает единичный сигнал с выхода элемента ИЛИ 6.7. В результате на выходе элемента И 55 формируется единичный сигнал, который поступает на коммутатор 19, разрешая прохождение информации на выход 24 второго операнда с входов 32 или 31 (в зависимости от кода поступающей микрокоманды).

Таютм образом, если выполнение микрокоманд записи информации в регистр 4 второго операнда маскируется в процессоре, то информация с этих входов в зависимости от кода выполняемой микрокоманды поступает на выход 24 второго операнда без занесения ее в регистр 4 второго операнда.

Обнуление регистров 3 и 4 выполняется по микрокомандам. Дешифратор 1

10

111603395

при расгаифровке кодов.этих микрокоманд вырабатывает единичные сигналы, которые .поступают на вторые входы элементов И 38 при обнулении регистров 3 первого операнда и И 39 при обнулении регистра 4 второго операнда. На первые входы этих элементов поступают импуль сы ТИ1, вырабатываемые распределите -: лем 9 импульсов. Если на инверсные входы элементов И 38 и 39 поступает нулевой сигнал с выхода элемента ИЛИ 18, то на выходах элементов И 38 и 39 формируются единичные сигналы, которые постзшают на регистры 3 и 4 и производят обнуление этих регистров

Арифметико-логический блок 10 выполняет следуюнще операции над 4-разрядными операндами: логическое сложение, логическое умножение, сложение, вычитание, суммирование по mod 2, инверсия. Выполнение этих опера1щй над 4-разрядными операндами, поступающими на арифметико-логический блок 10, осуществляется в нем постоянно, а резуль-25 нал с триггера 71, длительность кото- тат вьшолнения одной из этих операций рого определяется интервалом между пе- записьшается в блок 6 только при нали- редними фронтами импупьсов ТИ2 и ТИ1 чин соответствующей микрокомандыо вырабатываемыми распределителем 9 имБлок 6 оперативной памяти предназначен для хранения информации, посту- зс пающей с регистров 2 и 3

При выполнении одной из микрокоманд чтения информа1щи из блока 6 дешифратор 1 в зависимости от кода микрокоманды вырабатывает сигнал, который поступает на один из пяти входов элемента ИЛИ 73. С его выхода этот сигнал поступает на вход элемента ИЛИ 72, а с его выхода единичным сигналом - на соответствующий вход блока 6.

Элемент 2И-ИЛИ 76 формирует сигнал выборки, который разрешает обращение к блоку 6 при выполнении микрокоманд 15 записи или чтения информации в (из) блок 6. На первые входы первого и второго элементов И элемента 2И-ИЛИ 72 поступают единичные сигналы с выходов элементов ИЛИ 73 и 74 соответственно, определяю1цие, что выполняется одна из микрокоманд чтения .или записи информации из (в) блока 6. На вторые входы первого и второго элементов И элемента 2И-ИЛИ 76 поступает единичный сиг20

с регистров 2 и 3 и с арифметико-логического блока 10, а также содержимого триггеров 5 и 14. Передача информада1и из блока 6 может происходить во все регистры процессора и триггеры 13 и 14 по соответствую1Щ1м микрокомандам.

В процессоре вьшолняются семь микрокоманд записи информации в блок 6 оперативной памяти: результат логического сложения, результат суммирования по mod 2, результат логического умножения, результат суммы (раз- ности) и пять микрокоманд чтения информации из блока 6: в регистр 2 входа-выхода, в регистр) 3 первого операнда, в регистр 4 второго операнда, в триггер 13 маски и триггер 14 загрузки.

При выполнении одной из микрокоманд записи информации в блок 6 дешифратор 1 в зависимости от кода микрокоманды вырабатывает единичньш сигнал, который поступает на один из восьми входов элемента ЮШ 74 С его выхода этот сигнал поступает на ин- версньй вход элемента ИЛИ 72, а с его выхода, нулевым сигналом на соответст- .вующий вход блока 6,

35

пупьсов и поступающими на S- и R-входы триггера соответственно. На инверсный вход первого элемента и эле- элемента 2И-ИЛИ 76 поступает сигнал с выхода элемента И1Ш 18. Если он нуле-, вой, формируется единичный сигнал выборки, поступающий на соответствующий вход блока 6, и, следовательно, вы45

полняется операция чтения информации из блока 6. Если на выходе элемента ИЛИ 18 сформировался единичный сигнал,

д то он, приходя на инверсный вход первого элемента И элемента 2И-ИЛИ 76, запрещает формирование сигнала выборки и чтение информа1щи из блока 6 не происходит.

Сигнал с выхода элемента ИЛИ 18 приходит также на первый вход элемента И 75, на инверсньй его вход приходит сигнал с выхода триггера 14 загрузки. Если на выходе триггера 14

5Q загрузки сформировался нулевой уровень (нет режима-загрузки), то единичный сигнал с выхода элемента ИЛИ 18 проходит на выход элемента И 75 и на инверсный вход второго элемента И эле- мента 2И-ИЛИ 76, запретив тем самым формирование сигнала выборки на выхо да элемента 2И-ИЛИ 76 и, следовательно, вьшолнение операций записи информации в блок 6. Если на выхоо эле0

5 нал с триггера 71, длительность кото- рого определяется интервалом между пе- редними фронтами импупьсов ТИ2 и ТИ1 вырабатываемыми распределителем 9 имПри выполнении одной из микрокоманд чтения информа1щи из блока 6 дешифратор 1 в зависимости от кода микрокоманды вырабатывает сигнал, который поступает на один из пяти входов элемента ИЛИ 73. С его выхода этот сигнал поступает на вход элемента ИЛИ 72, а с его выхода единичным сигналом - на соответствующий вход блока 6.

Элемент 2И-ИЛИ 76 формирует сигнал выборки, который разрешает обращение к блоку 6 при выполнении микрокоманд 5 записи или чтения информации в (из) блок 6. На первые входы первого и второго элементов И элемента 2И-ИЛИ 72 поступают единичные сигналы с выходов элементов ИЛИ 73 и 74 соответственно, определяю1цие, что выполняется одна из микрокоманд чтения .или записи информации из (в) блока 6. На вторые входы первого и второго элементов И элемента 2И-ИЛИ 76 поступает единичный сиг0

с

5

пупьсов и поступающими на S- и R-входы триггера соответственно. На инверсный вход первого элемента и эле- элемента 2И-ИЛИ 76 поступает сигнал с выхода элемента И1Ш 18. Если он нуле-, вой, формируется единичный сигнал выборки, поступающий на соответствующий вход блока 6, и, следовательно, вы5

полняется операция чтения информации из блока 6. Если на выходе элемента ИЛИ 18 сформировался единичный сигнал,

то он, приходя на инверсный вход первого элемента И элемента 2И-ИЛИ 76, запрещает формирование сигнала выборки и чтение информа1щи из блока 6 не происходит.

Сигнал с выхода элемента ИЛИ 18 приходит также на первый вход элемента И 75, на инверсньй его вход приходит сигнал с выхода триггера 14 загрузки. Если на выходе триггера 14

Q загрузки сформировался нулевой уровень (нет режима-загрузки), то единичный сигнал с выхода элемента ИЛИ 18 проходит на выход элемента И 75 и на инверсный вход второго элемента И эле- мента 2И-ИЛИ 76, запретив тем самым формирование сигнала выборки на выхо да элемента 2И-ИЛИ 76 и, следовательно, вьшолнение операций записи информации в блок 6. Если на выхоо эле10

20

25

мента ИЛИ 18 сформировался нулевой , сигнал, то осуществляется запись информации в блок 6.

В режиме загрузки на инверсный вход элемента И 75 с вьпсода триггера 14 загрузки поступает единичный уровень, который формирует на выходе элемента И 75 нулевой сигнал. Этот сигнал, пос тупая с вькода элемента И 75 на инверсный вход второго элемента И элемента 2И-ИЛИ 76, разрешает формирование сигнала выборки на выходе элемента 2И-ИЛИ 76 и, следовательно, выполнение операции записи информации в блок 6.

Триггер 5 переноса служит для хранения значения переноса (заема), которое возникает при выполнении арифметико-логическим блоком 10 операций сложения (вычитания) над 4-разрядны- ми операндами.

Занесение значения переноса или заема в триггер 5 переноса и записи в него единшд, может быть вьшолнено по соответствующим микрокомандам. Еди- ничньш сигнал, вырабатываемый дешифратором 1 поступает на один из трех входов элемента ИЛИ 65. С выхода элемента ИЛИ 65 единичньш сигнал поступает на второй вход элемента И 47, на первый вход которого поступает сигнал ТИ1, вырабатываемый распределителем 9 импульсов. Если микрокоманда не маскируется, то на выходе элемента И 47 формируется единичный сигнал, ко- торьй постзшает на триггер 5 переноса и осуществляет запись в него соответствующей информации (переноса, заема или единицы). Сигналы, определяющие какая именно информация должна быть записана в триггер 5, вырабатываются дешифратором 1 при расшифровке кода выполняемой микрокоманды, разрешая прохождение информации на вход триггера 5 переноса.

Обнуление триггера 5 переноса осу- ществляется по микрокоманде. Дешифратор 1 при выполнении этой микрокоманды вырабатывает единичньш сигнал, который гл поступает на второй вход элемента И 48,а на второй вход этого элемента приходит сигнал ТИ1, формируемый распределителем 9 импульсов. Если на инверсный вход элемента И 48 приходит нулевой сигнал с выхода элемента ИЛИ 18, разрешающий выполнение микрокоманды

нич уст

зап мых вып зан три

деш одн ние гер 15 оди С е дит вто ТИ имп эле нал ющи ния эл

30

35

40

45

55

си в

за мы вы не тр

де од ни 11 че вы пе вх фо со та вых вы на ед

ет ем ти

инф щи Си фор гер

обнуления триггера 5 переноса, то на выходе элемента И 48 формируется еди

0

5

л

ничный сигнал, осуществляюпщи его установку в О.

Триггер 11 переполнения служит для записи и хранения значения выдвигаемых разрядов из регистров 3 и 4 при выполнении в них операций сдвига с занесением выдвигаемой информации в триггер 11 переполнения.

Единичный сигнал, вырабатываемый дешифратором 1 при расшифровке кода одной из микрокоманд сдвига с занесением выдвигаемой информации в триггер 11 переполнения, поступает на 5 один из четырех входов элемента ИЛИ 59. С его выхода единичный сигнал приходит на первый вход элемента И 49, на второй вход которого поступает сигнал ТИ1, формируемый распределителем 9 импульсов. Если на инверсный вход элемента И 48 приходит нулевой сигнал с выхода элемента ИЛИ 18, разрешающий вьшолнение микрокоманды обнуления триггера 5 переноса, то на выходе элемента И 48 формируется единичный осуществляющий его установку

0

5

0

5

5

сигнал, в О.

Триггер 11 переполнения служит дпя записи и хранения значения выдвигаемых разрядов из регистров 3 и 4 при выполнении в них операций сдвига с занесением вьщвигаемой информан;ии в триггер 11 переполнения.

Единичный сигнал, вырабатываемый дешифратором 1 при расшифровке кода одной из микрокоманд сдвига с занесением вьщвигаемой информации в триггер 11 переполнения, поступает на один из четырех входов элемента ШШ 59. С его выхода единичный сигнал приходит на первый вход элемента И 49, на второй вход которого поступает сигнал ТИ1, формируемый распределителем 9 импульсов. Если на инверсньш вход элемента И 49 приходит нулевой сигнал с выхода элемента ИЛИ 18, разрешающий выполнение микрокоманды сдвига, то на выходе элемента И 49 формируется единичный сигнал, который поступает

триггер переполнения и осуществляет запись в него информации, выдвигаемой из регистра 3 или 4 в зависимости от вьшолняемой микрокоманды.

Вьдвигаемая из регистров 3 и 4 информация поступает на соответствующие входы триггера 11 переполнения. Сигналы, определяюшие какая именно информация должна быть записана в триггер 11 переполнения, формируются де

15 16

шифратором 1 и определяются кодом выполняемой микрокоманды.

По соответствующей микрокоманде в; 1полняется перезапись информации, со держащейгся в триггере 5 переноса в триг гер 11 переполнения. При выполнении этой микрокоманды дешифратор 1 формирует единичный сигнал, который поступает на первый вход элемента И 50, на второй его вход приходит сигнал ТИЗ, формируемый распределителем 9 импульсов. Если на инверсный вход элемента И 50 приходит нулевой сигнал с выхода элемента ШШ 18, разрешающий выполне- ние микрокоманды, то на выходе элемента И 50 формируется единичный сигнал, который осуществляет запись триггера 11 переполнения информации с выхда триггера 5 переноса.

Если на выходе одного из триггеров 12 и 13 будет единичный сигнал, то этот сигнал блокирует выполнение микрокоманд.

Обработка информации в матрице, построенной на основе процессоров происходит параллельно. При реализации конкретных алгоритмов не все процессоры должны выполнять поступающие на них микрокоманды. Для реализации используется триггер 13 маски. Если он установлен в единичное состояние, то выполнение микрокоманд процессором блокируется,

При использовании матрицы процессоров в качестве ассоциативной памяти необходим триггер 12 флага активности который позволяет по какому-то ключу ипи признаку устанавливать процессоры в активное или пассивное состояние. По соответствующим микрокомандам в триггер 12 флага активности записывается либо содержимое триггера 5 переноса, либо единица, либо информация поступающая через вход 27,

При выполнении в процессоре микрокоманды записи единицы в триггер 12 флага активности дешифратор 1 вырабатывает единичный сигнал, поступающий на второй вход элемента И 51, На первый вход этого элемента поступает импульс ТИ1, формируемьш распределителем 9 импульсов. Если на инверсном входе элемента И 51 находится нулевой сигнал, то на выходе элемента И 51 формируется единичньй сигнал, которьй приходит на соответствующий вход триггера 12 флага активности и осуществляет запись единицы в триггер 12 флага активности.

10

25

.с 20

30

35

40

45

0

5

Запись информации в триггер 12 фла га активности с входа 27 или из триггера 5 переноса осуществляется при соответствующей микрокоманде. Единичный .сигнал, вырабатываемый дешифратором 1, поступает на один из входов элемента ИЛИ 64, с выхода которого он приходит на второй вход элемента И 46, на первый вход этого элемента поступает импульс ТИ1, формируемый распределителем 9 импульсов. Если на инверс- ньш вход элемента И 46 постзт1ает нулевой сигнал с выхода элемента ИЛИ 18, разрешаю1ций выполнение этих микроко- манд, то на выходе эпемента И 46 вырабатывается единичньй сигнал, разрешающий выполнение микрокоманды записи информации в триггер 12 флага активности с входа 2/ или из триггера 5 переноса.

Выполнение микрокоманды зайиси информации в триггер 13 маски из блока 6 происходит следующим образом. Дешифратор 1 вырабатывает единичный сигнал, поступающий на первый вход элемента И 40, на второй вход которого поступает импульс ТИЗ, формируемый распределителем 9 импульсов, а на третий его вход поступает единичный сигнал выборки, который формируется на выходе элемента 2И-ИПИ 76. В результате на выходе элемента И 40 формируется единичный сигнал, которьй .поступает на первый вход элемента ИЛИ 57. а с его выхода - на вход триггера 13 маски, осуществляя запись ин- форма1щи в него из блока 6,

Запись содержимого триггера 11 переполнения в триггер 13 маски происходит по микрокоманде, ,во время которой дешифратор 1 вырабатьшает единичный сигнал, который поступает на первый вход элемента И 41, на второй вход этого элемента поступает сигнал ТИ2, формируемьй распределителем 9 импульсов, С выхода элемента И 41 единичный сигнал приходит на третий вход элемента ИЛИ 57, с выхода которого он поступает на вход триггера 13 маски, осухцествляя Запись в него информации из триггера 11 переполнения. При вьшолнении в процессоре микрокоманд записи в триггер 13 маски дешифратор 1 вьфабатывает единичные сигналы, поступающие на один из трех входов элементов ИЖ 58 в зависимости от вьшолняемой микрокоманды, С выхода элемента ШШ 58 единичньй сигнал приходит на второй вход элемента И 35,

на первый вход которого поступает им пульс ТИ1, вырабатываемый распределителем 9 импульсов. С выхода элемента И 35 единичный импульс поступает на второй вход элемента ИЛИ 57, с выхода которого он поступает на вход триггера 13 маски, осуществляя в нем выполнение рассматриваемых микрокоманд.

Вьщача информации на вход-выход 21 происходит с первого выхода регистра 3 первого операнда по соответствующей микрокоманде. Информация с первого выхода регистра 3 первого операнда поступает на информационный вход магистрального элемента 20. На его управляющий вход поступает единичньш сигнал, который разрешает прохождение информации с выхода регистра 3 первого операнда на вход-выход 21.

Формула изобретения

Процессор матричной вычислительной системы, содержащий регистр входа-выхода, регистр первого операнда, регистр второго операнда, блок оперативной памяти, триггер переноса и дешифратор, причем вход кода операции процессора подключен к входу дешифратора, вход режима процессора подключен к адресному входу блока памяти, первый информационный вход процессора подключен к первому информационному входу регистра входа-выхода, первый,второй и третий выходы дешифратора подключены соответственно к входам синхронизации регистра входа-, выхода, регистра первого операнда и регистра второго операнда, отличающийся тем, что, с целью

повышения быстродействия, он содержит распределитель импульсов, с первого п третий элементы 2И-ИЛИ, первый и второй блоки управления, триггер загрузки, триггер переполнения, триггер переноса, триггер флага активности, триггер маски, элемент VJM, магистральный элемент, коммутатор и арифметико-логический блок, причем первый информационный вход процессора подключен к первому входу первого элемента 2И-ИЛИ, к первому информационному входу триггера флага и к первому. форма1ционному входу триггера маски, прямой выход которого подключен к первому входу элемента ИЛИ, выход кото-, рого подключен. к первым входам режима: первого и второго блоков управления.

0

5

0

5

0

5

0

5

0

с первого по четырнадцатый выходы первого блока управления подключены соответственно к первому информационному входу триггера переноса, к входу записи / считывания и к входу установки в О регистра входа-выхода, к входу установки в 1 триггера флаги активности, к входу записи / считывания и к входу установки в О регистра первого операнда, к входу записи-считывания и к входу установки в О регистра второго операнда, к входу синхронизации и входу установки в О триггера переполнения, к входу синхронизации и к входу установки в О триггера маски, к входу записи триггера флага активности и к управляющему входу коммутатора, первый и второй выходы которого подключены соответственно к выходам первого и второго операндов процессора, с четвертого по одиннадцатый выходы дешифратора подключены соответственно к второму входу режима первого блока управления, к второму входу режима второго блока управления, к входу кода операции арифметико-логического блока, к BIXO- ду разрешения триггера переполнения, к входу разрешения триггера маски, к входу синхронизации и к входу установки в О триггера переноса и к входу синхронизации триггера флага активности, выход которого подключен к второму входу элемента ИЛИ, второй и третий информационные входы процессора подключены соответственно к первому и второму входам второго элемента 2И-ШШ, выход которого подключен к первому информационному входу коммутатора и первому информационному входу регистра первого операнда, первый выход которого подключен к первому информационному входу триггера .переполнения, к второму информационному входу коммутатора и к информационному входу магистрального элемента, вьрсод которого подключен -к второму инфор- мационному входу регистра первого операнда, второй вход которого подключен к второму информационному входу триггера цереполнен ия, выход которого подключен к второму информационному входу триггера маски и к первому : информационному входу блока оперативной памяти, выходы с первого по пятый которого подключены соответственно к третьему информационному входу триггера маски., к второму информационному

входу регистра входа-выхода, к тре тьему информа14ионному входу регистра первого операнда, к первому информационному входу регистра второго операнда и к информационному входу триггера загрузки, выход которого подключен к третьим входам режима первого и второго блоков управления, первый выход второго блока управления подключен к четвертому входу режима первого блока управления и к входу синхронизации блока оперативной памяти, второй выход второго блока управления подключен к входу чтения/записи блока оперативной памяти, четвертый и пятьш информационные входы процессора под- .ключены соответственно к первому и второму входам третьего элемента 2И-ИЛИ, выход которого подключен к третьему информационному входу коммутатора и к второму информационному входу регистра второго операнда, первый выход которого подключен к третьему информацио нному входу регистра переполнения, второй выход регистра второго операнда подключен к четвертому информационному входу коммутатора и к четвертому информационному входу триггера переполнения, выходы с двенадцатого по двадцатый дешифратора подключены соответственно к первому и второму входам разрешения триггера загрузки, к второму и третьему входам первого элемента 2И-ИЛИ, к управляюш;е му входу магистрального элемента, к третьему и четвертому входам третьего элемента 2И-ИЛИ, к третьему и к четвертому входам второго элемента 2И-ИЛИ, тактовый вход процессора подключен к входу режима распределителя импульсов, первый и второй выходы которого подключены соответственно к первому и второму входам синхрониза

5

0

5

0

5

0

ции триггера загрузки, третий выход распределителя импульсов подключен к пятому ВХОДУ режима первого блока равления и четвертому входу режима второго блока управления, третий выход регистра первого операнда подключен к первому информационному входу арифметико-логического блока, к тре- ьему информационному входу регистра входа-выхода, к третьему информатщон- ному входу регистра второго операнда и к второму информационному входу блока оперативной памяти, третий информационный вход которого подключен к информационному выходу арифметико-логического блока, выход переноса/заема которого подключен к второму информационному входу триггера переноса, выход которого подключен к второму информационному входу триггера флага активности, к второму информационному входу арифметико-логического блока, к пятому .информационному входу триггера переполнения и к четвертому информационному входу блока оперативной памяти, третий выход регистра второго операнда подключен к третьему информационному входу арифметико-логического блока и к четвертому информационному входу регистра первого операнда, первый выход регистра входа-выхода подключен к пятому информационному входу регистра первого операнда и к четвертому информационному входу регистра второго операнда, второй выход регистра входа-выхода подключен к четвертому входу первого элемента 2И-ИЛИ, выход которого подключен к информационному-выходу процессора, вход-выход признака которого подключен к информационному входу-вькоду магистрального элемента.

У4

Фиг. 2

7«

Y2

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1262516A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Процессор | 1984 |

|

SU1200294A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

Изобретение относится к вычислительной технике и может быть использовано в составе специализированных быстродействующих вычислительных систем обработки изображений. Цель изобретения - увеличение быстродействия. Поставленная цель достигается тем, что процессор матричной вычислительной структуры содержит дешифратор 1, регистр 2 входа-выхода, регистр 3 первого операнда, регистр 4 второго операнда, триггер 5 переноса, блок 6 оперативной памяти, первый и второй блоки 7 и 8 управления, распределитель 9 импульсов, арифметико-логический блок 10, триггер 11 переполнения, триггер 12 Флага активности, триггер 13 маски, триггер 14 загрузки, с первого по третий элементы 2 И-ИЛИ 15-17, элемент ИЛИ 18, коммутатор 19, магистральный элемент 20. 3 ил.

т

/J

7/ .-Jf

С

75

У/

i/гЗ

| Однородные вычислительные среды. | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Все- союзн | |||

| школы-семинара по параллельной обработке информации | |||

| Львов, 1981 | |||

| Механический грохот | 1922 |

|

SU41A1 |

| Syctolic array chip matches the pace of high-Speed processing | |||

| - ;, Electronic Design, 1984, .October 31. | |||

Авторы

Даты

1990-10-30—Публикация

1987-10-12—Подача