Изобретение относится к области вычислительной техники, предназначено для сопряжения двух вычислительных машин, имеющих магистральный параллельный интерфейс, и может быть использовано для тестирования и отладки запоминающих и внешних устройств ведомой ЭВМ, а также для межмашинного обмена информацией.

Цель изобретения - расширение функциональных возможностей за счет обеспечения оперативной настройки ведущей ЭВМ на режим прямого доступа к заданной области адресов ведойой ЭВМ при оперативном и независимом изменении границ и размеров области

адресуемого пространства (окна) ведущей и ведомой ЭВМ.

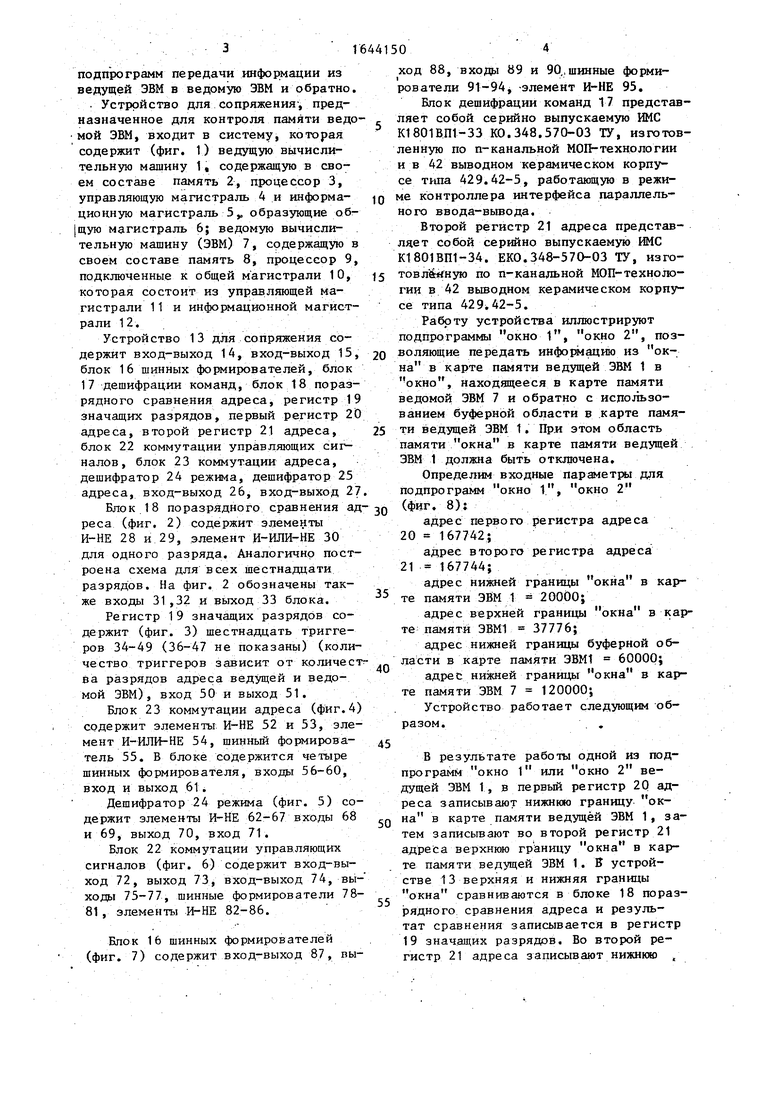

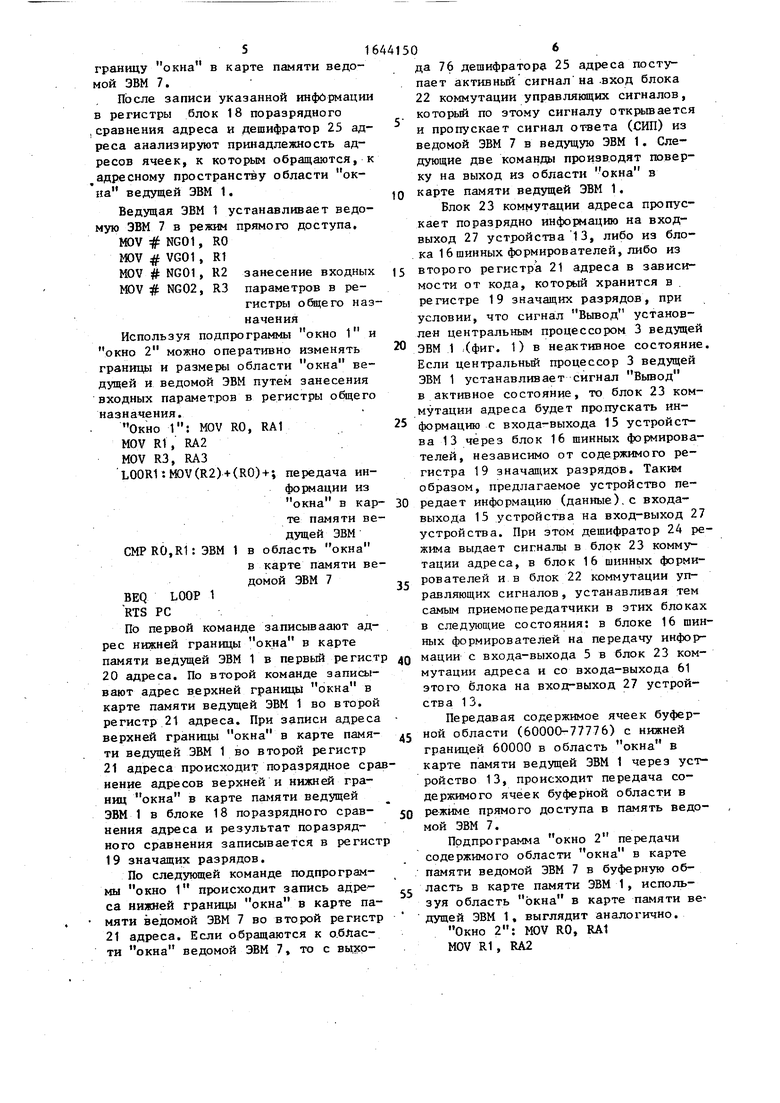

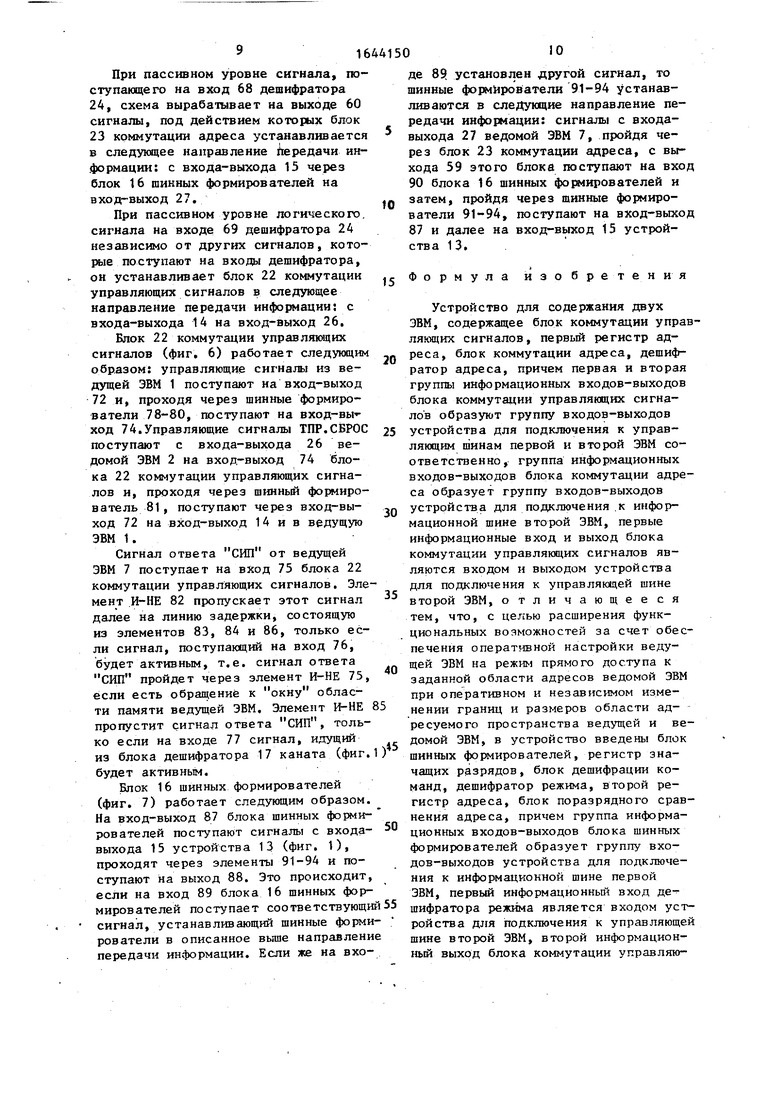

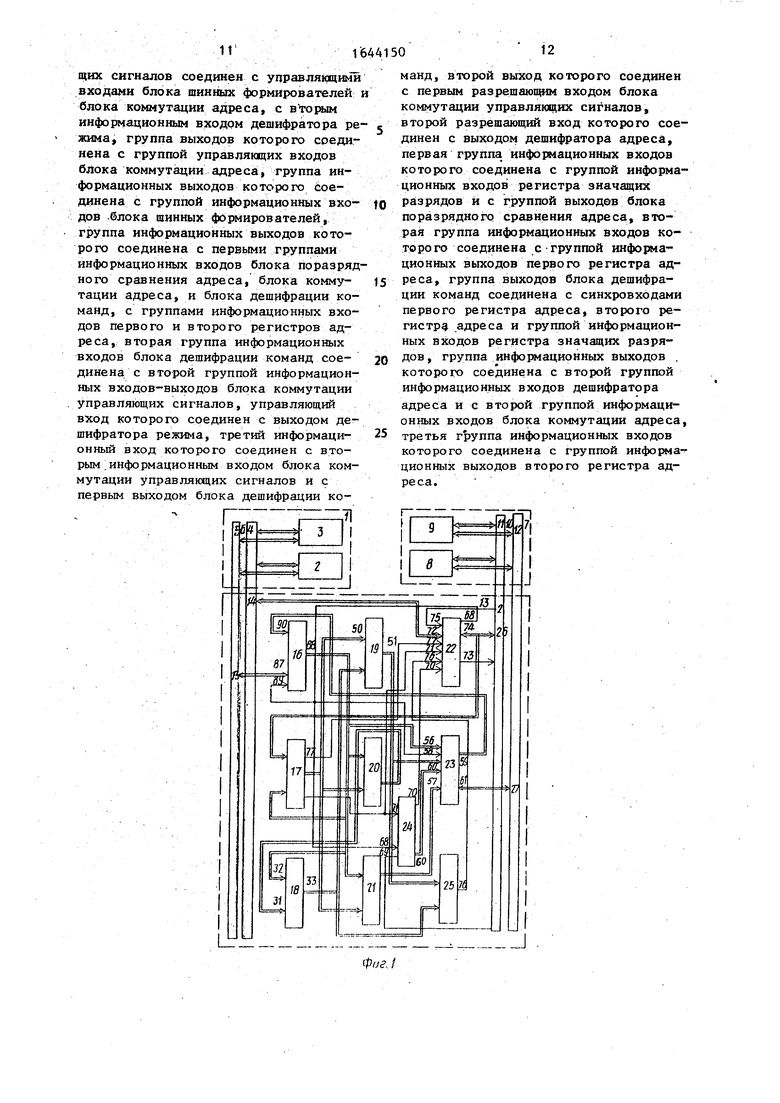

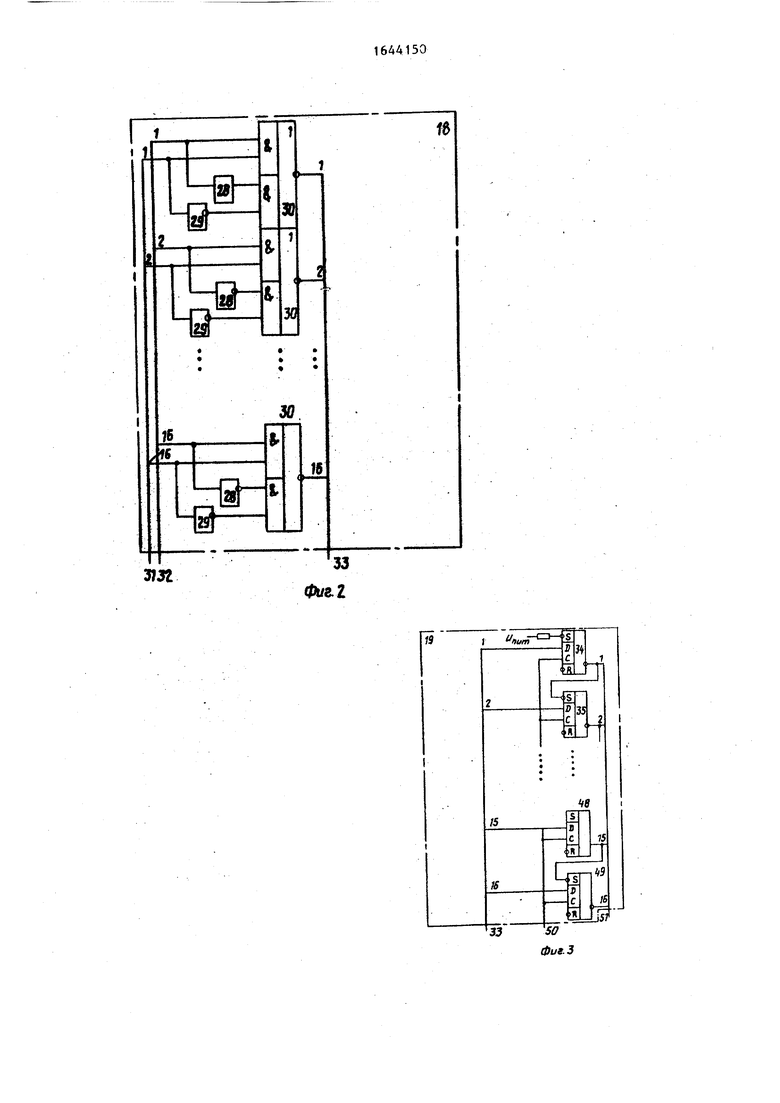

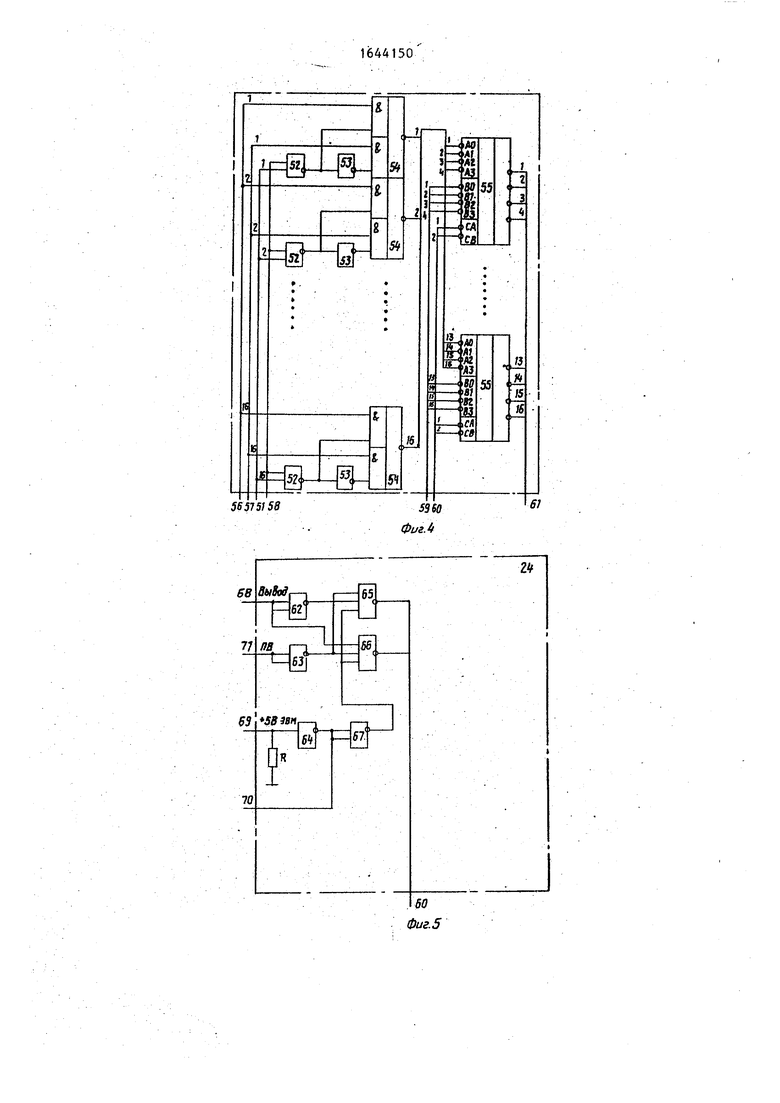

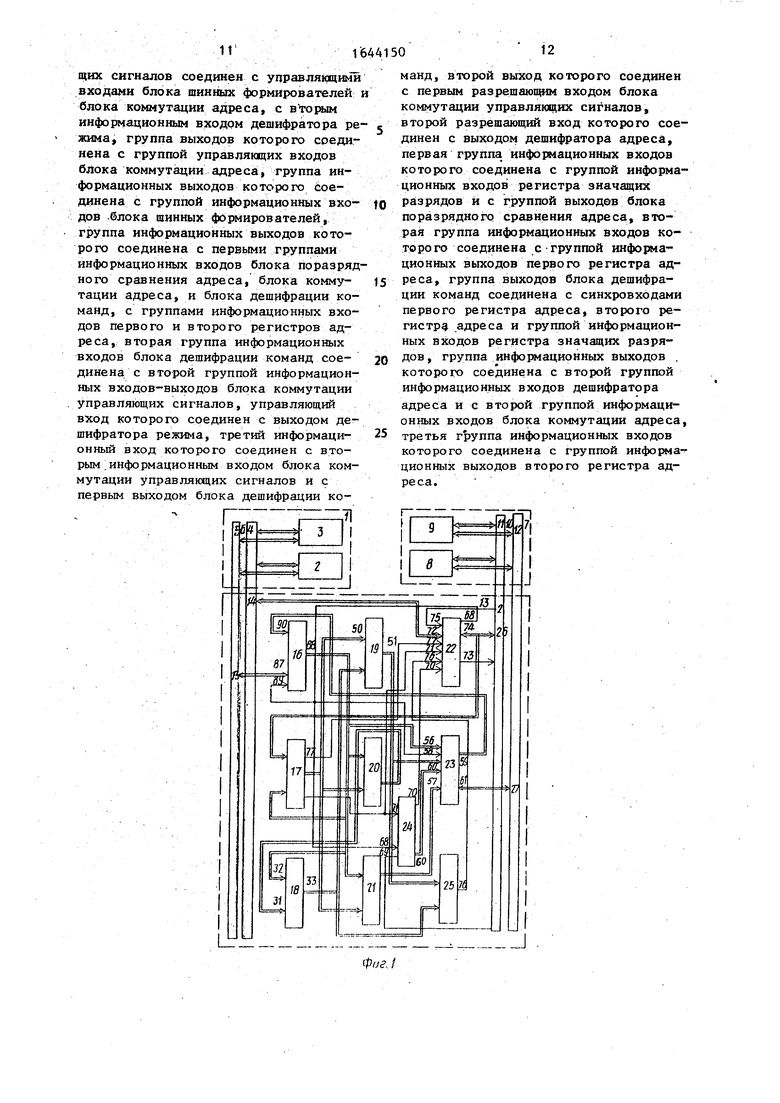

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока поразрядного сравнения адреса; на фиг. 3 - структурируя схема регистра значащих разрядов; на фиг. 4 - структурная схема блока коммутации адреса; на фиг. 5 - структурная схема дешифратора режима; на фиг. 6 - структурная схема блока коммутации управляющих сигналов; на фиг. 7 - структурная схема блока шинных формирователей; на фиг. 8 - иллюстрация работы

О

нЬь

Јъ

СЛ

О

подпрограмм передачи информации из ведущей ЭВМ в ведомую ЭВМ и обратно. . Устройство для сопряжения-, предназначенное для контроля памяти ведомой ЭВМ, входит в систему, которая содержит (фиг. 1) ведущую вычислительную машину 1t содержащую в своем составе память 2, процессор 3, управляющую магистраль 4 и информационную магистраль 5V образующие об- |щую магистраль 6; ведомую вычислительную машину (ЭВМ) 7, содержащую в своем составе память 8, процессор 9, подключенные к общей магистрали 10, которая состоит из управляющей магистрали 11 и информационной магистрали 1 2.

Устройство 13 для сопряжения содержит вход-выход 14, вход-выход 15, блок 16 шинных формирователей, блок 17 дешифрации команд, блок 18 поразрядного сравнения адреса, регистр 19 значащих разрядов, первый регистр 20 адреса, второй регистр 21 адреса, блок 22 коммутации управляющих сигналов, блок 23 коммутации адреса, дешифратор 24 режима, дешифратор 25 адреса, вход-выход 26, вход-выход 27

Блок 18 поразрядного сравнения адреса (фиг. 2) содержит элементы И-НЕ 28 и 29, элемент И-ИЛИ-НЕ 30 для одного разряда. Аналогично построена схема для всех шестнадцати разрядов. На фиг. 2 обозначены также входы 31 ,32 и выход 33 блока.

Регистр 19 значащих разрядов содержит (фиг. 3) шестнадцать триггеров 34-49 (36-47 не показаны) (количество триггеров зависит от количества разрядов адреса ведущей и ведомой ЭВМ), вход 50 и выход 51.

Блок 23 коммутации адреса (фиг.4) содержит элементы И-НЕ 52 и 53, элемент И-ИЛИ-НЕ 54, шинный формирователь 55. В блоке содержится четыре шинных формирователя, входы 56-60, вход и выход 61 .

Дешифратор 24 режима (фиг. 5) содержит элементы И-НЕ 62-67 входы 68 и 69, выход 70, вход 71.

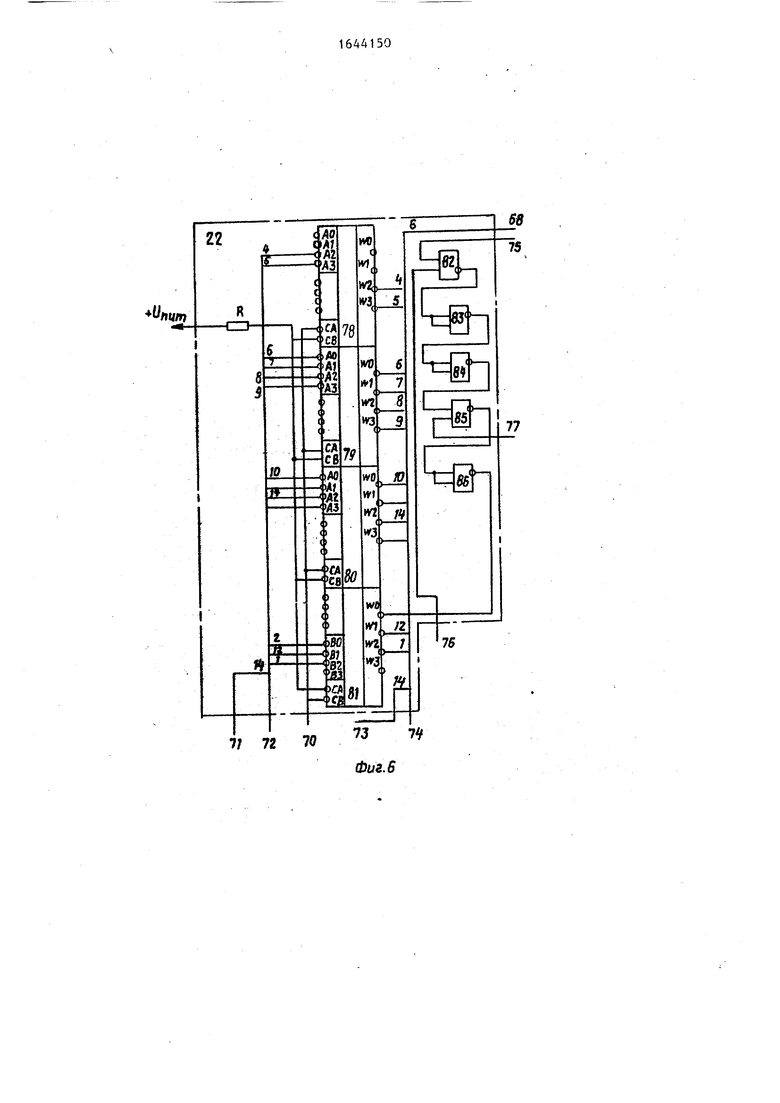

Блок 22 коммутации управляющих сигналов (фиг. 6) содержит вход-выход 72, выход 73, вход-выход 74, выходы 75-77, шинные формирователи 78- 81 , элементы И-НЕ 82-86.

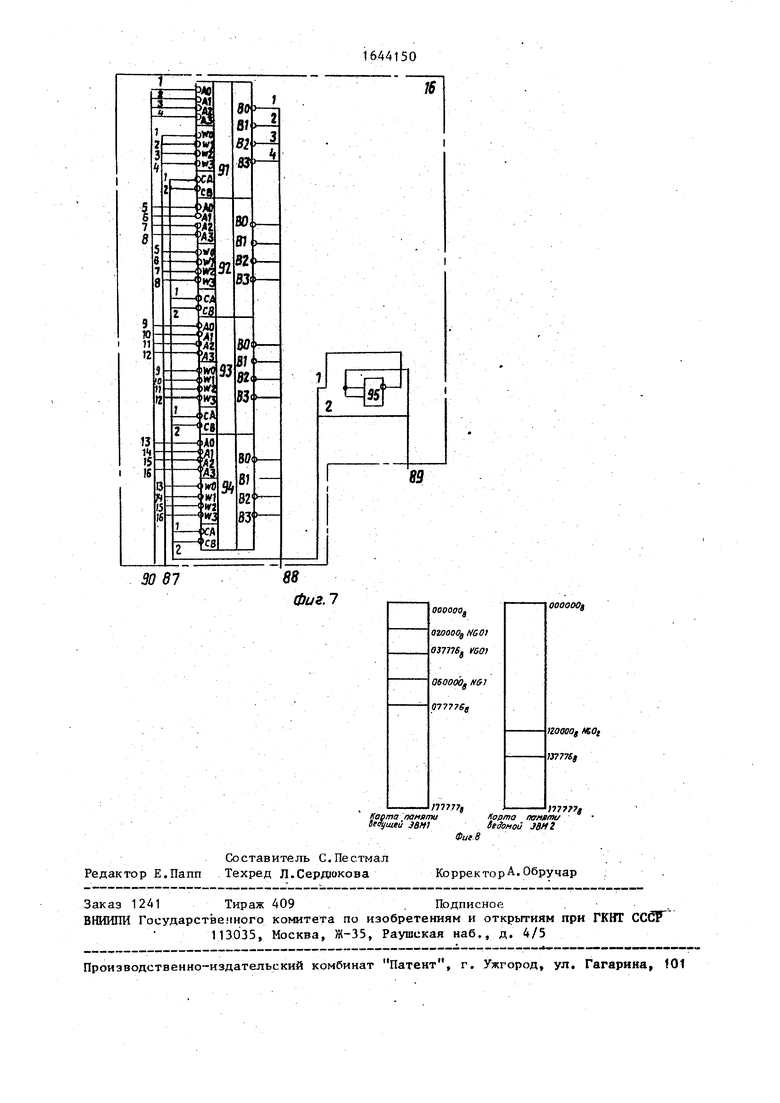

Блок 16 шинных формирователей (фиг. 7) содержит вход-выход 87, вы0

5

0

ход 88, входы 89 и 90,,шинные формирователи 91-94, -элемент И-НЕ 95.

Блок дешифрации команд 17 представляет собой серийно выпускаемую ИМС К1801ВП1-33 КО.348.570-03 ТУ, изготовленную по п-канальной МОП-технологии и в 42 выводном керамическом корпусе типа 429.42-5, работающую в режиме контроллера интерфейса параллельного ввода-вывода.

Второй регистр 21 адреса представляет собой серийно выпускаемую ИМС К1801ВП1-34. ЕКО.348-570-03 ТУ, изго- товл& №ую по n-канальной МОП-технологии в 42 выводном керамическом корпусе типа 429.42-5.

Работу устройства иллюстрируют подпрограммы окно 1, окно 2, позволяющие передать информацию из ок

0

5

0

0

5

на и

в карте памяти ведущей ЭВМ 1 в .

5

окно , находящееся в карте памяти ведомой ЭВМ 7 и обратно с использованием буферной области в карте памяти ведущей ЭВМ 1. При этом область памяти окна в карте памяти ведущей ЭВМ 1 должна быть отключена.

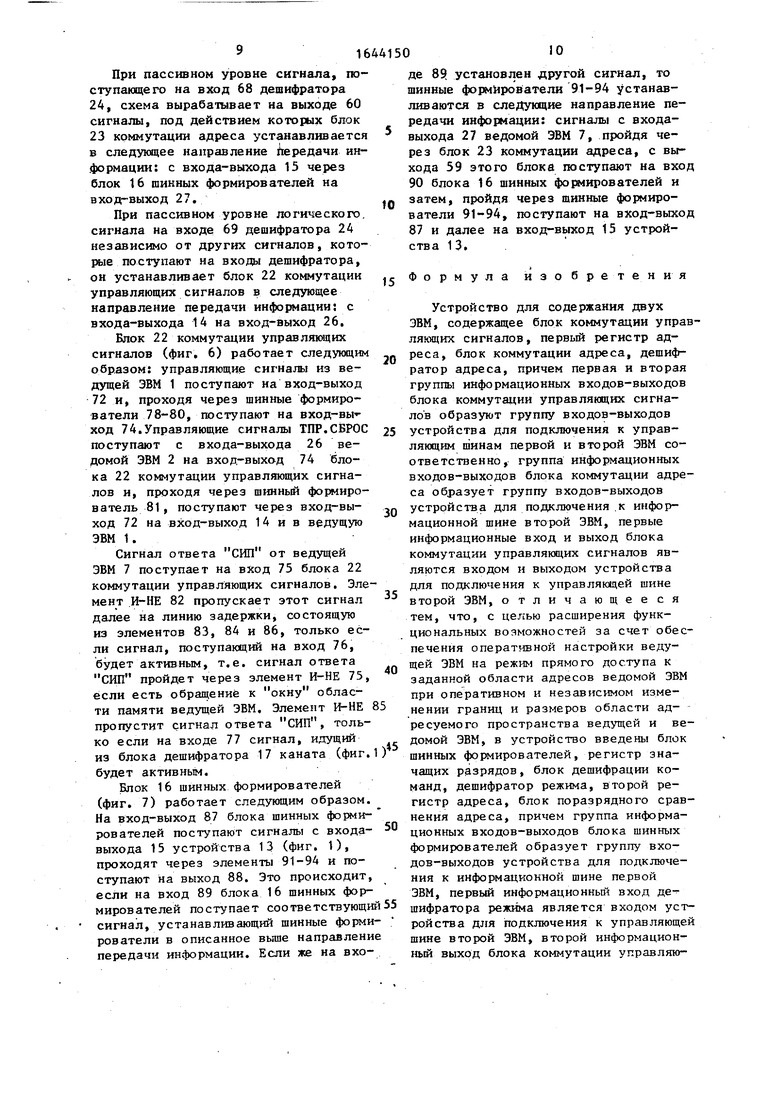

Определим входные параметры для подпрограмм окно 1, окно 2 (фиг. 8):

адрес первого регистра адреса

20 167742;

адрес второго регистра адреса

21- 167744;

адрес нижней границы окна в карте памяти ЭВМ 1 20000;

адрес верхней границы окна в карте памяти ЭВМ1 37776;

адрес нижней границы буферной области в карте памяти ЭВМ1 60000;

адрес нижней границы окна в карте памяти ЭВМ 7 120000;

Устройство работает следующим образом.

В результате работы одной из подпрограмм окно 1 или окно 2 ведущей ЭВМ 1, в первый регистр 20 адреса записывают нижнюю границу окна в карте памяти ведущей ЭВМ 1, затем записывают во второй регистр 21 адреса верхнюю границу окна в карте памяти ведущей ЭВМ 1. S устройстве 13 верхняя и нижняя границы окна сравниваются в блоке 18 поразрядного сравнения адреса и результат сравнения записывается в регистр 19 значащих разрядов. Во второй регистр 21 адреса записывают нижнюю ,

окна

в карте памяти ведогран иду мой ЭВМ 7.

После записи указанной информации в регистры блок 18 поразрядного

,сравнения адреса и дешифратор 25 адреса анализируют принадлежность адресов ячеек, к которым обращаются, к

fадресному пространству области окна ведущей ЭВМ 1.

Ведущая ЭВМ 1 устанавливает ведомую ЭВМ 7 в режим прямого доступа. MOV # NG01, RO MOV # VG01 , R1 MOV # NG01, R2

MOV # NG02, R3

занесение входных параметров в регистры общего назначения

Используя подпрограммы окно 1 и окно 2 можно оперативно изменять границы и размеры области окна ведущей и ведомой ЭВМ путем занесения входных параметров в регистры общего назначения.

Окно MOV RO, RA1 MOV R1, RA2 MOV R3, RA3

LOOR1:MOV(R2) + (RO) + ; передача информации из окна в карте памяти ведущей ЭВМ CMPRO,R1:3BM 1 в область окна

в карте памяти ведомой ЭВМ 7 BEQ LOOP 1 RTS PC

По первой команде записываают адрес нижней границы окна в карте памяти ведущей ЭВМ 1 в первый регист

20адреса. По второй команде записывают адрес верхней границы окна в карте памяти ведущей ЭВМ 1 во второй регистр 21 адреса. При записи адреса верхней границы окна в карте памяти ведущей ЭВМ 1 во второй регистр

21адреса происходит поразрядное сравнение адресов верхней и нижней границ окна в карте памяти ведущей

ЭВМ 1 в блоке 18 поразрядного сравнения адреса и результат поразрядного сравнения записывается в регист 19 значащих разрядов.

По следующей команде подпрограммы окно 1 происходит запись адреса нижней границы окна в карте памяти ведомой ЭВМ 7 во второй регистр 21 адреса. Если обращаются к области окна ведомой ЭВМ 7, то с выхо1644150

5

0

5

да 76 дешифратора 25 адреса поступает активный сигнал на вход блока 22 коммутации управляющих сигналов, который по этому сигналу открывается и пропускает сигнал ответа (СИП) из ведомой ЭВМ 7 в ведущую ЭВМ 1. Следующие две команды производят поверку на выход из области окна в

Q карте памяти ведущей ЭВМ 1.

Блок 23 коммутации адреса пропускает поразрядно информацию на вход- выход 27 устройства 13, либо из блока 16шинных формирователей, либо из

5 второго регистра 21 адреса в зависимости от кода, который хранится в регистре 19 значащих разрядов, при условии, что сигнал Вывод установлен центральным процессором 3 ведущей

0 ЭВМ 1 (фиг. 1) в неактивное состояние. Если центральный процессор 3 ведущей ЭВМ 1 устанавливает сигнал Вывод в активное состояние, то блок 23 коммутации адреса будет пропускать ин5 формацию с входа-выхода 15 устройства 13 через блок 16 шинных формирователей, независимо от содержимого регистра 19 значащих разрядов. Таким образом, предлагаемое устройство пе0 редает информацию (данные) с входа- выхода 15 устройства на вход-выход 27 устройства. При этом дешифратор 24 режима выдает сигналы в блок 23 коммутации адреса, в блок 16 шинных формирователей и в блок 22 коммутации управляющих сигналов, устанавливая тем самым приемопередатчики в этих блоках в следующие состояния: в блоке 16 шинных формирователей на передачу информации с входа-выхода 5 в блок 23 коммутации адреса и со входа-выхода 61 этого блока на вход-выход 27 устройства 1 3.

Передавая содержимое ячеек буфер5 ной области (60000-77776) с нижней границей 60000 в область окна в карте памяти ведущей ЭВМ 1 через устройство 13, происходит передача содержимого ячеек буферной области в

0 режиме прямого доступа в память ведомой ЭВМ 7.

Подпрограмма окно 2 передачи содержимого области окна в карте памяти ведомой ЭВМ 7 в буферную область в карте памяти ЭВМ 1, используя область окна в карте памяти ведущей ЭВМ 1, выглядит аналогично.

Окно MOV RO, RA1

MOV R1 , RA2

MOV R3, RA3

LOOP2:MOV(RO)+,(R2)+

CMP RO, R1

BEQ LOOP2

RES PC

При активном уровне сигнала Вывод, который вырабатывается в управляющей магистрали 4, когда выполняется третий оператор подпрограммы окно 2, дешифратор 24 режима вырабатывает управляющие сигналы, которые переключают блок 23 коммутации адреса и блок 16 шинных формирователей так, что сигналы идут с входа- выхода 27 на вход-выход 15, поступая на вход-выход 61 блока 23 коммутации адреса, выходят с выхода 59 этого блока и поступают на вход 90 блока 16 шинных формирователей, по- том с входа-выхода 87 этого блока поступают на вход-выход 15 устройства 13. Таким образом организовано чтение данных из области памяти окна ведомой ЭВМ 7 и запись в буфер- ную область в памяти ведущей ЭВМ 1.

Блок 18 поразрядного сравнения адреса (фиг. 2) работает следующим образом: на вход 31 подаются разряды, определяющие нижнюю границу об- ласти окна в карте памяти ведущей ЭВМ 1, по входу 32 подаются адресные разряды ведущей ЭВМ 1. Схема обеспечивает поразрядное сравнение поступающих на ее входы кодов и вы- дачу на выход 33 кода, определяющего результат поразрядного сравнения.

Регистр 19 значащих разрядов (фиг. 3) работает следующим образом. С выхода 33 блока 18 поступает код, определяющий результат поразрядного сравнения в том разряде, где имеется негативный результат поразрядного сравнения - в триггеры этого и всех более младших разрядов записывается логическая 1, а во все более старшие разряды, где результат поразрядного сравнения позитивный - записывается логический О. Сформированный таким образом код подается с ВЫХ да 51 на вход дешифратора 25 адреса и хранится в триггерах 34-49. По входу 50 подаются сигналы, осуществля- ющие управление процессом записи и считывания информации.

Блок 23 коммутации адреса (фиг. 4 позволяет в зависимости от кода, который хранится в регистре 19 значащих разрядов, получить на выходе код

по следующей логике - если сигнал Вывод в ведущей ЭВМ 1 установлен в неактивное состояние, то в зависимости от содержимого регистра 19 значащих разрядов в данном разряде на выходе блока 23 коммутации адреса получают либо значение логических сигналов, идущих на вход-выход 15 без изменения, либо значение логического сигнала для данного разряда, записанного во второй регистр 22 адреса, т.е. модифицированное значение сигнала для конкретного разряда.

Если сигнал Вывод установлен в активное состояние, то независимо от содержимого регистра 19 значащих разрядов в данном разряде на выходе схемы получают инверсное значение сигналов, поступающих из входа-выхот да 15 устройства 13.

Аналогично работают все разряды данного блока. Вход 56 соединен с входом 88 (фиг. 1) блока 16 шинных формирователей, на этот вход поступают сигналы из входа-выхода 15 устройства 13. Вход 57 соединен с выходом второго регистра 21 адреса, на этот вход поступают разряды нижней границы области окна ведомой ЭВМ 7

Вход 51 соединен с выходом регистра 19 значащих разрядов, на этот вход поступает информация о результате сравнения нижней и верхней границ области окна ведущей ЭВМ 1. Вход 58 соединен с входом 89 блока 16 шинных формирователей, на этот вход поступает сигнал Вывод с выхода 68 блока 22 коммутации управляющих сигналов .

Дешифратор 24 режима (фиг. 5) работает следующим образом. При отсутствии сигнала (логический О) на входе 69 дешифратора 24 схема выдает сигналы на выходах 70 и 60, под действием которых вход-выход 61 блока 23 коммутации адреса и вход-выход 74 блока 22 коммутации управляющих сигналов устанавливаются в высокоим- педансное состояние.

При активном уровне сигнала, постпающего на вход 69 дешифратора 24, и при активном уровне сигнала, поступающего на вход 68, схема вырабатывает сигналы, которые переводят блок 23 коммутации адреса в режим передачи информации из входа-выхода 27 через блок 16 шинных формирователей на вход-выход 15.

to

15

y1644150

При пассивном уровне сигнала, поступающего на вход 68 дешифратора 24, схема вырабатывает на выходе 60 сигналы, под действием которых блок 23 коммутации адреса устанавливается в следующее направление передачи информации: с входа-выхода 15 через блок 16 шинных формирователей на вход-выход 27.

При пассивном уровне логического, сигнала на входе 69 дешифратора 24 независимо от других сигналов, которые поступают на входы дешифратора, он устанавливает блок 22 коммутации управляющих сигналов в следующее направление передачи информации: с входа-выхода 14 на вход-выход 26.

Блок 22 коммутации управляющих сигналов (фиг. 6) работает следующим образом: управляющие сигналы из ведущей ЭВМ 1 поступают на вход-выход 72 и, проходя через шинные формирователи 78-80, поступают на вход-вм - ход 74.Управляющие сигналы ТПР.СБРОС поступают с входа-выхода 26 ведомой ЭВМ 2 на вход-выход 74 блока 22 коммутации управляющих сигналов и, проходя через шинный формирователь 81 , поступают через вход-выход 72 на вход-выход 14 и в ведущую ЭВМ 1.

Сигнал ответа СИП от ведущей ЭВМ 7 поступает на вход 75 блока 22 коммутации управляющих сигналов. Элемент И-НЕ 82 пропускает этот сигнал далее на линию задержки, состоящую из элементов 83, 84 и 86, только если сигнал, поступающий на вход 76, будет активным, т.е. сигнал ответа СИП пройдет через элемент И-НЕ 75, если есть обращение к окну области памяти ведущей ЭВМ. Элемент И-НЕ 85 пропустит сигнал ответа СИП, только если на входе 77 сигнал, идущий

20

25

30

35

40

10

де 89. установлен другой сигнал, то шинные формирователи 91-94 устанавливаются в следующие направление передачи информации: сигналы с входа- выхода 27 ведомой ЭВМ 7, пройдя через блок 23 коммутации адреса, с выхода 59 этого блока поступают на вход 90 блока 16 шинных формирователей и затем, пройдя через тинные формирователи 91-94, поступают на вход-выход 87 и далее на вход-выход 15 устройства 13.

Формула изобретения

Устройство для содержания двух ЭВМ, содержащее блок коммутации управ ляющих сигналов, первый регистр адреса, блок коммутации адреса, дешифратор адреса, причем первая и вторая группы информационных входов-выходов блока коммутации управляющих сигналов образуют группу входов-выходов устройства для подключения к управляющим шинам первой и второй ЭВМ соответственно, группа информационных входов-выходов блока коммутации адреса образует группу входов-выходов устройства для подключения к информационной шине второй ЭВМ, первые информационные вход и выход блока коммутации управляющих сигналов являются входом и выходом устройства для подключения к управляющей шине второй ЭВМ, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения оперативной настройки ведущей ЭВМ на режим прямого доступа к заданной области адресов ведомой ЭВМ при оперативном и независимом изменении границ и размеров области адресуемого пространства ведущей и ведомой ЭВМ, в устройство введены блок

r.J Cl-din О ,и,- I I rii , ,7 «ч - -

из блока дешифратора 17 каната (фиг.1) шинных формирователей, регистр зна- будет активным.

Блок 16 шинных формирователей (фиг. 7) работает следующим образом. На вход-выход 87 блока шинных формирователей поступают сигналы с входа- выхода 15 устройства 13 (фиг. 1), проходят через элементы 91-94 и поступают на выход 88. Это происходит, если на вход 89 блока 16 шинных фор50

чащих разрядов, блок дешифрации команд, дешифратор режима, второй регистр адреса, блок поразрядного сравнения адреса, причем группа информационных входов-выходов блока шинных формирователей образует группу входов-выходов устройства для подключения к информационной шине первой ЭВМ, первый информационный вход демирователей поступает соответствующий55 шифратора режима является входом устсигнал, устанавливающий шинные формирователи в описанное выше направление передачи информации. Если же на вхоройства для подключения к управляющей шине второй ЭВМ, второй информационный выход блока коммутации управляю

0

10

де 89. установлен другой сигнал, то шинные формирователи 91-94 устанавливаются в следующие направление передачи информации: сигналы с входа- выхода 27 ведомой ЭВМ 7, пройдя через блок 23 коммутации адреса, с выхода 59 этого блока поступают на вход 90 блока 16 шинных формирователей и затем, пройдя через тинные формирователи 91-94, поступают на вход-выход 87 и далее на вход-выход 15 устройства 13.

Формула изобретения

0

5

0

5

0

Устройство для содержания двух ЭВМ, содержащее блок коммутации управляющих сигналов, первый регистр адреса, блок коммутации адреса, дешифратор адреса, причем первая и вторая группы информационных входов-выходов блока коммутации управляющих сигналов образуют группу входов-выходов устройства для подключения к управляющим шинам первой и второй ЭВМ соответственно, группа информационных входов-выходов блока коммутации адреса образует группу входов-выходов устройства для подключения к информационной шине второй ЭВМ, первые информационные вход и выход блока коммутации управляющих сигналов являются входом и выходом устройства для подключения к управляющей шине второй ЭВМ, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения оперативной настройки ведущей ЭВМ на режим прямого доступа к заданной области адресов ведомой ЭВМ при оперативном и независимом изменении границ и размеров области адресуемого пространства ведущей и ведомой ЭВМ, в устройство введены блок

шинных формирователей, регистр зна-

шинных формирователей, регистр зна-

чащих разрядов, блок дешифрации команд, дешифратор режима, второй регистр адреса, блок поразрядного сравнения адреса, причем группа информационных входов-выходов блока шинных формирователей образует группу входов-выходов устройства для подключения к информационной шине первой ЭВМ, первый информационный вход дешифратора режима является входом устройства для подключения к управляющей шине второй ЭВМ, второй информационный выход блока коммутации управляющих сигналов соединен с управляющими входами блока шинных формирователей блока коммутации адреса, с в торым информационным входом дешифратора ре- жима, группа выходов которого соединена с группой управляющих входов блока коммутации адреса, группа информационных выходов которого соединена с группой информационных вхо- дов блока шинных формирователей, группа информационных выходов которого соединена с первыми группами информационных входов блока поразрядного сравнения адреса, блока комму- тации адреса, и блока дешифрации команд, с группами информационных входов первого и второго регистров адреса, вторая группа информационных входов блока дешифрации команд сое- динена с второй группой информационных входов-выходов блока коммутации управляющих сигналов, управляющий вход которого соединен с выходом дешифратора режима, третий информаци- онный вход которого соединен с вторым информационным входом блока коммутации управляющих сигналов и с первым выходом блока дешифрации команд, второй выход которого соединен с первым разрешающим входом блока коммутации управляющих сигналов, второй разрешающий вход которого соединен с выходом дешифратора адреса, первая группа информационных входов которого соединена с группой информационных входов регистра значащих разрядов и с группой выходов блока поразрядного сравнения адреса, вторая группа информационных входов которого соединена с группой информационных выходов первого регистра адреса, группа выходов блока дешифрации команд соединена с синхровходами первого регистра адреса, второго регистру адреса и группой информационных входов регистра значащих разрядов, группа информационных выходов . которого соединена с второй группой информационных входов дешифратора адреса и с второй группой информационных входов блока коммутации адреса третья группа информационных входов которого соединена с группой информационных выходов второго регистра адреса.

ч «

fe

LJ

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1982 |

|

SU1059561A1 |

| Устройство для формирования изображения | 1988 |

|

SU1575230A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1987 |

|

SU1411764A1 |

| Устройство для сопряжения цифровой вычислительной машины | 1987 |

|

SU1444793A1 |

| Устройство для отображения многоугольников на экране растрового графического видеоконтрольного блока | 1987 |

|

SU1534454A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645960A1 |

| Устройство для контроля печатных плат | 1986 |

|

SU1472929A1 |

| Запоминающее устройство | 1988 |

|

SU1608746A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМИ УСТРОЙСТВАМИ | 1991 |

|

RU2024052C1 |

Изосретение относится к вычислительной технике, предназначено для сопряжения двух ЭВМ, имеющих магистральный параллельный интерфейс, и может быть использовано для тестирова2 V ния и отладки запоминающих и внешних устройств ведомой ЭВМ, а также для межмашинного обмена информацией. Целью изобретения является расширение функциональных возможностей за счет обеспечения оперативной настройки ведущей ЭВМ на режим прямого доступа и заданной области адресов ведомой ЭВМ при оперативном и независимом изменении границ и размеров области адресуемого пространства ведущей и ведомой ЭВМ. Устройство содержит блок шинных формирователей, регистр значащих разрядов, блок коммутации управляющих сигналов, блок дешифрации команд, блок коммутации адреса, дешифратор режима, блок поразрядного сравнения адреса, дешифратор адреса, два регистра адреса. 8 ил. (Л

4

л I

ft

S3 SO фиг.Ь

61

о in

r }

vD

Фиг. 7

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1251093A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1154674, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-23—Публикация

1988-05-25—Подача