г гп

гг гJ

с

(Л

точности обнаружения и коррекции ошибок путем применения кода Файра. Устройство содержит буферный блок 1 памяти,два блока 2 и 3 памяти ошибочных байтов, с первого по третий коммутаторы 4-6, группу элементов И 7, формирователи 8 четности, первый 9 и второй 10 элементы ИЛИ, блок 11 обнаружения ошибок, блок 12 памяти адресов ошибок, формирователь 13 импульсов, блок 14 выбора адреса, формирователь 15 сигналов обращения, счетчик 16, регистр 17 сдвига, преобразователь 18 последовательного кода в параллельный, генератор 30 та товых импульсов, элемент НЕ 31, элемент И 32 и триггер 33, На вход 20 устройства поступает сигнал начальной установки, на вход 24 - блок информации в последовательном коде, сопровождаемый тактовыми сигналами

на входе 19. Преобразователь 18 преобразует код информации в параллельный код по восемь бит, поступающий на входы блока 1. Тактовые сигналы со входа 19 обеспечивают прием информации в блок 11, предназначенный для обработки блоков информации по 1024 информационных бита и восемнадцати проверочньк разрядов. В блоке 11 используется код Файра, описываемый многочленом (х -f 1) (х +Х+1) (х -ьХ+1) , который позволяет исправить пакет ошибок длиной шесть бит и обнаруткить пакет ошибок длиной до двенадцати бит, за счет чего повышается точность обнаружения ошибок. На выходы 27 и 26 блока 11 выводятся соответственно сигнал налттчия ошибок и сигнал некорректируемой ошибки. При считывании выполняется коррекция ошибок при помощи формирователей 8 четности. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1372364A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372366A1 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| Устройство обмена информацией между ЭВМ и абонентами | 1990 |

|

SU1835545A1 |

| Устройство для вывода информации | 1991 |

|

SU1833857A1 |

Изобретение относится к области вычислительной техники, а именно к запоминающим устройствам, и может быть применено для коррекции ошибок в каналах передачи блоков информации из накопителей на магнитных лентах, дисках,в частности для исправления пакетов ошибок при считывании информа ции из запоминаюпщх устройств на цилиндр ическргх магнитных доменах. Целью изобретения является повьшение

1

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть применено для коррекции ошибок в каналах передачи блоков информации в после- довательном коде, например, при считывании информации из накопителей на магнитных лентах, дисках и, в частности, для исправления пакетов ошибок при считывании информации из запоми- наюцщх устройств на цилиндрических магнитных доменах.

Целью изобретения является повышение точности обнаружения и коррекции ошибок путем применения кода Файра.

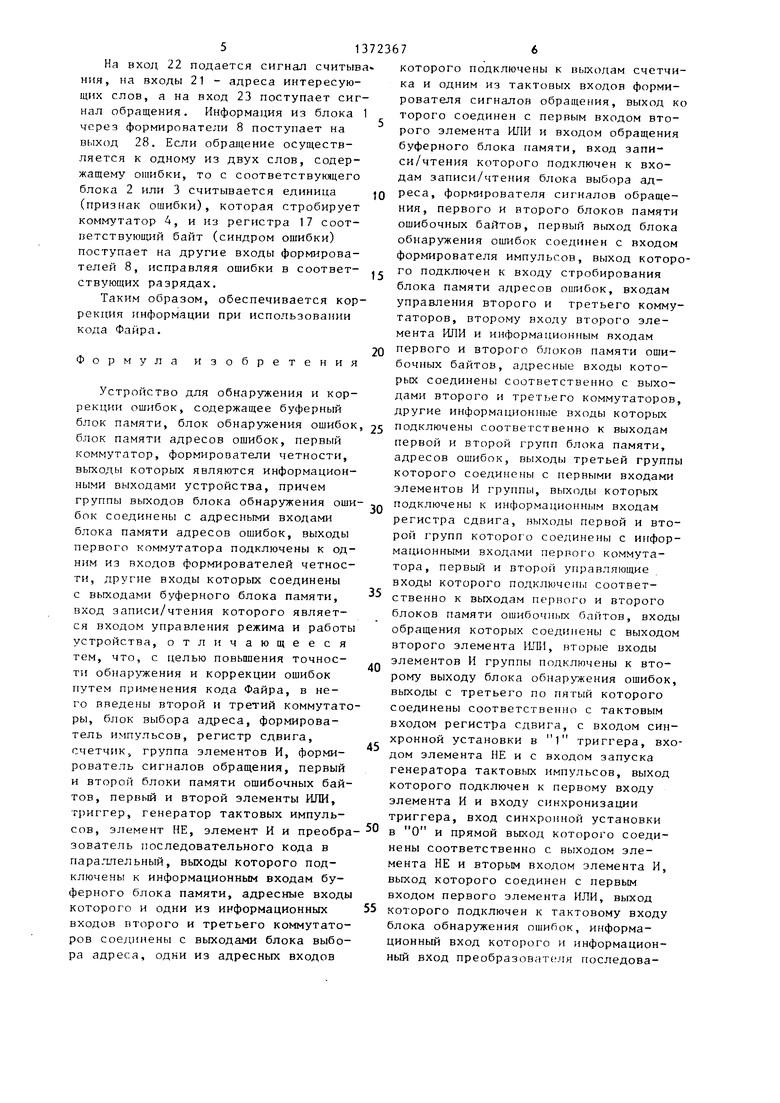

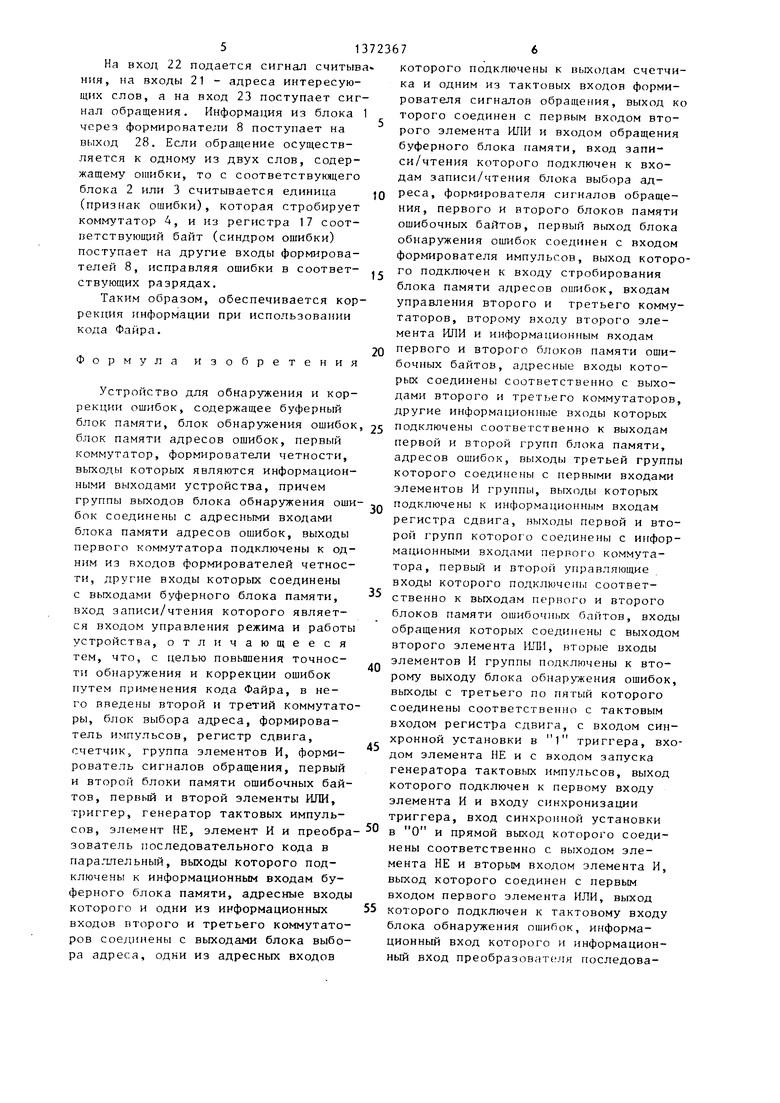

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема наиболее предпочтительного варианта вы- полнения блока обнаружения ошибок.

Предлагаемое устройство содержит (фиг.1) буферный блок 1 памяти, первый 2.и второй 3 блоки памяти ошибочных байтов, с первого по третий коммутаторы 4-6, группу элементов И 7, формирователи 8 четности, первый 9 и второй Ю элементы ИЛИ, блок 11 обнаружения ошибок, блок 12 памяти адресов ошибок, формирователь 13 им-

пульсов, блок 14 выбора адреса, формирователь 15 сигналов обращения, счетчик 16, регистр 17 сдвига, преобразователь 18 последовательного кода в параллельный.

На фиг.1 обозначены тактовый вход 19, вход 20 начальной установки, адресные входы 21, вход 22 управления режимом работы, вход 23 обращения, информационный вход 24 устройства, вход 25 элемента И 9, контрольные входы 26 и 27 и информационные выходы 28 устройства, блок 29 запуска режима коррекции.

Устройство содержит также генератор 30 тактовых импульсов, элемент НЕ 31, элемент И 32 и триггер 33.

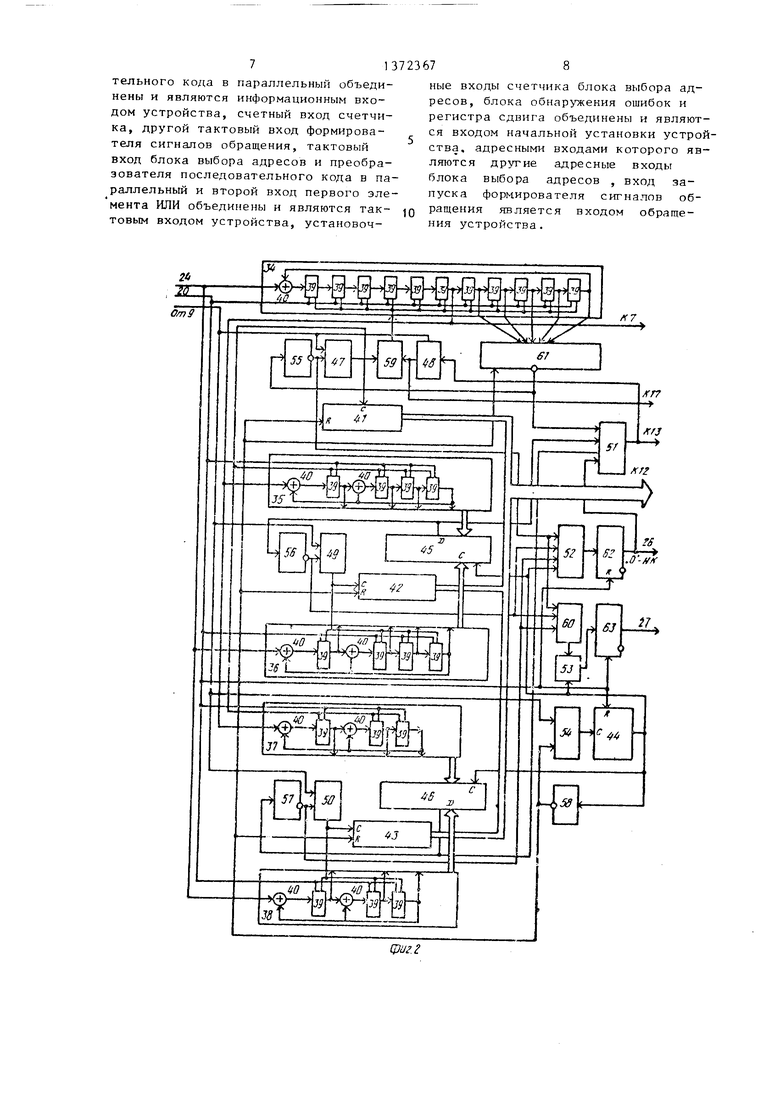

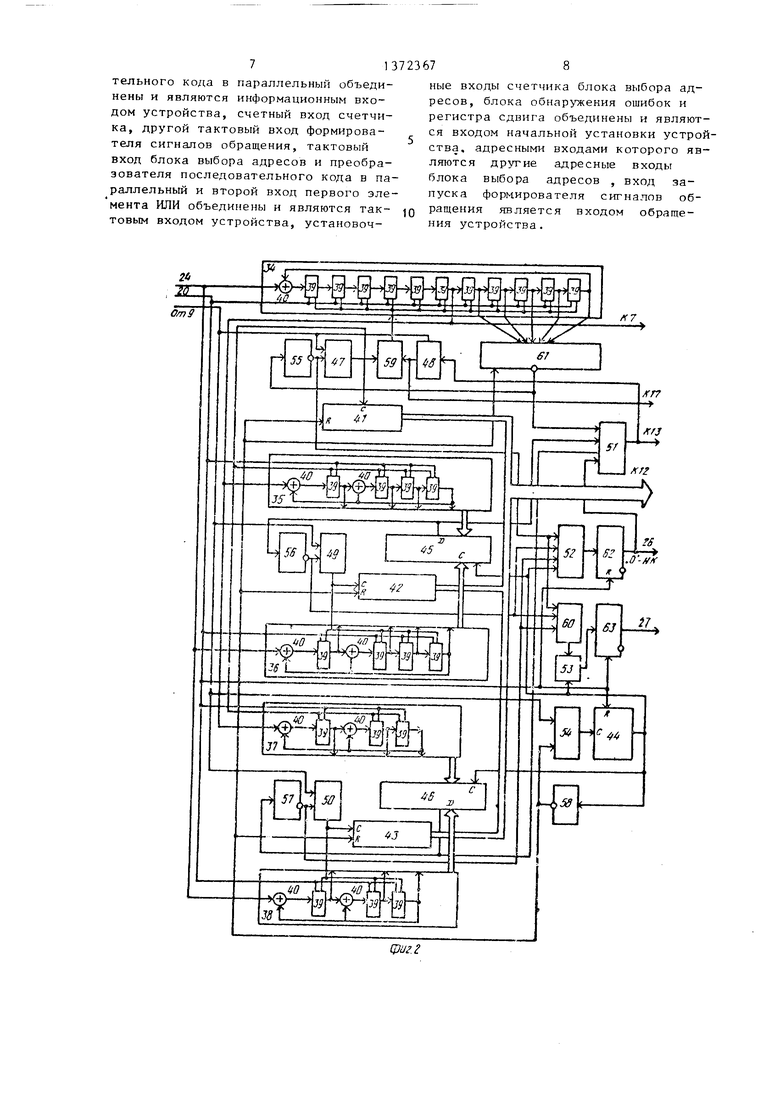

Блок 11 обнаружения ошибок содержит (фиг.2) регистры 34-38, состоящие из D-триггеров 39 и формирователей 40 четности, счетчики 41-44, блоки 45 и 46 сравнения, элементы И 47-54 элементы НЕ 56-58, элементы ИЛИ 59 и 60, элементы ИЛИ-НЕ 61 и триггеры 62 и 63.

Блок 12 памяти адресов ошибок мо- жйт быть выполнен в виде трех бло- кол постоянной памяти.

2 и 3 памяти ошибочных байтов Ь11полнены одноразрядными.

Предлагаемое устройство работает следуюи1Д1м образом.

На вход 20 (фиг.2) поступает сигнал начальной установки. На вход 24 в последовательном коде поступает блок информации, сопровождаемый тактовыми сигналами, поступающими на вход 19. Преобразователь 18 осуществляет преобразование последовательного кода в параллельный, например, по восемь бит, KOTopbrii поступает на информационные входы блока 1. Счетчик 16 обеспечивает счет тактовых импульсов, вследствие чего блоки 14 и 15 обеспечивают смену адресов и вьфабот- ку сигналов обращения через каждые восемь тактов. На вход 22 в этот момент поступает сигнал записи. На выходе фор№1рователя 13 сигнал отсутствует, вследствие чего в блоки 2 и 3 по всем адресам записываются нули. Тактовые сигналы с входа 10 через элемент ИЛИ 9 обеспечивают прием информации н блок 11.

Блок 11 предназначен для обработки блоков информации по 1024 информационных бита и восемнадцати проверочных разрядов. Общая длина последовательности, включая пустые разряды, составляет 1155 бит. Используется код Файра, описываемслй многочленом (х + 1)(х +Х+1) (х + Х+1), который позволяет исправ1 ть пакет ошибок длиной в шесть бит и обнаружить пакет ощибок длиной до двенадцати бит. По прошествии 1155 тактов (1024, включая 18 проверочных) в блок 11 записывается 128 восьмиразрядных слов, а на выходах 26 и 27 блока 11 будут контрольные сигналы, определяющие дальнейшую работу устройства.

Если на выходах 26 и 27 блока 11 нули, это означает, что ошибки в считанном слове нет и информация из блока 1 может быть использована, для чего на вход 22 необходимо подать сигнал считывания, на вход 21 - адрес интересуюп1его числа, а на вход 23 - сигнал обращения. На выходах 28

10

15

20

формация из блока 1 не 1.ожет быть и пачьзована, поскольку при данном ко де ошибки не исправляются.

На выходах 26 и 27 блока 11 присутствует сигнал наличия ошибки и сигнал корректируемой ошибки. В это случае необходимо исправить ошибку, т.е. определить адрес и синдром оши ки. Для этого вновь, но уже с более высокой частотой, с входа 25 запуск ется работа блока 11 без приема информации (поскольку вся коррекция м жет быть произведена в паузе между 1155 и 1156 тактовыми сигналами на входе 19). Это может быть выполнено например, с помощью блока 29. Через двадцать шесть тактов от генератора 30 обеспечивается поиск синдрома адреса и признака ошибки. Адрес оши ки поступает в блок 12, синдром в п следовательном коде поступает на эл менты И 7 группы,сигнал признака ошибки поступает на формирователь 1 которнй вырабатывает импульс. Один из выходов блока 12 стробируется та же, как и блоки 5 и 6 сигналом от б ка 13, а выходы, подключенные к эле ментам И 7, не стробируются, что об печивает поступление синдрома ошибк в тот разряд, с которого начинаются ошибки. Синдром в последовательном де сопровождается тактовыми импульс ми - сигналами из блока 11 в регист 17, обеспечивая прием и сдвиг в регистре 17 синдрома в сторону старших разрядов, вследствие чего на вы ходах регистра 17 будет синдром оши ки в параллельном коде. Импульс с выхода формирователя 13 должен быть выработан спустя время, необходимое для приема синдрома ошибки в регистр 17. Этот импульс, с одной сто роны, обеспечивает стробирование час ти блока 12 и выдачу двух последова тельных адресов, в которых произошли ошибки, на входы коммутаторов 5 и 6, которые в этом случае переключены на прием этих адресов. На и формационные входы блоков 2 и 3 по25

30

35

40

45

через соответствующее время обращения ступают единичные сигналы, а через будет получена информация.

На выходах блока 11 26 и 27 имеется сигнал наличия ошибки (например, на выходе 27 блока 11) и сигнал некорректируемой ошибки (например, на 55 выходе 26 блока 11).В этом слу-гае в принятой информации имеется ошибка разрядностью шесть-десять бит, и инэлемент ИЛИ 10 от формирователя 13 поступает сигнал обращения, обеспеч вая запись единицы по адресам, соде жащим ошибки. После этого запись информации в устройство прекращаетс Непосредственное исправление ошибок при считывании осуществляется следу щим образом.

о-10

15

20

3723674

формация из блока 1 не 1.ожет быть ис- пачьзована, поскольку при данном коде ошибки не исправляются.

На выходах 26 и 27 блока 11 присутствует сигнал наличия ошибки и сигнал корректируемой ошибки. В этом случае необходимо исправить ошибку, т.е. определить адрес и синдром ошибки. Для этого вновь, но уже с более высокой частотой, с входа 25 запускается работа блока 11 без приема информации (поскольку вся коррекция может быть произведена в паузе между 1155 и 1156 тактовыми сигналами на входе 19). Это может быть выполнено, например, с помощью блока 29. Через двадцать шесть тактов от генератора 30 обеспечивается поиск синдрома, адреса и признака ошибки. Адрес ошибки поступает в блок 12, синдром в последовательном коде поступает на элементы И 7 группы,сигнал признака ошибки поступает на формирователь 13, которнй вырабатывает импульс. Один из выходов блока 12 стробируется так же, как и блоки 5 и 6 сигналом от блока 13, а выходы, подключенные к элементам И 7, не стробируются, что обеспечивает поступление синдрома ошибки в тот разряд, с которого начинаются ошибки. Синдром в последовательном коде сопровождается тактовыми импульсами - сигналами из блока 11 в регистр 17, обеспечивая прием и сдвиг в регистре 17 синдрома в сторону старших разрядов, вследствие чего на выходах регистра 17 будет синдром ошибки в параллельном коде. Импульс с выхода формирователя 13 должен быть выработан спустя время, необходимое для приема синдрома ошибки в регистр 17. Этот импульс, с одной стороны, обеспечивает стробирование части блока 12 и выдачу двух последовательных адресов, в которых произошли ошибки, на входы коммутаторов 5 и 6, которые в этом случае переключены на прием этих адресов. На информационные входы блоков 2 и 3 по25

30

35

40

45

ступают единичные сигналы, а через

элемент ИЛИ 10 от формирователя 13 поступает сигнал обращения, обеспечивая запись единицы по адресам, содержащим ошибки. После этого запись информации в устройство прекращается. Непосредственное исправление ошибок при считывании осуществляется следующим образом.

На вход 22 подается сигнал считыва ния, на входы 21 - адреса интересующих слов, а на вход 23 поступает сигнал обращения. Информация из блока через формирователи 8 поступает на выход 28. Если обршцение осуществляется к одному из двух слов, содержащему ошибки, то с соответствующего блока 2 или 3 считывается единица (признак ошибки), которая стробирует коммутатор 4, и из регистра 17 соот- петствуюиц1й бант (синдром ошибки) поступает на другие входы формирователей 8, исправляя ощибки в соответствующих разрядах.

Таким образом, обеспечивается коррекция информации при использовании кода Файра.

Формула изобретения

Устройство для обнаружения и коррекции ошибок, содержащее буферный блок памяти, блок обнаружения ошибок блок памяти адресов ошибок, первый коммутатор, формирователи четности, выходы которых являются информационными выходами устройства, причем группы выходов блока обнаружения оши бок соединены с адресными входами блока памяти адресов ошибок, выходы первого коммутатора подключены к одним из входов формирователей четности, другие входы которых соединены с выходами буферного блока памяти, вход записи/чтения которого является входом управления режима и работы устройства, отличающееся тем, что, с целью повышения точности обнаружения и коррекции ошибок путем применения кода Файра, в него введены второй и третий коммутато ры, блок выбора адреса, формирователь импульсов, регистр сдвига, счетчик группа элементов И, формирователь сигналов обращения, первый и второй блоки памяти ошибочных байтов, первый и второй элементы ИЛИ, триггер, генератор тактовых импульсов, элемент НЕ, элемент И и преобра зователь последовательного кода в параллельный, выходы которого подключены к информационным входам буферного блока памяти, адресные входы которого и одни из информационных входов второго и третьего коммутаторов соединены с выходами блока выбора адреса, одни из адресных входов

-

10

15

20

30

35

40

25 55

45

50

которого подключены к выходам счетчика и одним из тактовых входов формирователя сигналов обращения, вьгход ко торого соединен с первым входом второго элемента ИЛИ и входом обращения буферного блока памяти, вход записи/чтения которого подключен к входам записи/чтения блока выбора адреса, формирователя сигналов обращения, первого и второго блоков памяти ошибочных байтов, первый выход блока обнаружения ошибок соединен с входом формирователя импульсов, выход которого подключен к входу стробирования блока памяти адресов ошибок, входам управления второго и третьего коммутаторов, второму входу второго элемента ИЛИ и информационным входам первого и второго блоков памяти ошибочных байтов, адресные входы кото- рьк соединены соответственно с выходами второго и третьего коммутаторов, другие информационные входы которых подключены соответственно к выходам первой и второй групп блока памяти, адресов ошибок, выходы третьей группы которого соединены с первыми входами элементов И группы, выходы которых подключены к информационным входам регистра сдвига, выходы первой и второй групп которог о соединены с информационными входами первого коммутатора, первый и второй управляющие входы которого подключены соответственно к выходам первого и второго блоков памяти ошибочных байтов, входы обращения которых соединены с выходом второго элемента ИЛИ, вторые входы элементов И группы подключены к второму выходу блока обнаружения ошибок, выходы с третьего по пятый которого соединены соответственно с тактовым входом регистра сдвига, с входом синхронной установки в 1 триггера, входом элемента НЕ и с входом запуска генератора тактовых импульсов, выход которого подключен к первому входу элемента И и входу синхронизации триггера, вход синхронной установки в О и прямой выход которого соединены соответственно с выходом элемента НЕ и вторым входом элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого подключен к тактовому входу блока обнаружения ошибок, информационный вход которого и информационный вход преобразователя последовательного кода в параллельный объединены и являются информационным входом устройства, счетный вход счетчика, другой тактовый вход формирователя сигналов обращения, тактовый вход блока выбора адресов и преобразователя последовательного кода в параллельный и второй вход первого элемента ИЛИ объединены и являются тактовым входом устройства, установоч2«

ные входы счетчика блока выбора адресов, блока обнар жения ошибок и регистра сдвига объединены и являются входом начальной установки устройства, адресными входами которого являются другие адресные входы блока выбора адресов , вход запуска форнирователя сигналов обращения яшляется входом обращения устройства.

| Хетагуров Я.Д., Руднев 10.fl | |||

| Повышение надежности запоминаюиигх устройств методами избыточного кодирования | |||

| М.: Энергия, 1974, с | |||

| Аппарат, предназначенный для летания | 0 |

|

SU76A1 |

| Зарубежная ралиоэлектроника, 1985, К 7, с | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-02-07—Публикация

1986-06-30—Подача