oZ2

а &

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372366A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Устройство для коррекции ошибок в блоках памяти с последовательным доступом | 1987 |

|

SU1510014A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1989 |

|

SU1698907A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

Изобретение относится к вычислительной технике, а именно к системам коррекции опптбок в каналах передачи блоков информации в последовательном коде, например при считывании информации с накопителем на магнитных лентах или магнитных дисках, и может быть использовано, в частности, для коррекщш информации, считьшаемой с ЗУ на цилиндрических магнитных доменах. .Целью изобретения является повышение точности обнаружения и исправ

MZ

лення ouni6oK путем использования кода Файра, Устройство содержит буферный блок 1 памяти, блок 2 выбора адреса, форьпфователь 3 сигнала обращения, счетчик 4, преобразователь 5 последовательного кода в параллель- ньп1, блок 6 обнаружения ошибок, формирователи 9, 10 импульсов, элемент И-НЕ 11, элемент ШШ-НЕ 12, элемент ИЛИ 13, коммл таторы 14, 15, регистр 16, блок управления 17, а также блок 7 памяти адресов ооп-гбок и блок 8 памяти признаков ошибок, выполненные из блоков постоянной памяти. Устройство обеспечивает обнаружение и коррекцию ошибок в информации, поступаю- :(сй 11 иос.кедовательном коде на вход

.

1

Изобретение относится к вычисли- i GjibHoit технике, а именно к системам коррекции о1яибок в каналах передачи блоков информацп-1 в последовательном .:оде, например при считьшании инфор- мации с накопителей на. магнитных лентах или магнитн 1х дисков, и может 6t,iTb использслано, в часттюсти, для KoppcKjrjiK пифорл ации. Считываемой с ЗУ на цилиндрических маггапных доменах .

Целью изобретения является повьше ние точности обнар лсерпш и исправления ошибок путем использования кода t aiipa.

На фиг, 1 представлена функционалная схема предлагаемого устройства и наиболее предпочтлтельного варианта цыполнепия блока запуска; на фиг. 2- ,7 - функциональные cxeivib наиболее Н7)едп.1 ;тительных вариантов выполнения соответственно блока обнаружения ошибок, блока выбора адреса, форми- .)оватп:1я сигнала обращения, блока памяти адресов ошибок, блока памяти призпак. ошибок и блока управления.

Предлаг аемое устройство содержит (фнг.1) буферШ:.м блок 1 памяти, блок 2 выбора адреса, формирователь 3 сигнала обращешгя, счетчгас 4, преобразователь 5 последовательного кода в параллельньпЧ, блок 6 обнаружения ошибок, блок 7 адресов ошибок

23 преобразователя 5, причем применение кода Файра позволяет при меньшем количестве контрольных разрядов исправлять пакеты ошибок большей длины, чем при применении кода БЧХ или кода Рида-Соломона. С выходов преобразователя 5 информация записывается в блок 1 байтами. Блок 6 позволяет выявлять признак ошибки и все необходимые данные для определения адреса ошибки с помощью блока 7. Блок 8 определяет по признаку ошибки номера ошибочных разрядов, которые поступают в формирователи 18 четности, где производится коррекция информации, считанной из блока 1 по определенному в блоке 7 адресу. 7 ил.

)0

15

5 ,

блок 8 памяти признаков ошибок, пер- вьй 9 и второй 10 формирователи импульсов, элемент И-НЕ 11, элемент ИЛИ-НЕ 12, элемент ИЛИ 13, первый 14 и второй 15 коммутаторы, регистр 16, блок 17 управления, формирователи 18 четности, вход 19 начальной установки, адресные входы 20, вход 21 управ- jiemiH режимом, вход 22 обращения, информационный вход 23, информационные выходы 24, первый 25 и второй 26 тактовые входы, выход 27 наличия ошибки и выход 28 наличия корректируемой ошибки.

На фиг. 1 изображен также блок 29 запуска, содержащий генератор 30 импульсов, триггер 31, элемент 32 и элемент НЕ 33.

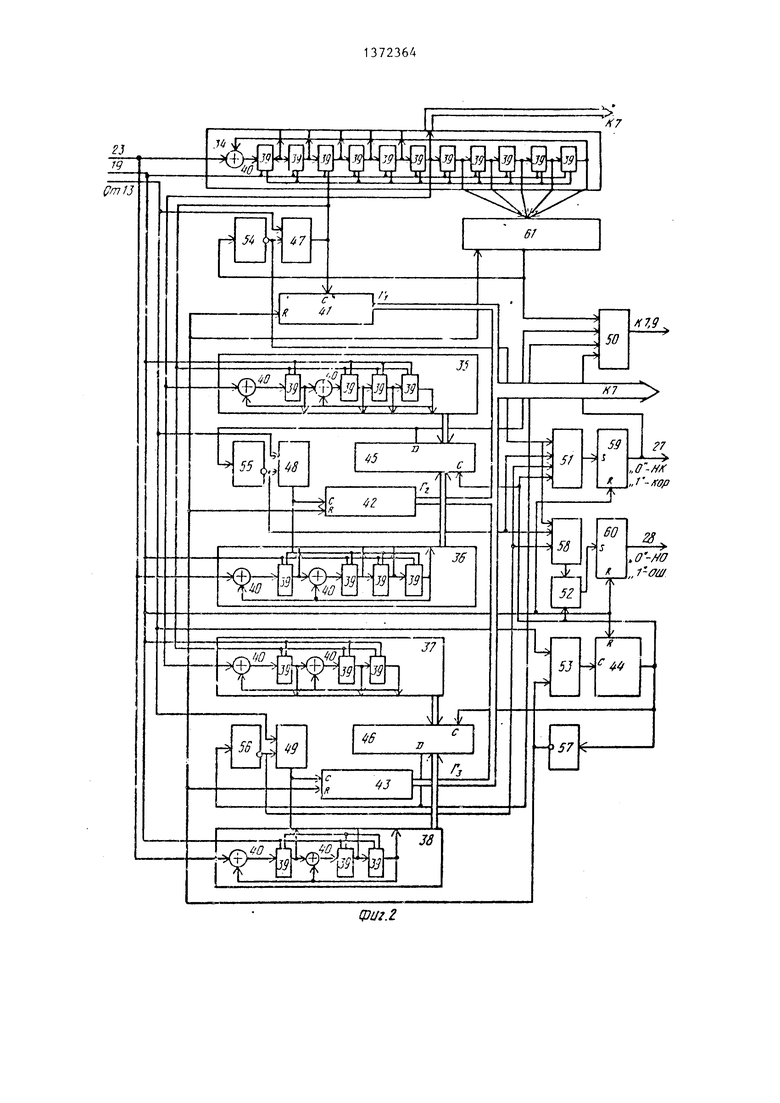

Блок 6 обнаружения ошибок содержит (фиг.2) регистры 34-38,каждый из которых состоит из триггеров 39 и формирователей 40 четности,счетчики 41-44, схемы 45 и 46 сравнения, элементы И 47-53, элементы НЕ 54-57, элементы ИЛИ 58, триггеры 59 и 60 и элемент ШШ-НЕ 61.

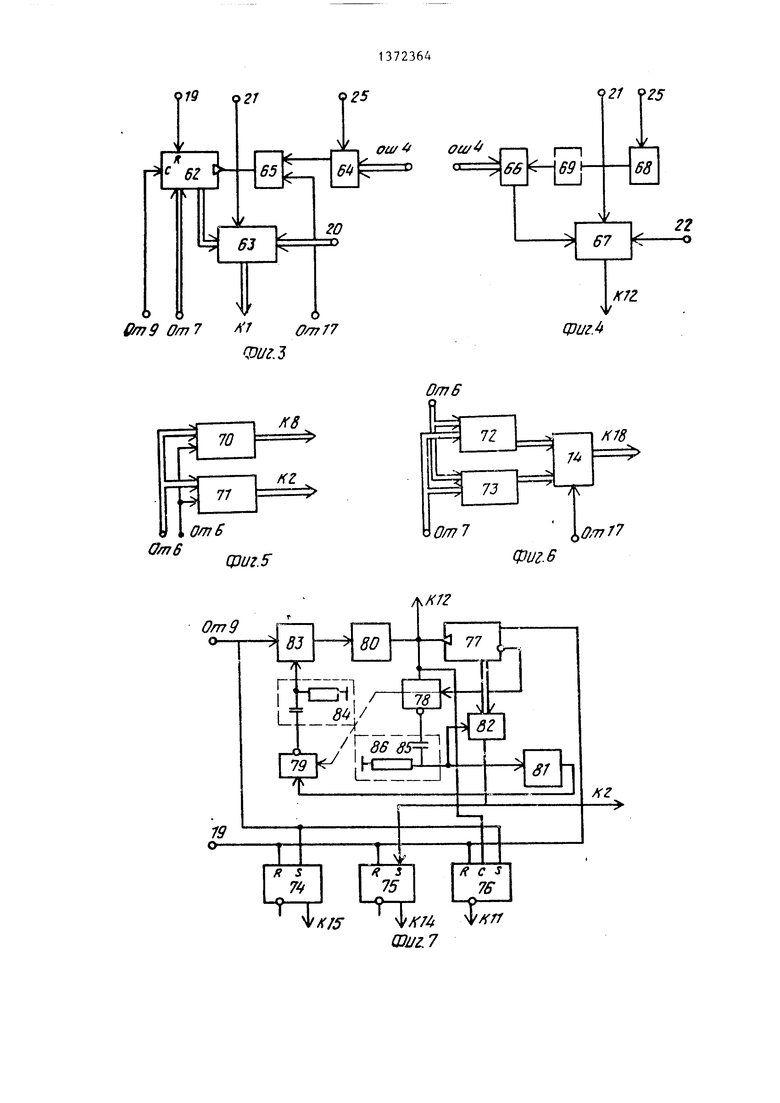

Блок 2 выбора адреса содержит (фиг.З) счетчик 62, коммутатор 63, элемент И 64 и элемент ИЛИ 65.

Формирователь 3 сигнала обращения содержит (фиг.4) элемент И 66, коммутатор 67, элемент 8 задержки и формирователь 69 сигналов.

3

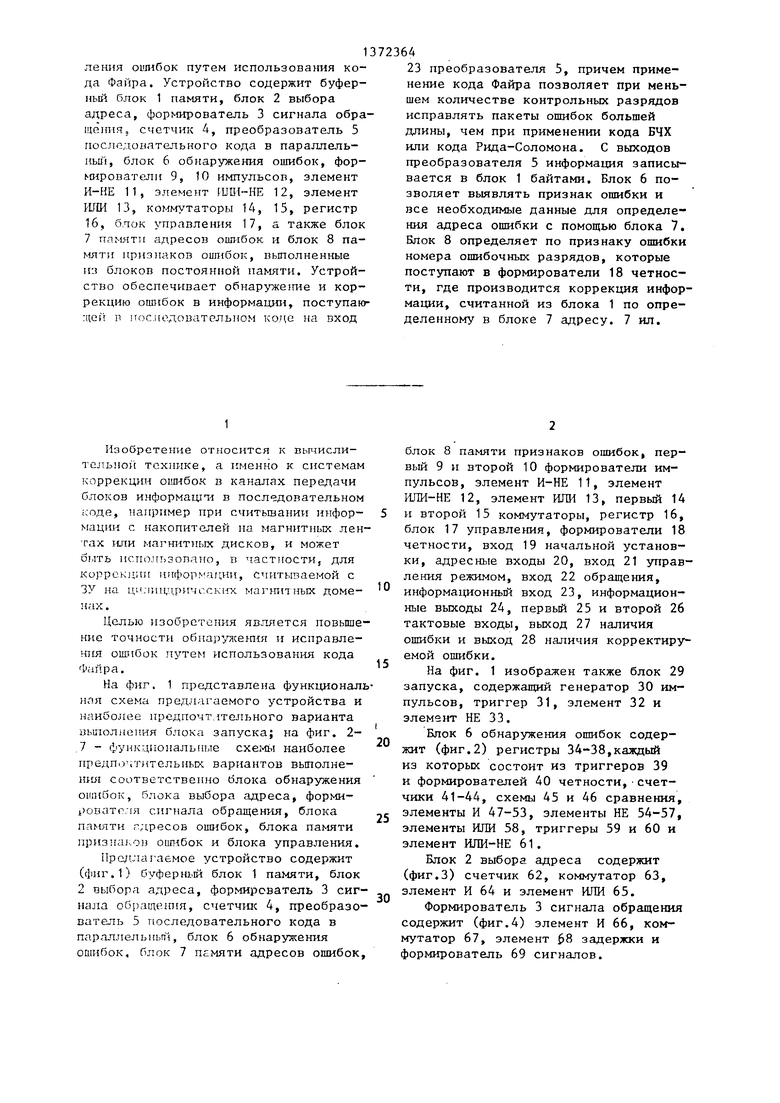

Блок 7 памяти адресов ошибок содержит (фиг.5) блоки 70 и 71 постоя ной памяти.

Блок 8 памяти признаков ошибок сдержит (фиг.6) блоки 72 и 73 постоянной памяти.

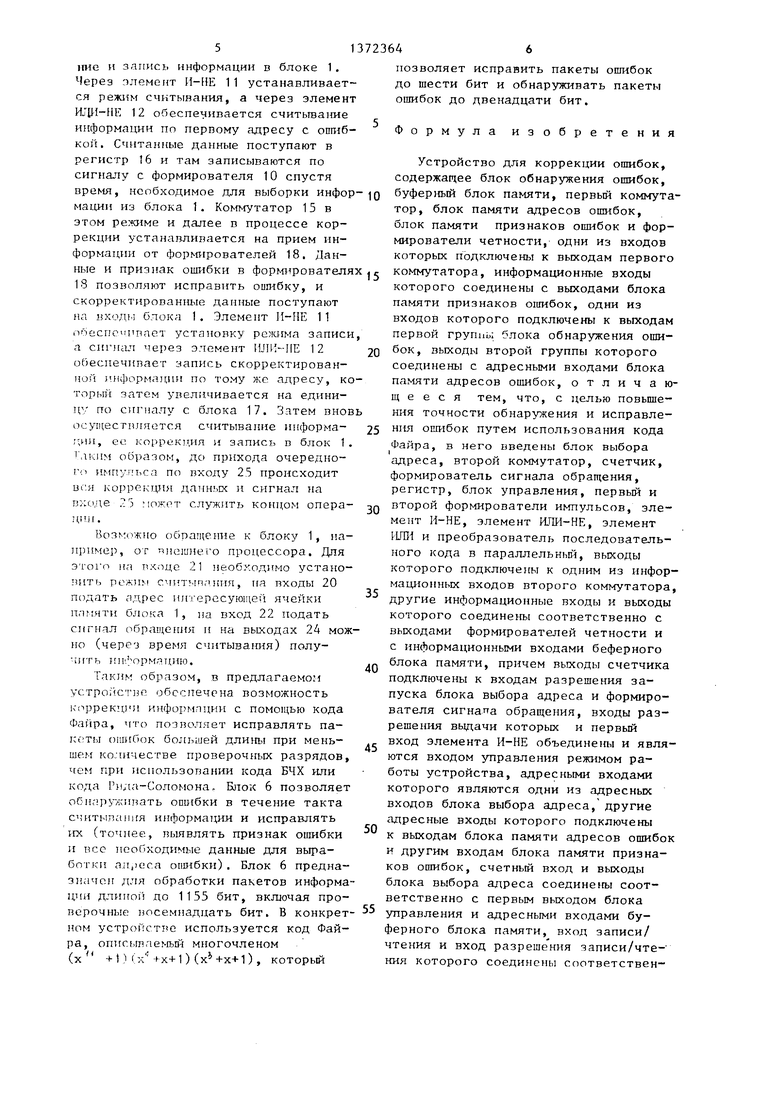

Блок 17 управления (фиг.7) содержит на триггерах 74-76 счетчик 77, элементы И-ilE 78 и 79, формировател 80 и 81 импульсов, дешифратор 82, элемент Hltti 83, RC-цепочка 84, конденсатор 85 и резистор 86.

Предлагаемое устройство работает следующим образом.

По входу 19 (фиг.1) осуществляется начальная установка соответствующих блоков устройства. На вход 23 подают группу разрядов информации (совместно с проверочнъми разрядами сопровождаемую тактовь ш сипишами по входу 25 (для ДМ/; ЗУ тактопая частота около 100 кГц). Преобразователь 5 осу1(ес ГБЛяет иреобразовапие последоват и;ьиого кодо и парал:лель- ньй по бит. lia вход 21 подаю сигнал згшиси И1 формации, лслсдстви чего на втлхол.е улемента 1 1 присутствует С 1гил1 релагма записи iiiiCic мации в 1, иагфимср лог. О, причем на другом входе элембМ1та И-НЕ 11 в исход)1ом состоянии также лог. 1. Счетчик 4 оПеспечш-асг счет импул1,соп с входа 25, причем после имиульсл на виходе счетчика 4 будет p,;;ipeiiiaioiuvifi потсл- хдаал, o6eci e iiiB;ii-jiHPii срабатьшаш е блока 2 и форг Ирователя 3. } промежутке jiOcijMi.iM ir де1 иты;ч такто выми импульсами происход1 Г строОнро вание загп-1си -в блок 1, а после девятого происходит запись нового адреса в счетчик 62 (начальный адрес нулевой). Исходное состояние блока 17 таково, что комт-гутатор 14 включе на пропуск и 1формадии от блока 72, коммутатор 15 включен на пропуск информации от преобразователя 5, на элемент 1-ШИ-П : 12 пост -ттает нулевой сигнал, на блок 2 поступает нулевой сигнал с выхода блока 17, а на элемент И-НЕ 11 поступает единичньш сигнал. Таким образом, по прошестви определенного количества тактов, полезная информация записьшается в бл 1 в виде байтов информации. Одновременно в блоке 6 происходит обнаружение ошибки. На выходах 27 и 28 появляются сигналы, свидетельствую

0

5

ь

0

0

5

5

0

5

щие о наличии или отсутствии ошибок в считанной информации. При этом, если на выходе 27 имеется лог.О - нет , а если лог. 1 - есть ошибка; если на выходе 28 лог.О - некорректируемая ошибка, а если лог. - корректируемая ошибка. Дальнейшая работа устройства может быть инициирована блоком 29, KOTopbtfi вырабатывает последовательность тактовой частоты, достаточной для срабатьша- ния элементов блока 6, например, до 1 МГц.

В зависимости от состояния выходов 27 и 28 возможны следующие режи- мм работы ycTpoi icTBa.

На выходе 27 лог, О. Это означает, jTo в принятой информации оши- 6(jK нет и она может быть ис11ол1 зова- на.

На ц.гходс 27 лог. 1, а па выходе 28 лог. О. Это означает, что в п;)11пятой мпйормлдии иг-к-ется нскор- ректируспля опибка кратностью от семи 71,о дпел П/тати бит и 1 нформадия iic . моясет быть использо}1;111а,

ll i jt n-r.ojie 27 и на выходе 28 лог. Г . Эт1 1 означает, что в принятой nuiiii ivuu jii и.- сется ошибка и опа мо- я;ет Гилтт. скорректирована. Лля этого па вход 26 подают тактовую частоту, нслб;пств1 е чего через несколько тактов на входах блока 8-вьр:одах блока 6 по япитг.я признак ог-шбки, а информация, достаточная для определения адреса ouniOiai, - на выходах блока 6, под- ключен} ых к блоку 7, и сигнал ошибки - на пходе блока 9. Из блока 7 считывается адрес первого ошибочного брйта (всего может быть не более двух о111ибоч ьк байтов), который поступает и 6jfoK 8 и в блок 2, где по задержанному сигнаичу с выхода формирователя 9 записывается но параллельному входу н счзтчп 62. Одновременно блок 8 осу1цествляет вьгработку номеров оипюо- чных рг1зрядов, которые по выходам накопителе 72 и 73 поступают на соответствующие зходы KOMNryTaTopa 14, а поскольку последний открыт для приема информации от блока 72, то признак ошибки первого ошибочного слова поступает на соответствующие входы форш1рователей 18.В это время блок 17 организует работу устройства так, что последовательно по каждому из двух последовательных адресов с оп ибкам производится считыва)Ше и заггись информации в блоке 1 . Через ;1лемсит И-НЕ 1 1 устанавливается считывания, а через элемент 12 обеспечивается считьшание информации по первому адресу с опшб- Koit. Считанные данные поступают в регистр 16 и там записываются по сигналу с формирователя 10 спустя

тор, блок памяти адресов ошибок, блок памяти признаков ошибок и формирователи четности, одни из входов которых подключены к выходам первого

18 позволяют исправить оишбку, и скорректированные данные поступают на входы блока 1. Элемент И-ИЕ 11 (пбесг счппает установку режима записи, а сиг)1ал через элемент lUIH-IIE 12 20 ойеспечипает запись скорректированной информации по тому же адресу, ко- TvOpiiiH затем увеличивается на единицу гто сигналу с блока 17. Затем вновь

25

время, необходимое для выборки инфор- ю буферный блок памяти, первый коммута- мации из блока 1. Коьп гутатор 15 в этом режиме и далее в процессе коррекции устанавливается на прием информации от форшгрователей 18. Данные и ошибки в формирователяхjг коммутатора, информационные входы

которого соединены с выходами блока памяти признаков ошибок, одни из входов которого подключены к выходам первой группы блока обнаружения ошибок, выходы второй группы которого соединены с адресными входами блока памяти адресов ошибок, отличающееся тем, что, с целью повьш1е- ния точности обнаружения и исправле- Н1Ш ошибок путем использования кода Файра, в него введены блок выбора адреса, второй коммутатор, счетчик, формирователь сигнала обращения, регистр, блок управления, первый и 2Q второй формирователи импульсов, элемент И-НЕ, элемент ИЛИ-НЕ, элемент ИЛИ и преобразователь последовательного кода в параллельнь&1, выходы которого подключены к одним из информационных входов второго комт-гутатора, другие информационные входы и выходы которого соединены соответственно с выходами формирователей четности и с информационными входами беферного блока памяти, причем выходы счетчика подключены к входам разрешения запуска блока выбора адреса и формирователя сигнала обращения, входы разрешения выдачи которых и первый вход элемента И-НЕ объединены и являются входом управления режимом работы устройства, адресными входами которого являются одни из адресных входов блока выбора адреса, другие адресные входы которого подключены к выходам блока памяти адресов ошибок и другим входам блока памяти признаков опшбок, счетный вход и выходы блока выбора адреса coeдинe tы соответственно с первым выходом блока управления и адресными входами буферного блока памяти, вход записи/ чтения и вход разрешения записи/чте- НИН которого соединены соответственосущестнияется считывание информа- ;;ии, ео коррек тия и запись в блок 1 . Тлкнм об эазом, до прихода очередно- Г .1 импуг 1,са по входу 25 происходит вся 1соррекция данных и сигнал на пко, 25 может служить концом операции .

Bo3N;(,r«Ho обращение к блоку 1, например, от neiiDiero процессора. Для этого на Т1ХОЦС 21 iie-обходимо устано- режим считмп. птя, на входы 20 П(1дать пдрес интересующей ячейки ппмяти блока 1, на вход 22 подать сигнал обращения и на выходах 24 можно (через время считывания) получить I п 1. ;ормз цлю.

Таким образом, в предлагаемом устройс гнс обсс1течена возможность 1чоррекц Ч1 информлции с помощью кода Файра, что позволяет исправлять па- icf Tbi ошибок длинь при меньшем количестве проверочных разрядов, чем при использопании кода БЧХ или кода Ри;1а-Соломона. Бло; 6 позволяет )л пать опшбки в течение такта считывания информации и исправлять trx (точнее, выявлять признак ошибки и псе необходимые данные для вьфа- ботки алрсса oiiBi6KH) . Блок 6 предназначен для обработки пакетов информации длино11 до 1155 бит, вклJoчaя про35

40

45

50

верочные носемнадцать бит. В конкрет ном устройстт е используется код Файра, onTtcbinaeNan-i многочленом (х -f )) () (), который

- 55

позволяет исправить пакеты ошибок до шести бит и обнаруживать пакеты ошибок до двенадцати бит.

Формула изобретения

Устройство для коррекции ошибок, содержащее блок обнаружения ошибок.

тор, блок памяти адресов ошибок, блок памяти признаков ошибок и формирователи четности, одни из входов которых подключены к выходам первого

буферный блок памяти, первый коммута- коммутатора, информационные входы

2Q

- 55

но с выходом элемента И-НЕ и с выходом элемента ИЛИ-НЕ и входом второго формирователя импульсов, выход которого подключен к управляющему входу регистра, входы и выходы которого соединены соответственно с выходами буферного блока памяти и с другими входами формирователей четности, управляющий вход второго коммутато- pa подключен к второму выходу блока управления, третий и четвертый выходы которого соединены соответственно с вторым входом элемента И-НЕ и с первым входом элемента ИЛИ-НЕ, второй вход которого подключен к выходу формирователя сигнала обращеьшя вход обращения которого является входом обращения устройства, а вход запуска соединен со счетньм входом счетчика, входом запуска блока выбора адреса, входом синхронизации преобразователя последовательного кода в параллельньш, первым входом элемента ИЛИ и является первым такто вым входом устройства, вторым тактовым входом которого является второй

вход элемента ИЛИ, выход которого подключен к входу запуска блока обнаружения опшбок, первьй выход которого подключен к входу обращения блока памяти адресов ошибок и входу первого формирователя импульсов, выход которого соединен с входами синхронизации блока управления и блока выбора адреса, вход установки которого подключен к входу установки счетчика, блока управления, блока обнаружения ошибок и является входом начальной установки устройства, информационными выходагш которого являются выходы буферного блока памяти, входы данных преобразователя последовательного кода в параллельный и блока обнаружения ошибок объединены и являются информационным входом устройства, пятый выход блока управления подключен к управляющему входу первого коммутатора, второй и третий выходы блока обнаружения ошибок являются соответственно выходом наличия ошибки и выходом наличия корректируемой ошибки устройства.

2J

QmT3

| Хетагуров Я.А., Руднев Ю.П | |||

| Повышение надежности цифровых уст- - ройств методами избыточного кодирования | |||

| М.: Энергия, 1974, с.71 | |||

| Зарубежная радиоэлектроника, 1985, № 7, с.11, рис | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-02-07—Публикация

1986-06-30—Подача