ff 18

(Л

оо

1чЭ

оэ

О5

ел

паков ошибок, формирователи 5 четности , группу коммутаторов 6, первый 7 и второй 8 коммутаторы, блок 9 сравнения, блок 10 синхронизации, регистр 11 сдвига, счетчик 12, формирователь 13 импульсов, элемент ИЛИ 1А. Информация в параллельном коде (байтами) записьгаается через входы 21 в буферньй блок 1 памяти и в регистр 11 сдвига, из которого каждый байт данных сдвигается и поступает

в блок 2 обнаружения ошибок, который вьфабатывает с использованием кода Файра все данные, необходимые для определения адреса и характера ошибки. Коррекция информации, считанной из буферного блока 1 памяти по определенному адресу ошибки, выполняется формирователями 5 четности. Сигналы на выходах 23 и 24 соответствуют наличию ошибки и наличию корректируемой ошибки в информации. 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1372364A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372366A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

Изобретение относится к вычислительной технике,а именно к устройствам для коррекции информации,и может быть применено для исправления пакетов ошибок, возникающих при передаче блоков информации из внешних запоминающих устройств с параллельным считыванием, таких, как накопители на магнитных барабанах и цилиндрических магнитимых доменах. Целью изобретения является повышение быстродействия устройства. Устройство содержит буферный блок 1 памяти, блок 2 обнаружегшя ошибок, блок 3 памяти адресов ошибок, блок 4 памяти приз

Изобретение относится к вычислительной технике, а именно к устройствам для коррекции информации, и может быть использовано для исправления пакетов ошибок, возникающих при передаче блоков информации из внешних запоминаюп1их устройств с параллельным считыванием, таких, как накопители на магнитных барабанах, цилиндрических магнитных доменах.

Целью изобретения является повьш1е нле быстродействия устройства инфор- мац1-ш.

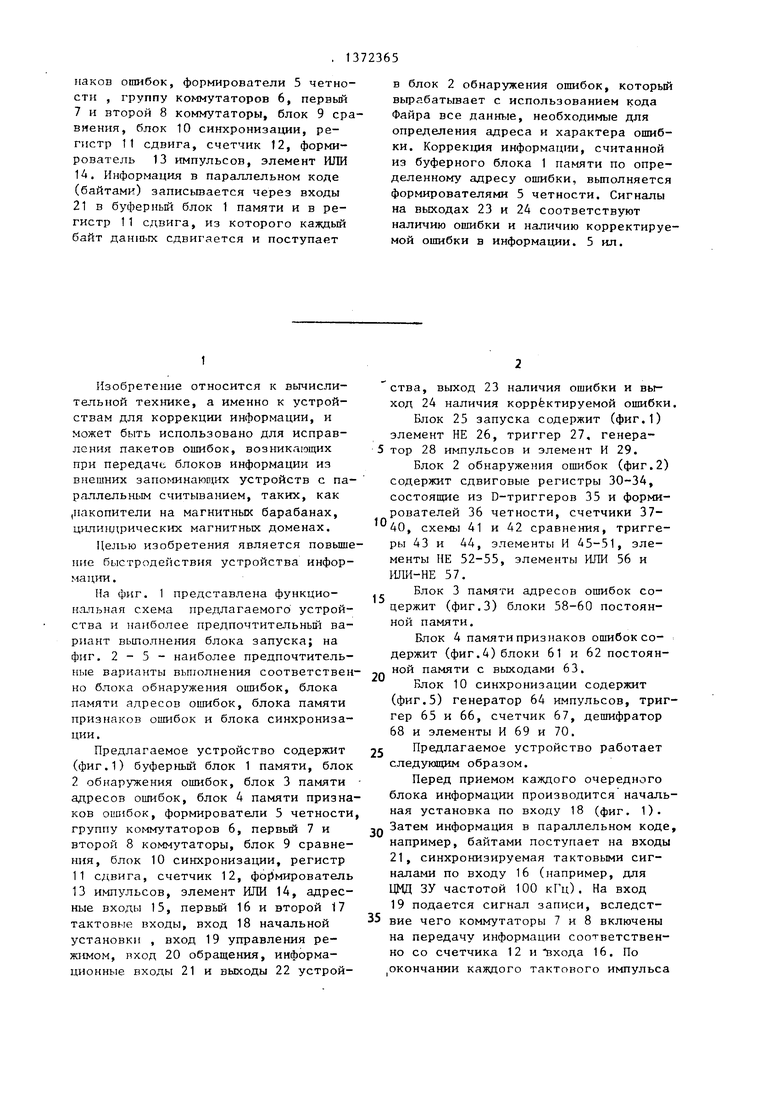

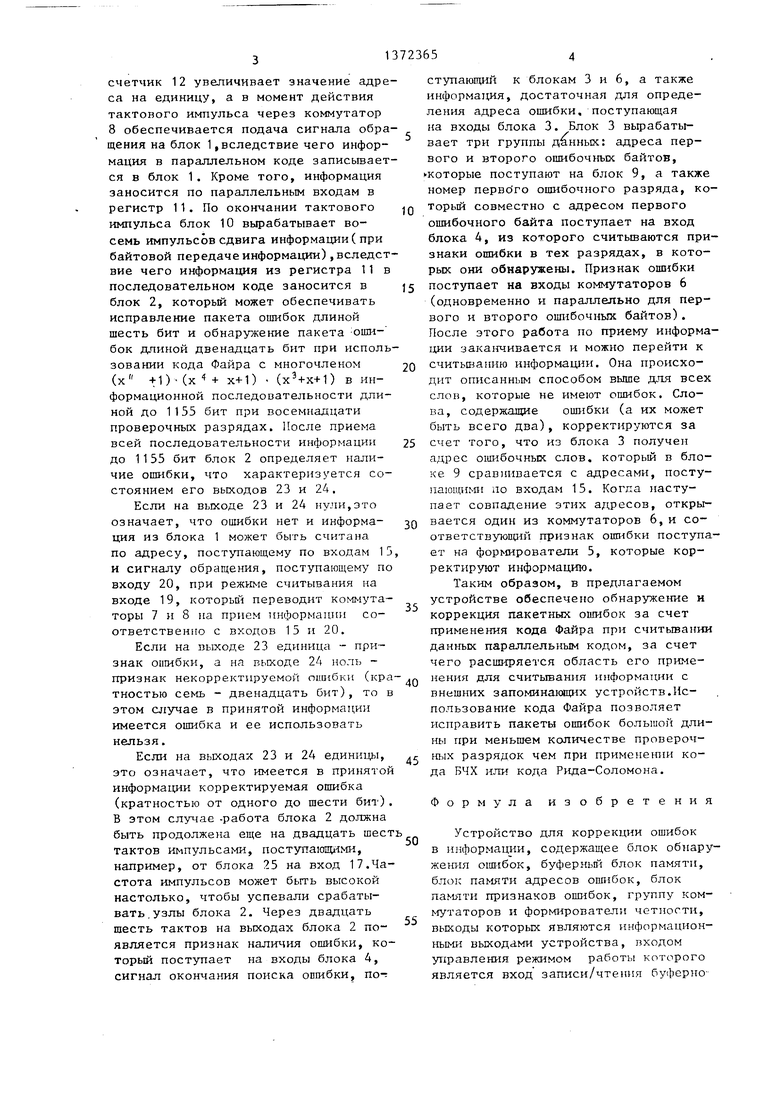

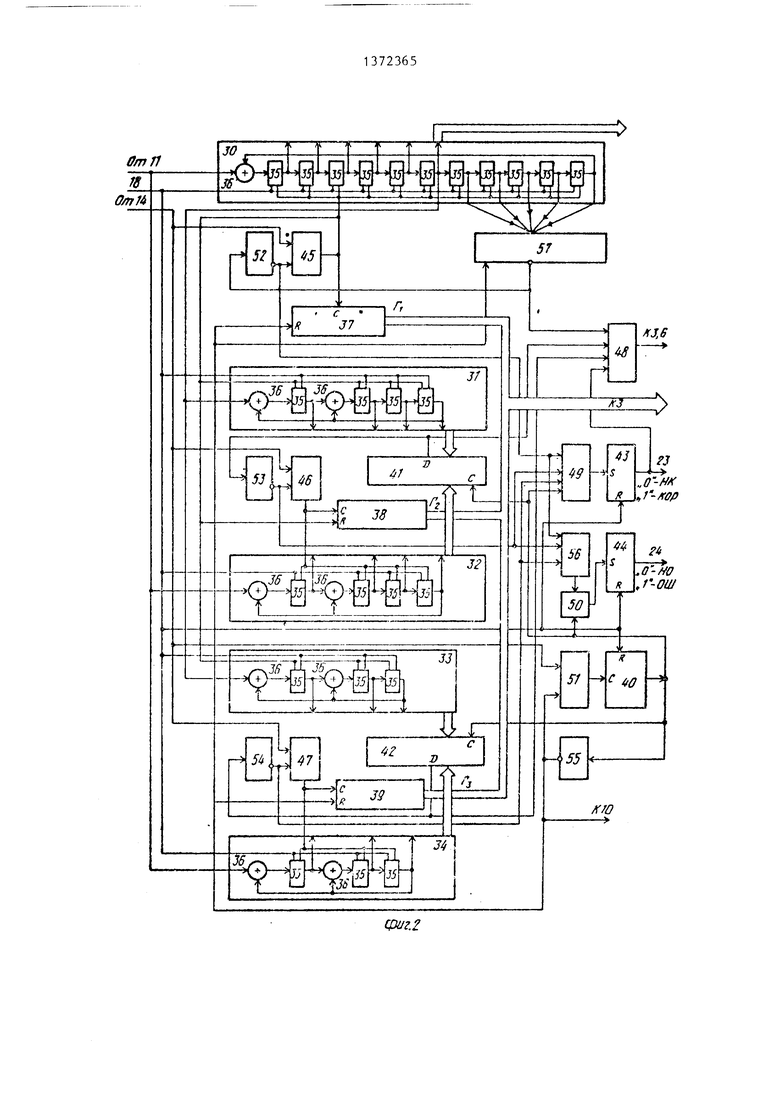

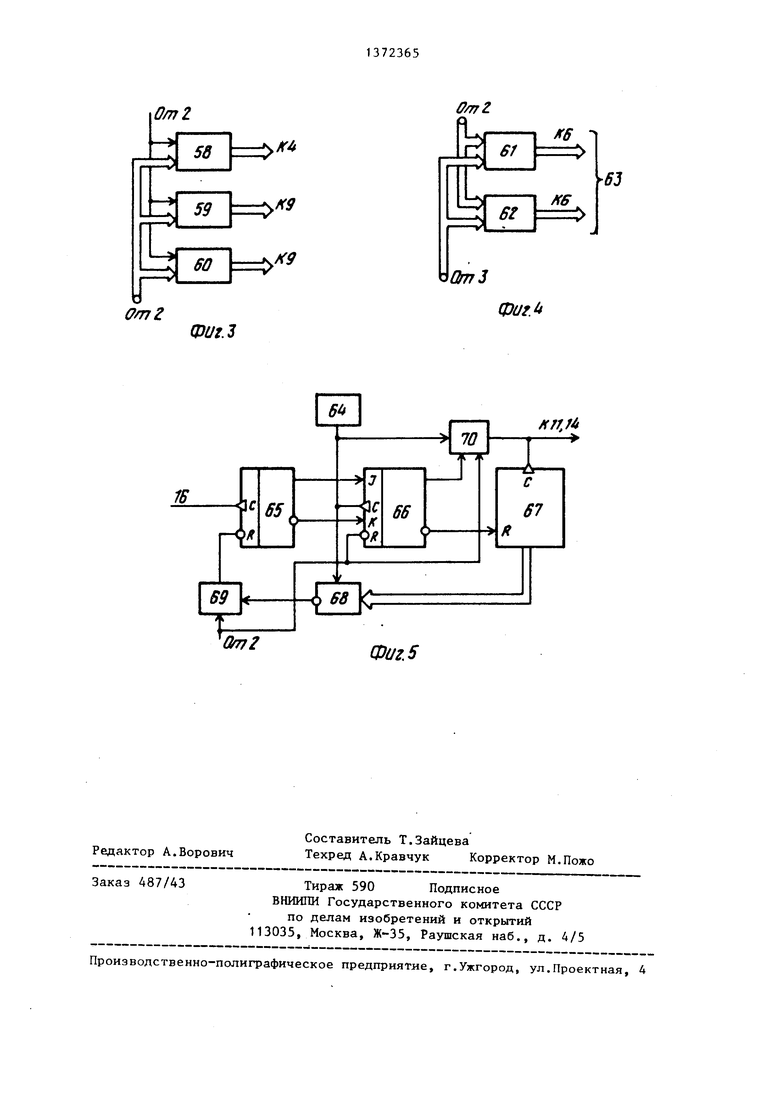

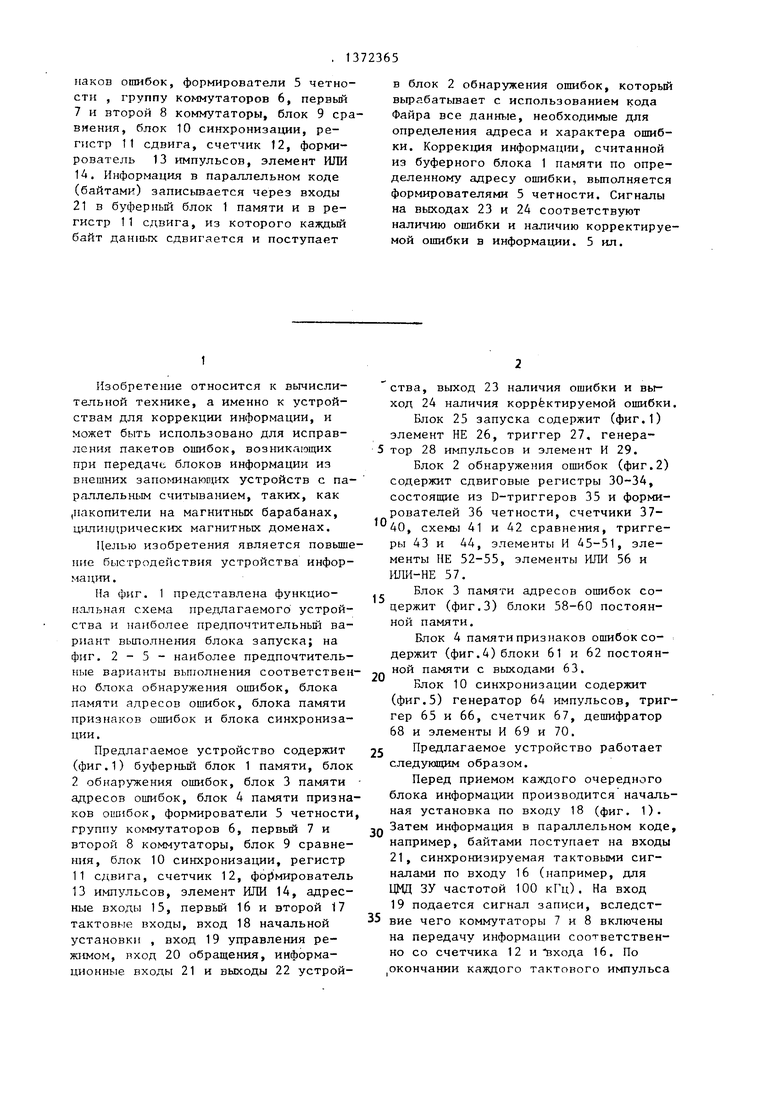

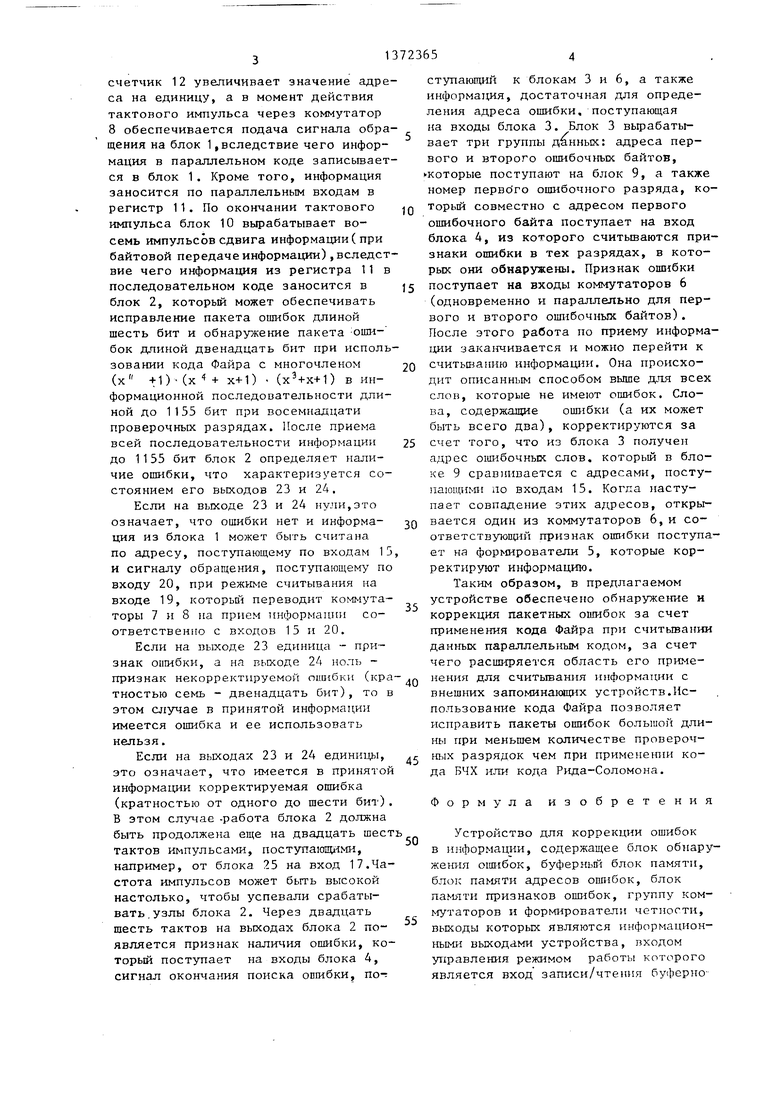

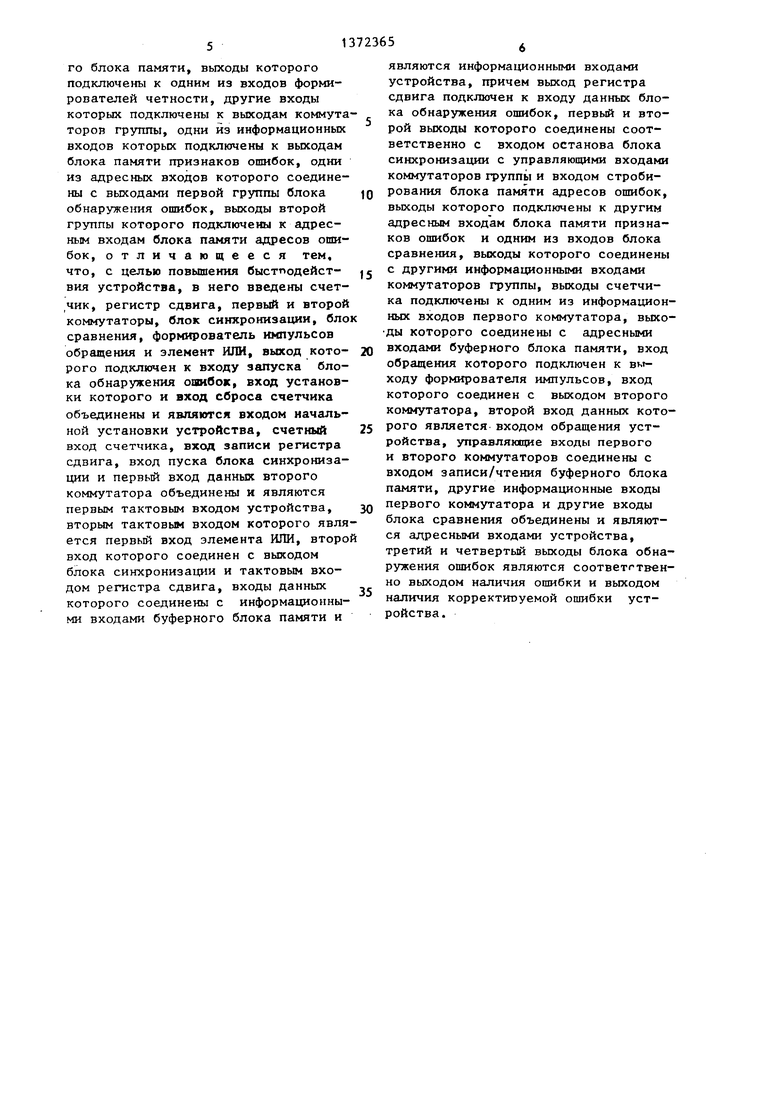

На фиг. 1 представлена функциональная схема предлагаемого устройства и }1аиболее предпочтительны вариант выполнения блока запуска; на фиг. 2 - 5 - наиболее предпочтительные варианты вьпюлнения соответственно блока обнаружения ошибок, блока памяти адресов ошибок, блока памяти признаков ошибок и блока синхронизации.

Предлагаемое устройство содержит (фиг.1) буферный блок 1 памяти, блок 2 обнаружения ошибок, блок 3 памяти адресов ошибок, блок 4 памяти признаков оишбок, формирователи 5 четности группу коммутаторов 6, первый 7 и второй 8 коммутаторы, блок 9 сравнения, блок 10 синхронизации, регистр 11 сдвига, счетчик 12, фо1)мирователь 13 импульсов, элемент ИЖ 14, адресные входы 15, первый 16 и второй 17 тактовые входы, вход 18 начальной установки , вход 19 управления режимом, вход 20 обращения, информационные входы 21 и выходы 22 устрой10,

5

ства, выход 23 наличия ошибки и выход 24 наличия корректируемой ошибки.

Блок 25 запуска содержит (фиг.1) элемент НЕ 26, триггер 27, генера- 5 тор 28 импульсов и элемент И 29.

Блок 2 обнаружения ошибок (фиг.2) содержит сдвиговые регистры 30-34, состоящие из D-триггеров 35 и формирователей 36 четности, счетчики 37- 40, схемы 41 и 42 сравнения, триггеры 43 и 44, элементы И 45-51, элементы НЕ 52-55, элементы ИЛИ 56 и ИЛИ-НЕ 57.

Блок 3 памяти адресов ошибок со- цержит (фиг.З) блоки 58-60 постоянной памяти.

Блок 4 памяти признаков ошибок содержит (фиг.4)блоки 61 и 62 постоянной памяти с выходами 63.

Блок 10 синхронизации содержит (фиг.5) генератор 64 импульсов, триггер 65 и 66, счетчик 67, дешифратор 68 и элементы И 69 и 70. 5 Предлагаемое устройство работает следующим образом.

Перед приемом каждого очередного блока информации производится начальная установка по входу 18 (фиг. 1). Затем информация в параллельном коде, например, байтами поступает на входы 21, синхронизируемая тактовыми сигналами по входу 16 (например, для ЦМД ЗУ частотой 100 кГц). На вход 19 подается сигнал записи, вследст- 5 вие чего коммутаторы 7 и 8 включены на передачу информации соответственно со счетчика 12 и входа 16. По окончании каждого тактового импульса

0

счетчик 12 увеличивает значение адреса на единицу, а в момент действия тактового импульса через коммутатор 8 обеспечивается подача сигнала обращения на блок 1, вследствие чего информация в параллельном коде записьтает ся в блок 1. Кроме того, информация заносится по параллельным входам в регистр 11. По окончании тактового импульса блок 10 вырабатывает восемь импульсов сдвига информации ( при байтовой передаче информации), вследствие чего информация из регистра 11 в последовательном коде заносится в блок 2, который может обеспечивать исправление пакета ошибок длиной шесть бит и обнаружение пакета оши- бок длиной двенадцать бит при использовании кода Файра с многочленом (х +1)-(х + х+1) . () в информационной последовательности длиной до 1155 бит при восемнадцати проверочных разрядах. После приема всей последовательности информации до 1155 бит блок 2 определяет наличие ошибки, что характеризуется состоянием его выходов 23 и 24,

Если на выходе 23 и 24 нули,это означает, что ошибки нет и информация из блока 1 может быть считана По адресу, поступаюш,ему по входам 15 и сигналу обращения, поступающему по входу 20, при режиме считывания на входе 19, которьй переводит коммутаторы 7 и 8 на прием информации соответственно с входов 15 и 20.

Если на выходе 23 единица - признак опибки, а на выходе 24 ноль - признак некорректируемой опшбкп (кратностью семь - двенадцать бит), то в этом случае в принятой информации имеется ошибка и ее использовать нельзя.

Если на выходах 23 и 24 единицы, это означает, что имеется в принятой информации корректируемая ошибка (кратностью от одного до шести бит). В этом случае -работа блока 2 должна быть продолжена еще на двадцать шест тактов импульсами, поступающими, например, от блока 25 на вход 17.Частота импульсов может быть высокой настолько, чтобы успевали срабатывать, узлы блока 2. Через двадцать шесть тактов на выходах блока 2 появляется признак наличия ошибки, который поступает на входы блока 4, сигнал окончания поиска опшбки, по

0

5

5 0

0

5

0

5

0

5

ступающий к блокам 3 и 6, а также информатщя, достаточная для определения адреса ошибки, поступающая на входы блока 3. Блок 3 вьфабаты- вает три группы данных: адреса первого и второго ошибочных байтов, ккоторые поступают на блок 9, а также номер перво го ошибочного разряда, который совместно с адресом первого ошибочного байта поступает на вход блока 4, из которого считьшаются признаки ошибки в тех разрядах, в которых они обнаружены. Признак ошибки поступает на входы коммутаторов 6 (одновременно и параллельно для первого и второго ошибочных бантов). После этого работа по приему информации заканчивается и можно перейти к считьшанию информации. Она происходит описанным способом выше для всех слов, которые не имеют ошибок. Слова, содержащие ошибки (а их может быть всего два), корректируются за счет того, что из блока 3 получен адрес ошибочных слов, который в блоке 9 сравнивается с адресами, поступающим по входам 15. Когда наступает совпадение этих адресов, открывается один из коммутаторов 6, и со- ответствуюп ий признак ошибки поступает на формирователи 5, которые корректируют информацию.

Таким образом, в предлагаемом устройстве обеспечено обнаружение и коррекция пакетных ошибок за счет применения кода Файра при считьгоа1тии данных параллельным кодом, за счет чего расширяется область его применения для считьшания информации с внешних запоминакш1их устройств.Использование кода Файра позволяет исправить пакеты ошибок большой длины при меньшем количестве проверочных разрядок чем при применении кода БЧХ или кода Рида-Соломона.

Формула изобретения

Устройство для коррекции ошибок в информации, содержащее блок обнаружения ошибок, буферньй блок памяти, блок памяти адресов ошибок, блок памяти признаков ошибок, группу коммутаторов и формирователи четности, выходы которых являются информационными выходами устройства, входом управления режимом работы которого является вход записи/чтения буферного блока памяти, выходы которого подключены к одним из входов формирователей четности, другие входы которых подключены к выходам коммута торов группы, одни из информационных входов которых подключены к выходам блока памяти признаков ошибок, одни из адресных входов которого соединены с выходами первой группы блока обнаружения ошибок, выходы второй группы которого подключены к адресным входам блока памяти адресов ошибок, отличающееся тем, что, с целью повышения быстподейст- ВИЯ устройства, в него введены счет- чик, регистр сдвига, первый и второй коммутаторы, блок синхронизации, бло сравнения, формирователь импульсов обращения и элемент ИЛИ, выход кото- рого подклкиен к входу запуска блока обнаружения ошибок, вход установки которого и вход сброса счетчика объединены и являются входом начальной установки устройства, счетный вход счетчика, вход записи регистра сдвига, вход пуска блока синхронизации и первый вход данных второго коммутатора объединены и являются первым тактовым входом устройства, вторым тактовым входом которого является первый вход элемента ИЛИ, второ вход которого соединен с выходом блока синхронизации и тактовым входом регистра сдвига, входы данных которого соединены с информационными входами буферного блока памяти и

являются информационными входами устройства, причем выход регистра сдвига подключен к входу данных блока обнаружения ошибок, первый и второй выходы которого соединены соответственно с входом останова блока синхронизации с управляющими входами коммутаторов группы и входом строби- рования блока памяти адресов ошибок, выходы которого подключены к другим адресным входам блока памяти признаков ошибок и одним из входов блока сравнения, выходы которого соединены с другими информационными входами коммутаторов группы, выходы счетчика подключены к одним из информационных входов первого коммутатора, выхо- ды которого соединены с адресными входами буферного блока памяти, вход обращения которого подключен к ходу формирователя импульсов, вход которого соединен с выходом второго коммутатора, второй вход данных которого является входом обращения устройства, управляющие входы первого и второго коммутаторов соединены с входом записи/чтения буферного блока памяти, другие информационные входы первого коммутатора и другие входы блока сравнения объединены и являются адресными входами устройства, третий и четвертый выходы блока обнаружения ошибок являются соответгтвен- но выходом наличия ошибки и выходом наличия корректируемой ошибки устройства.

ОтП

0/nJ

Q -Hff „f -W/}

От г

фиг.2

/fff

/(Б

S3

ОтЗ

Фиг.

| Хетагуров Я.А., Руднев Ю.П | |||

| Повышение надежности цифровых устройств методами избыточного кодирования, М.: Энергия, 1974, с.76 | |||

| Зарубежная радиоэлектроника, 1985, № 7, с.11, рис.4. |

Авторы

Даты

1988-02-07—Публикация

1986-06-30—Подача