Р

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для параллельной передачи информации | 1990 |

|

SU1795465A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ХАРТЛИ-ФУРЬЕ | 1999 |

|

RU2190874C2 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1304034A1 |

| Программируемый процессор спектральной обработки сигналов | 1978 |

|

SU744603A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1983 |

|

SU1124323A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1989 |

|

SU1691853A1 |

| Многоканальное устройство для быстрого преобразования Фурье с конвейерной обработкой операндов | 1984 |

|

SU1211752A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1264240A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях быстрого преобразования Фурье (БПФ) по основа сии г нию два, а также в системах переработки информации. Цель изобретения - повышение быстродействия устройства. Оперативное запоминающее устройство содержит адресный регистр 1. разделенный на старшую 2 и младшую 3 части, регистр 4 входных данных, блоки 5 преобразования адреса, адресные коммутаторы 6. коммутаторы 7 входных данных, накопители 8, коммутаторы 9 выходных данных, регистр 10 выходных данных, второй адресный регистр 11, разделенный на старшую 12 и младшую 13 части, триггэр 14 режима, бпок 15 формирования управляющих сигналов, конвейерный регистр 16, элементы И 17. 1 з.п.ф-лы, 3 ил., 1 табл.

о

4

Ю Ю

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях быстрого преобразования Фурье (БПФ) по основанию два, а также в системах переработки информации.

Цель изобретения - повышение быстродействия устройства.

На фиг. 1 приведено оперативное запоминающее устройство; на фиг. 2 - блок пре- образования адреса; на фиг. 3 - блок формирования управляющих сигналов.

При построении вычислителя БПФ по основанию два наибольшие трудности вызывает создание быстродействующей сие- темы памяти. При этом традиционное расслоение памяти на число страниц, равное степени двух, позволяющее быстро декодировать адреса, не обеспечивает бесконфликтного доступа по нескольким (в частности, двум) адресам при выполнении алгоритма БПФ по основанию два.

При выполнении элементарной операции БПФ Бабочки необходимо производить считывание из оперативного запоминающего устройства, а затем запись двух комплексных операндов, адреса которых отличаются на степень двух

Aj AI + 2k, где AI - адрес первого операнда;

AJ - адрес второго операнда;

k 0, 1,2.... logaN;

N - число точек преобразования.

Если разделить два указанных адреса на нечетное число, то полученные остатки не будут равны между собой:

At (А| + 2k) (mod М); М 3, 5, 7, так как 2k э4 0 (mod M).

Таким образом, если всю память разбить на нечетное число накопителей, ска- жем на 3, а при расшифровке адресов номер накопителя определять как остаток от деления каждого адреса на 3, то никогда не произойдет обращения к одному и тому же накопителю при выполнении элементарной операции БЛФ.

Адрес внутри накопителя можно определить как частное от деления адресов операндов на 3. Учитывая, однако, тот факт, что микросхемы полупроводниковой памяти имеют объем, равный степени двух, адрес внутри накопителя можно вычислять, отбрасывая один младший разряд логического адреса. При этом объем накопителя будет использоваться не полностью.

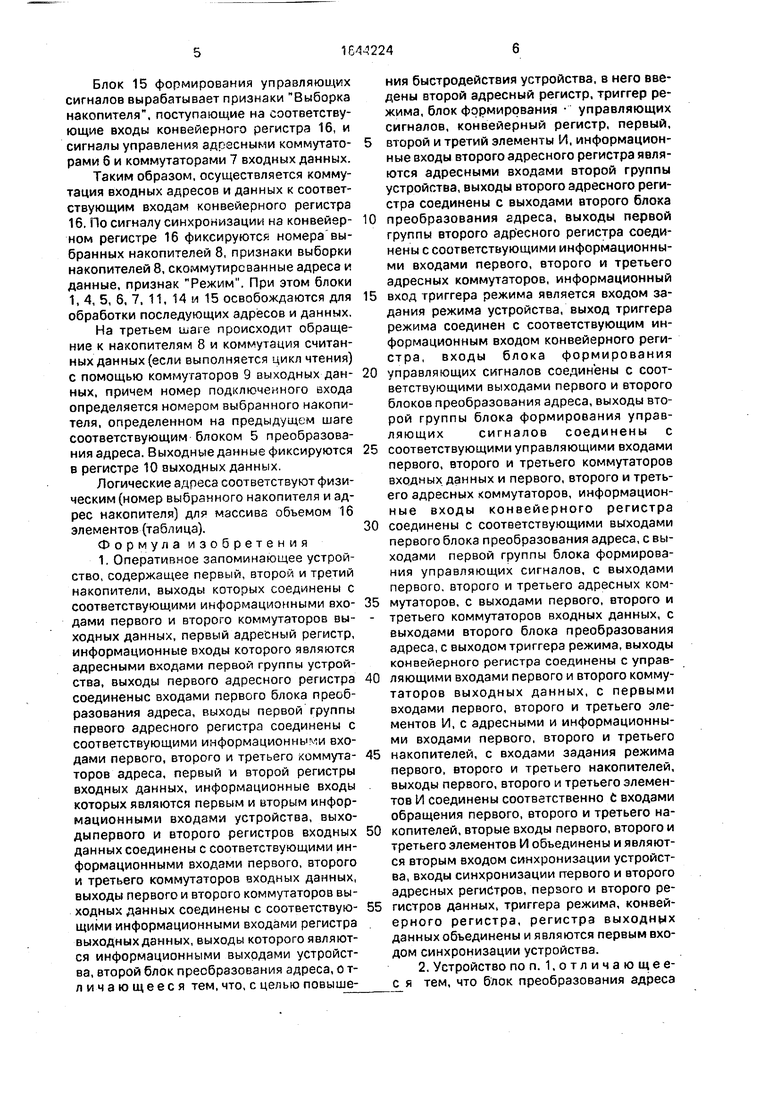

Размещение массива из 16 (20з) элементов приведено в таблице.

Вычисление остатка от деления на 3 можно выполнить на основе постоянных запоминающих устройств (ПЗУ). Увеличение

времени обращения к ОЗУ из-за задержек, вносимых схемами дешифрации адресов и коммутаторами, можно компенсировать введением конвейерного регистра, При этом в стадии обработки могут находиться две пары адресов.

Оперативное запоминающее устройство (фиг. 1) содержит адресный регистр 1, разделенный на старшую 2 и младшую 3 части, регистр 4 входных данных, два блока 5 преобразования адреса, три адресных коммутатора 6, три коммутатора 7 входных данных, три накопителя 8, два коммутатора 9 выходных данных, регистр 10 выходных данных, второй адресный регистр 11, разделенный на старшую 12 и младшую 13 части, триггер 14 режима, блок 15 формирования управляющих сигналов, конвейерный регистр 16, тр1/ элемента И 17,

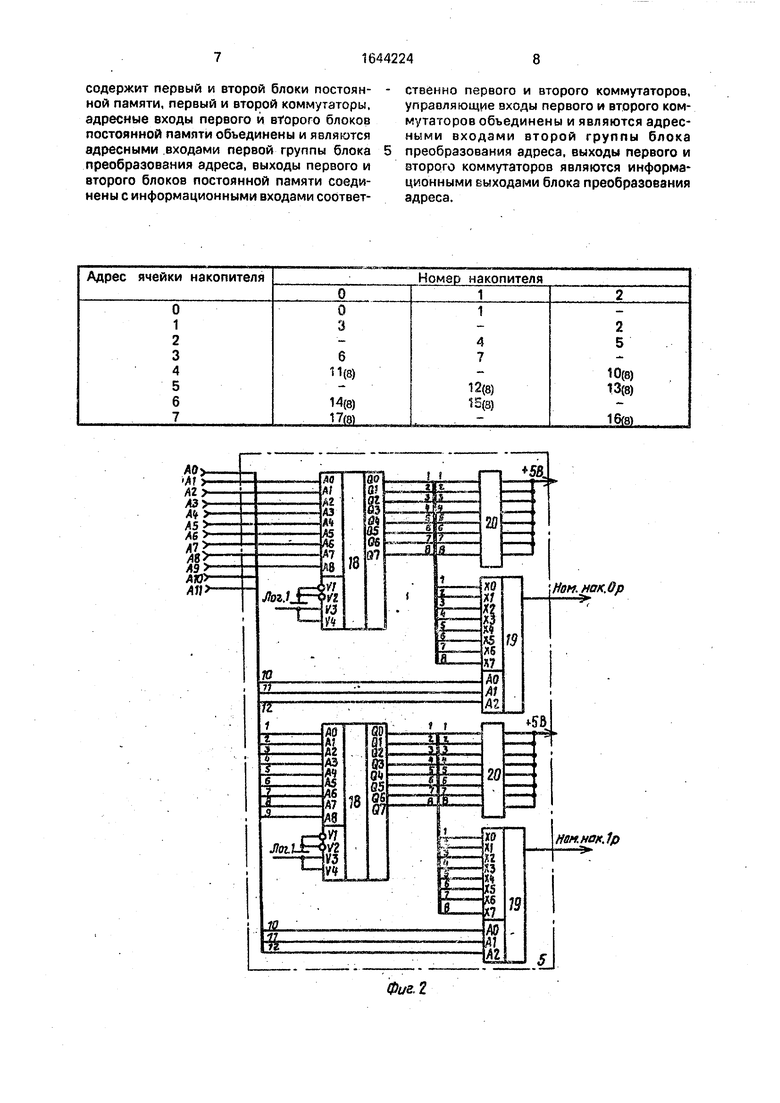

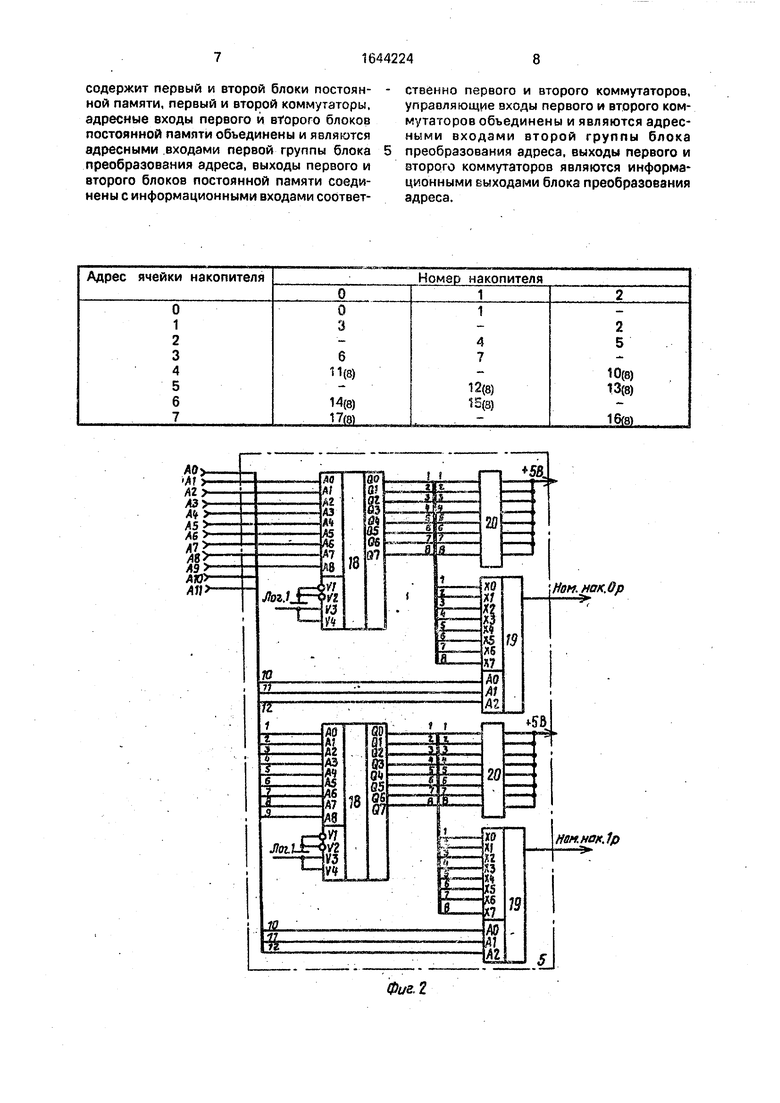

Блок 5 преобразования адреса (фиг. 2) содержит два блока 18 постоянной памяти, два коммутатора 19, блоки 20 резисторов.

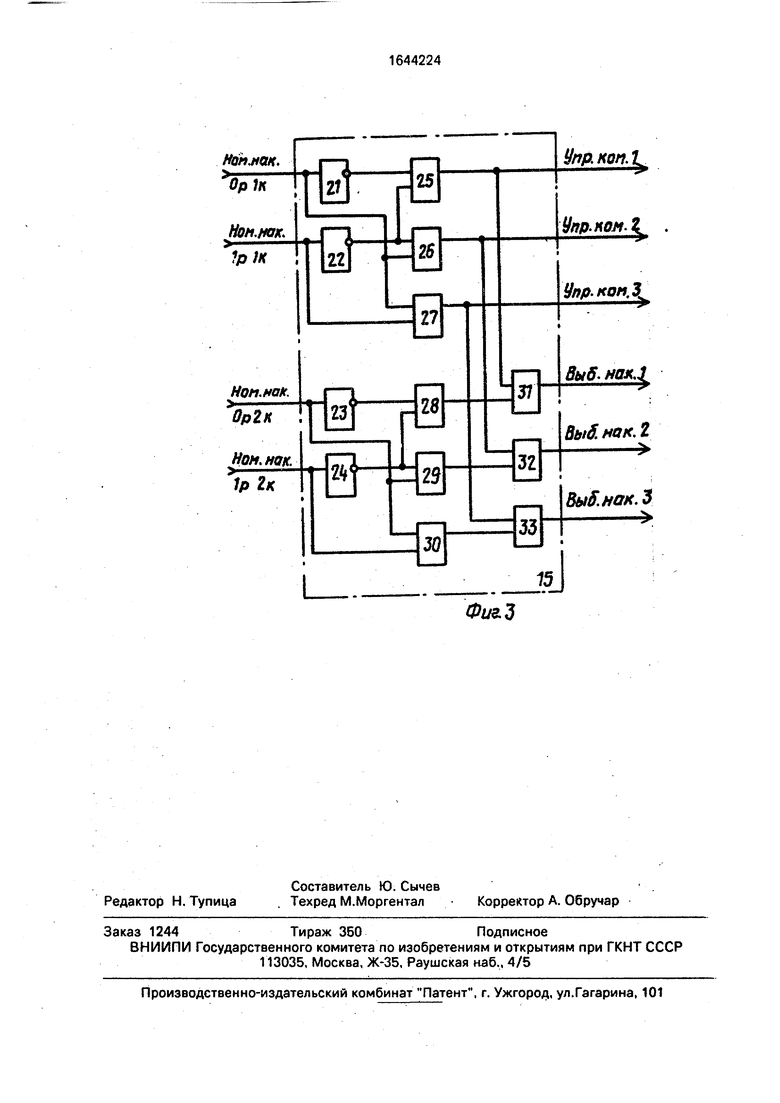

Блок 15 формирования управляющих сигналов (фиг. 3) содержит инверторы 21 -24. элементы И 25-30, элементы ИЛИ 31-33.

Оперативное запоминающее устройство работает следующим образом.

На адресные входы устройства поступают два адреса, соответствующие адресам операндов элементарной операции БПФ. Эти адреса в соответствии с алгоритмом быстрого преобразования Фурье отличаются, на величину, равную степени двух.

Процесс обращения к предлагаемому запоминающему устройству выполняется за три шага,

На первом шаге адреса, признак пись-чтение, входные данные (если выполняется цикл записи) фиксируются на адресных регистрах 1 и 11, триггерах 14 режима и регистрах 4 входных данных соот- ветственнс.

На втором шаге адреса с первого 1 и второго 11 адресных регистров поступают на первый и второй блоки 5 преобразования адреса (фиг. 2) соответственно. Блоки 5 преобразования адреса определяют номер накопителя 8, в котором находится адресуемый элемент. В соответствии с изложенным выше, при выполнении элементарной операции БПФ по основанию два номера накопителей 8, определенные первым и вторым блоками 5 преобразования адреса, никогда не совпадают.

С выходов блоков 5 преобразования адреса номера выбранных накопителей 8 поступают на соответствующие входы конвейерного регистра 16 и на входы блока 15 формирования управляющих сигналов (фиг, 3).

Блок 15 формирования управляющих сигналов вырабатывает признаки Выборка накопителя, поступающие на соответствующие входы конвейерного регистра 16, и сигналы управления адресными коммутато- рами 6 и коммутаторами 7 входных данных.

Таким образом, осуществляется коммутация входных адресов и данных к соответствующим входам конвейерного регистра 16. По сигналу синхронизации на конвейер- ном регистре 16 фиксируются номера выбранных накопителей 8, признаки выборки накопителей 8, скоммутирсванные адреса и данные, признак Режим. При этом блоки 1, 4, 5, 6, 7. 11, 14 и 15 освобождаются для обработки последующих адресов и данных.

На третьем шаге происходит обращение к накопителям 8 и коммутация считанных данных (если выполняется цикл чтения) с помощью коммутаторов 9 выходных дан- ных, причем номер подключенного входа определяется номером выбранного накопителя, определенном на предыдущем шаге соответствующим блоком 5 преобразования адреса. Выходные данные фиксируются в регистре 10 выходных данных.

Логические адреса соответствуют физическим (номер выбранного накопителя и адрес накопителя) для массива объемом 16 элементов (таблица).

Формула изобретения

содержит первый и второй блоки постоянной памяти, первый и второй коммутаторы, адресные входы первого и второго блоков постоянной памяти объединены и являются адресными входами первой группы блока преобразования адреса, выходы первого и второго блоков постоянной памяти соединены с информационными входами соответственно первого и второго коммутаторов, управляющие входы первого и второго коммутаторов объединены и являются адресными входами второй группы блока преобразования адреса, выходы первого и второго коммутаторов являются информационными выходами блока преобразования адреса.

Фиг.3

| Запоминающее устройство | 1981 |

|

SU972593A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1264240A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1991-04-23—Публикация

1988-06-15—Подача