- номер ячейки в выбранном блоке памяти. Использование преобразователя кода адреса и дешифраторов позволяет с форматом доступа N осуществить одновременную выборку элементов хранимого массива в порядке следования их номеров.

Недостатком этого устройства является низкая пропускная способность из-за невозможности одновременной выборки элементов массива в двоично-инверсной последовательности, в последовательности с шагом, кратным формату доступа, а также диагональных и поддиагональных элементов двумерного массива.

Наиболее близким техническим решением к предлагаемому является оперативное запоминающее устройство, содержащее адресный регистр, разделенный на две части - старшую и младшую, блоки преобразования адреса, адресные коммутаторы, коммутаторы входных данных, регистр входных данных, коммутаторы выходных данных, регистр выходных данных, накопители, вход адресного регистра является адресным входом устройства, выход старшей части адресного регистра соединен с управляющими входами коммутаторов входных и выходных данных, с входами блоков преобразования адреса и с вторыми информационными входами адресных коммутаторов, выходы блоков преобразования адреса соединены с первыми информационными входами соответствующих адресных коммутаторов, выходы которых соединены с входами старших разрядов адреса соответствующих накопителей, выход младшей части адресного регистра соединен с входами младших разрядов адреса накопителей, входы регистра входных данных являются информационными входами устройства, каждый выход регистра входных данных подключен к соответствующему информационному входу каждого коммутатора входных данных, выходы которых соединены с информационными входами соответствующих накопителей, выход каждого накопителя соединен с соответствующим информационным входом каждого коммутатора выходных данных, выходы коммутаторов выходных данных соединены с соответствующими входами регистра выходных данных, выходы которого являются информационными выходами устройства, управляющие входы адресных коммутаторов объединены и являются управляющим входом устройства.

В этом устройстве адрес состоит из двух частей - старшей и младшей. Старшая часть адреса устройства определяет номер четверти (при формате доступа ) накопителя, в которой находится адресуемое данное, а младшая часть адреса устройства определяет номер ячейки в этой четверти. Формат доступа определяется числом накопителей

в устройстве. Кроме того, старшая часть адреса определяет номер накопителя, в которой записывается данное с нулевого выхода регистра входных данных. При записи информации на входы старших разрядов адресанакопителей поступают преобразованные коды старшей части адресного регистра, что позволяет записывать данные с выходов регистра входных данных в различные четверти различных накопителей. При считывании информации на входы старших разрядов адреса накопителей поступает код с выхода старшей части адресного регистра. Старшая и младшая части адреса выдаются при этом на вход устрой

ства в двоично-инверсном порядке, что позволяет осуществить с форматом доступа N одновременную выборку элементов- хранимого массива е двоично-инверсной последовательности. Такая последовательность

5 считывания элементов массива информации необходима для процессоров, выполняющих функцию БПФ. Однако в данном устройстве невозможно осуществить с форматом доступа N одновременную выборку

0 элементов хранимого массива в последовательности с шагом, кратным формату досту- па, а также диагональных и поддиагональных элементов массива, так как эти элементы будут в большинстве слу5 чаев расположены в одноименных накопителях. Такая последовательность выборки элементов массива информации необходима для процессоров, выполняющих операции над матрицами (например, для

0 одновременного обращения к элементам столбцов матриц при их перемножении, для одновременного обращения к диагональным и поддиагональным элементам при вычислении определителей матриц и т.д.).

5 Недостатком этого устройства является низкая пропускная способность из-за невозможности одновременной выборки N элементов хранимого массива в последова-. тельности с шагом, кратным формату досту0 па, а также N диагональных и поддиагональных элементов массива.

Цель изобретения - повышение пропускной способности устройства за счет рационального размещения элементов вектора в

5 накопителях.

В предлагаемом устройстве элементы вектора с номерами, кратными формату доступа N (N-число накопителей в устройстве), располагаются при записи в зависимости от кода преобразования адреса в различных

накопителях. При этом пропускная способность устройства при обращении к элементам столбцов матриц, а также диагональным и поддиагональным элементам матриц по сравнению с прототипом возрастает пропорционально числу накопителей,

Таким образом, технико-экономическое преимущество изобретения по сравнению с базовым, в качестве которого выбран прототип, как наилучший из известных данного типа, заключается в повышении пропускной способности в N раз, где N-- число накопителей в устройстве.

Поставленная цель достигается тем, что в оперативное запоминающее устройство, содержащее N коммутаторов входных данных (N - количество параллельно-передаваемых- информационных сообщений), N - накопителей, причем выход i-ro коммутатора входных данных соединен с информационным входом i-ro накопителя (, (N-1), введены блок синхронизации, (N+1) блоков постоянной памяти, блок элементов И и N блоков элементов ИЛИ, причем вход разрешения ввода-вывода информации устройства соединён с входом пуска блока синхронизации, первый и второй выходы которого подключены соответственно к входу выборки всех блоков постоянной памяти и управляющему входу блока элементов И, вторая группа адресных входов всех блоков постоянной памяти является первым адресным входом устройства, первая группа адресных входов всех блоков постоянной памяти объединена с информационным входом блока элементов И и является вторым адресным входом устройства,.третья группа адресных входов всех блоков постоянной памяти является входом.задания кода преобразования адреса устройства, выход i-rp блока постоянной памяти соединен с первым входом i-ro блока элементов ИЛИ, второй вход которого соединен с выходом блока элементов И. выход i-ro блока элементов ИЛИ соединен с адресным входом i-ro накопители, выход N-ro блока постоянной памяти соединен с управляющими входами всех коммутаторов входных данных, t-ый информационный вход устройства является j- тым информационным входом р-го коммутатора ходных данных ()modN; ИО.(М-Т); (N-1); р-0,(КМ)). выход f-ro накопителя является i-тым информационным выходом устройства, входы разрешения записи и чтения всех накопителей соединены соответственно с третьим и четвертым выходами блока синхронизации.

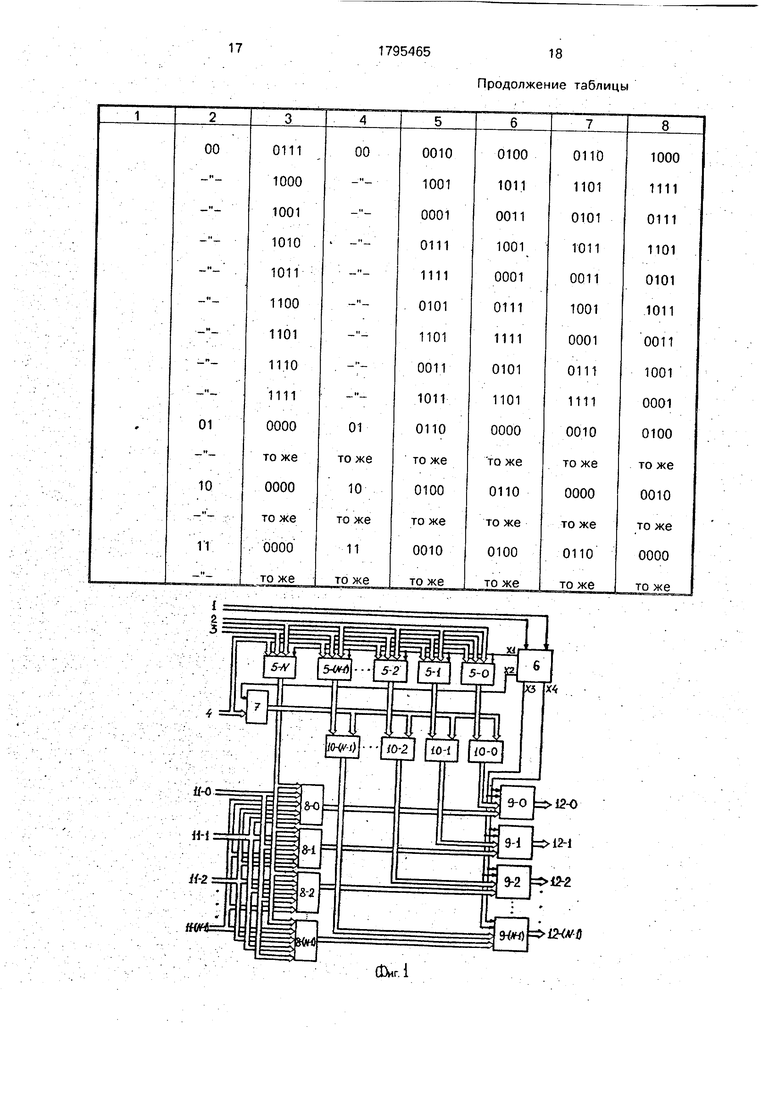

На фиг, 1 представлена функциональная схема устройства для параллельной передачи информации; на фиг. 2 функциональная схема блока синхронизации; на фиг. 3 и 4 показана структура размещения информации после записи массива из 64 информационных слов в устройстве с 5 числом накопителей соответственно для их последующей выборки в двоично-инверсной последовательности и для выборки диагональных и поддиагональных элементов массива с форматом доступа, равным N;

0 на фиг. 5 - временные диаграммы работы блока синхронизации.

Устройство содержит (фиг. 1) вход 1 разрешения ввода-вывода информации, вход 2 задания кода преобразования адреса уст5 ройства, первый адресный вход 3 устройства, второй адресный вход 4 устройства, группу 5 блоков постоянной памяти (5-0)- (5-N), блок 6 синхронизации, блок 7 элемен- тов И, группу 8 коммутаторов входных

0 данных (8-0)(N-1)J, группу 9 накопителей (9-0)(N-1), группу 10 блоков элементов ИЛИ (10-0)(N-1)y, группу 11 информационных входов устройства (11-0)- 11-(N-1). группу 12 информационных вы5 ходов устройства (12-0)(М-1).

Блок 6 синхронизации (фиг. 2) содержит, например, генераторы пачек импульсов 13 и 14, ждущие мультивибраторы 15 и 16, а также элементы задержки 17 и 18.

0

На фиг. 5 обозначены: ЗП - сигнал записи, поступающий по первому разряду входа 1 разрешения ввода-вывода информации устройства; СЧ - сигнал считывания, посту5 пающий в блоке 6 синхронизации по второму разряду входа 1 устройства; ПА - преобразованные адреса на адресных входах накопителей 9; ИВх - информационные сигналы на входах накопителей 9; Ивых 0 информационные сигналы на выходах 12 ус- тройства.

Устройство работает следующим образом.

Адрес, поступающий по входам 2 и 3

5 устройства, состоит из двух частей - старшей и младшей. Старшая часть адреса определяет номер накопителя 9, а младшая часть - номер ячейки в выбранном накопителе 9. Старшая часть адреса содержит k log2N

0 разрядов, а младшая - 2k разрядов. В устройстве для обеспечения одновременной выборки элементов массива в различных последовательностях с форматом доступа N применяется преобразование кода адреса в

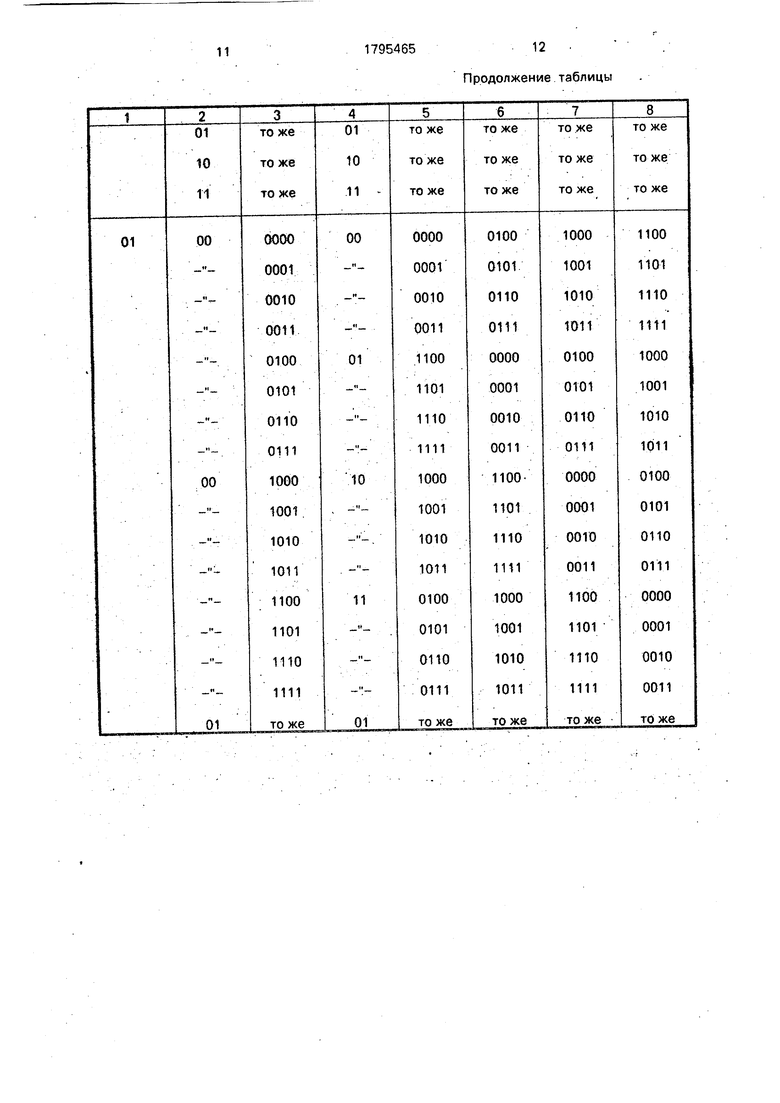

5 процессе записи информации. Причем, в процессе записи преобразованная старшая часть разрядов адреса поступает на адресные входы коммутаторов 8 входных данных, Преобразованная младшая часть разрядов адреса поступает на адресные входы накопителей 9. При этом вариант преобразования кода адреса определяется сигналами на входе 2 задания кода преобразования адреса устройства. В процессе считывания информации преобразование адреса не производится. Варианты преобразования кода адреса зависят от прошивки запоминающих элементов блоков 5 постоянной памяти. При этом разряды адресных входов блоков 5 постоянной памяти разделены на три части. Для примера, в устройстве с числом накопителей 9 для различных вариантов преобразования адреса прошивка запоминающих элементов блоков 5 представлены в таблице.

В устройстве в зависимости от кода преобразования адреса со входа 2 осуществляется перераспределение данных среди накопителей 9. Основной особенностью вычислительной системы в которой предполагается использование устройства является то, что операции производится над вектор- операндами, а результатом работы является результирующий вектор. Под вектором здесь понимается массив данных р, состоящий из элементов Do, PI, ..,, Pi, ,..., Рп-1, где n - ограничивается емкостью памяти. Производительность векторной (матричной) ЭВМ удается значительно повысить, если записывать данные (элементы вектора) в накопители 9 таким образом, чтобы иметь возможность затем их параллельно считывать с форматом доступа N. В предлагаемом устройстве в зависимости от выполняемой операций векторной (матричной) ЭВМ на вход 2 выдается код преобразования адреса. Количество различных вариантов преобразования адресов определяется разрядностью входа 2 устройства на основе выражения m fogak, где т - число разрядов кода преобразования, k - количество вариантов преобразования.

Рассмотрим работу устройства для случая прошивки блоков 5 постоянной памяти, представленного в таблице.

В данном примере код преобразования 00 при записи информации соответствует последующему считыванию данных (элементов вектора) в обычной последовательности, код 01 - считыванию данных в двоично-инверсной последовательности, код10 -для параллельного считывания элементов столбцов матрицы с форматом доступа 4, код 11 - для параллельного считывания диагональных и поддиагональных элементов матрицы 8X8 с форматом доступа 4,

Предположим, что в векторной ЭВМ выполняется операция БПФ. Для этого по входу 2 в устройство выдается код преобразования адреса 01. По сигналу с первого разряда входа 1 устройства в блоке 6 синхронизации вырабатывается серия сигналов XI для преобразования кодов адресов и ХЗ для записи информации с форматом в накопители 9 (см. фиг. 5). В результате, элементы обрабатываемого вектора через группу 11 информационных входов устройства в соответствии с таблицей будут записаны в определенном порядке в накопители 9. Если старшая часть кодов адресов записи устройства была 00, то элементы вектора Ро-Рбз будут расположены в

накопителях 9. в соответствии с фиг. 4. Нетрудно заметить, что такое распределение .элементов обрабатываемого вектора по ячейкам накопителей 9 позволяет с форматом доступа считать элементы вектора

в двоично-инверсной последовательности, что необходимо при выполнении операции БПФ в векторной ЭВМ. При этом считывание осуществляется по сигналу с второго разряда входа 1 устройства путем выработки серии управляющих сигналов с выходов Х2 и Х4 блока 6 синхронизации (см. фиг. 5), Аналогичным образом работает устройство в соответствии с таблицей в случае выполнения векторной ЭВМ операций над

матрицами (коды преобразования адреса 10 и 11).. -...Ф о р м у л а и з о б р е т е н и я

Устройство для параллельной передачи информации, содержащее N коммутаторов входных данных (М-количество параллельно-передаваемых информационных сообщений), N накопителей, причем выход i-ro

коммутатора входных данных соединен с информационным входом i-ro накопителя (, N-1), отличающееся тем, что, с целью повышения пропускной способности, в него введены блок синхронизации,

N+1 блоков постоянной памяти, блок эле- ме нтов И и N элементов ИЛИ, причем вход разрешения ввода информации устройства соединен с входом пуска блока синхронизации, первый и второй выходы которого подключены к входу разрешения записи всех блоков памяти и управляющему входу блока элементов И соответственно, первая группа адресных входов всех блоков постоянной памяти является первым адресным входом

устройства, втирая группа адресных входов всех блоков постоянной памяти объединена с информационным входом блока элементов И и является вторым адресным входом устройства, третья группа адресных входов всех блоков постоянной памяти является

входом задания кода преобразования адреса устройства, выход 1-го блока постоянной памяти соединен с первым входом 1-го элемента ИЛИ, второй вход которого соединен с выходом блока элементов И, выход 1-го элемента ИЛИ соединен с адресным входом 1-го накопителя, выход N-ro блока постоянной памяти соединен с управляющими входами всех коммутаторов входных данных.

i-e информационные входы которых объединены и являются i-м информационным входом устройства, выход i-ro накопителя является 1-м информационным выходом ус- тройства, входы разрешения записи и чтения всех накопителей соединены соответственное третьим и четвертым выходами блока синхронизации.

Продолжение таблицы

13

Продолжение таблицы

Продолжение таблицы

Продолжение таблицы

«a l

igq

CQ j

q

33-

(Ј

«d

i

tt

a q: W(T

09(1

oca

d

га

i

W(T

«a

-т

r

r

yq

09(1

«a d

a

W(T

кг

«a

c

vq;

°a

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1985 |

|

SU1264240A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1439671A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Устройство для параллельного формирования адресов | 1990 |

|

SU1734097A1 |

| Устройство для реализации быстрого преобразования Фурье при многоканальной обработке информации | 1983 |

|

SU1124324A1 |

| Оперативное запоминающее устройство | 1989 |

|

SU1705870A1 |

Ј«ЮЭШ1К ПЖ ЯУ ИиО-ХУН}ЧУа1ЯиОЯУН QSVaiHUO VH

««a ss

cr

Г

I

га

«d

srcl ка

d

rtQ « Zf(J

i f vSEmicwtfH 2 W3JJ4UOWH }чуаа. QSVQIXUONVH

W

гх

ir

W -

Q JMCP

«cr

ят(Г

«d

a

a «a

9

iffO 5{

Ј(

t a «a

JM03

П

9T

W

Я

57

S9tS6Al

Авторы

Даты

1993-02-15—Публикация

1990-10-08—Подача