(54) ЗАПОМИНАОДЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное запоминающее устройство | 1984 |

|

SU1228147A1 |

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| УСТРОЙСТВО ВЫБОРА ОПТИМАЛЬНОГО МАРШРУТА МАНЕВРА | 1992 |

|

RU2045773C1 |

| Запоминающее устройство с переменным форматом данных | 1981 |

|

SU987678A1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Многоканальный систолический процессор для вычисления полиномиальных функций | 2020 |

|

RU2737236C1 |

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

Изобретение относится к запоминающим устройствам и может быть использовано в многопроцессорных и многоканальных системах переработки информации и управления с общей памятью.

Известно запоминающее устройство, содержащее коммутатор, блок управления коммутатором и секционированную память l .

Недостатко этого устройства является его сложностьНаиболее близким техническим решением к изобретению является запоминающее устройство, содержащее адресный регистр, связанный с декорреляторог, выходы которого соединены со входами модулей памяти, информационный регистр, связанный с другими входами модулей памяти, и выходные сумматоры, входы которых.соединены с модулями памяти, а выходы через пороговые элементы соединены с выходные регистром 2 J.

Недостатком этого устройства является то, что оно не позволяет прои.зводить одновременную запист, по нескольким каналам, что снижает его быстродействие.

Целью изобретения является повышение быстродействия устройства. .

Поставленная цель достигается тем, что в запоминающее устройство, содержащее канал обращения к па.мяти, состоящий из адресного регистра, выходы которого подключены к входам декоррелятора и информационного регистра, первую группу сумматоров по модулю два, пороговые элементы, выходной регистр и блоки памяти, каждый из

10 которых состоит из многоуровневого элемента па.мяти, выход которого соединен с первьом входом первого умножителя, первого сумматора по модулю два и второго умножителя, первый вход

15 которого подключен к выходу первого сумматора по модулю два, а второй вход - к соответствующему выходу декоррелятора, причем входы первых cyMviaTopOB по модулю два соединены

20 с выходами информационного регистра, входы и выходы сумматоров по модулю два первой группы подключены соответственно, к выходам первых умножителей и к входам пороговых алиментов,

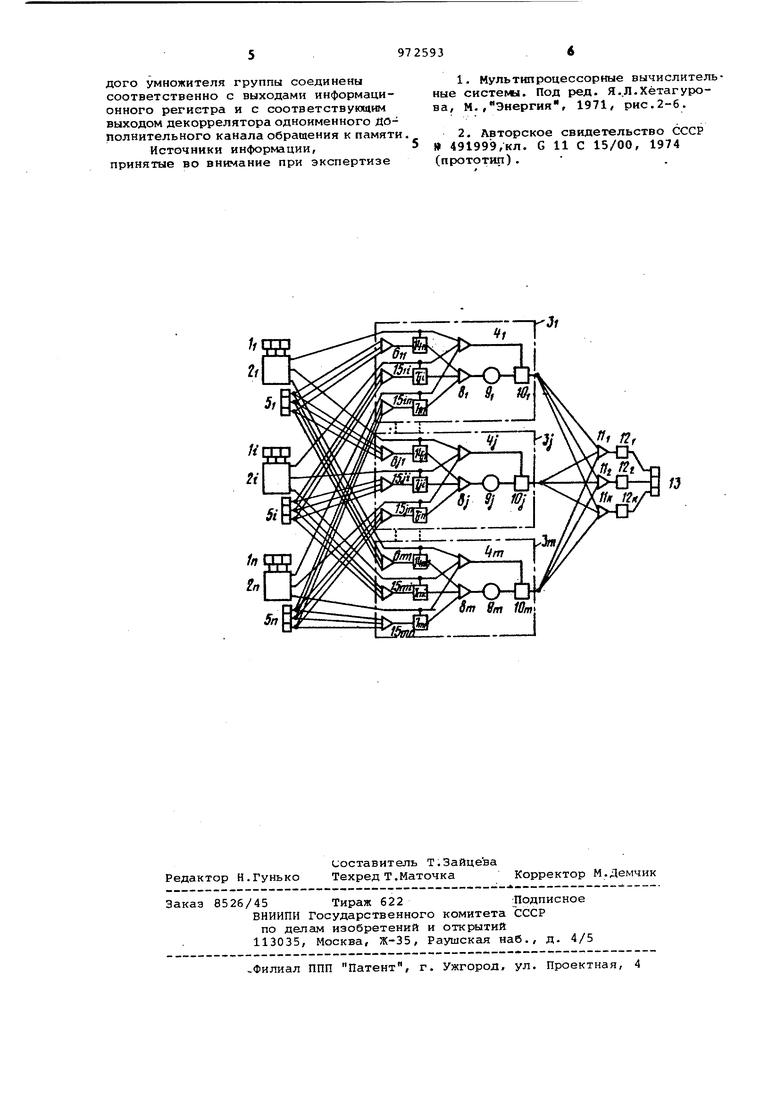

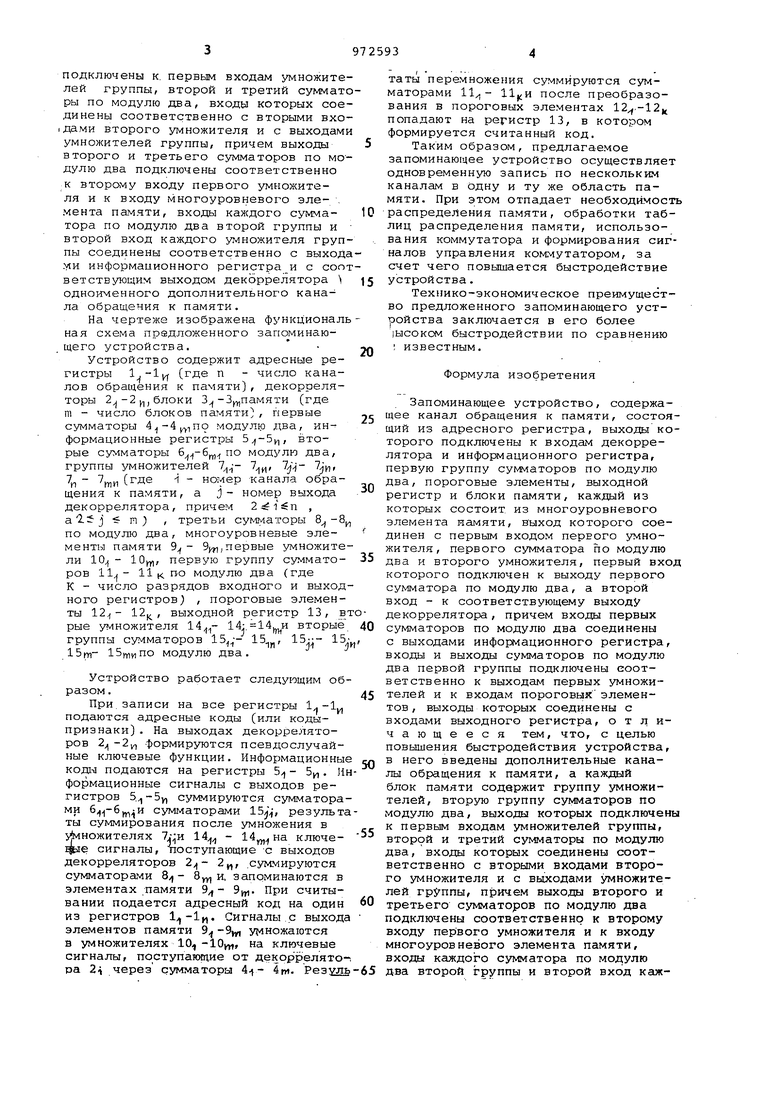

25 выходы которых соединены с входами выходного регистра, введены дополнительные каналы обращения к памяти, а .каждый блок памяти содержит группу умножителей, вторую группу суммато30ров по модулю два, выхо.цы которых подключены к. первым входам умножителей группы, второй и третий суммато ры по модулю два, входы которых соединены соответственно с вторыми вхо1дами второго умножителя и с выходами умножителей группы, причем выходы второго и третьего сумматоров по модулю два подключены соответственно к второму входу первого умножителя и к входу многоуровневого эле- , мента памяти, входы каждого сумматора по модулю два второй группы и второй вход каждого умножителя груп пы соединены соответственно с выхода -yiH информационного регистра и с соо ветствующим выходом декоррелятора одноименного дополнительного канала обращения к памяти. На чертеже изображена функциональ ная схема прадложенного запоминающего устройства. Устройство содержит адресные регистры к число каналов обращения к памяти), декорреляторы ,блоки 3 -З памяти (где m - число блоков памяти}, первые сумматоры модулю два, информационные регистры ,, вторые сумматоры по модулю два, группы умножителей 7, Ijy,, 1 - 7 (где - номер канала обращения к памяти, а J- номер выхода декоррелятора, причем , al- j Fi ) , третьи сумматоры по модулю два, многоуровневые элементы памяти 9),первые умножите ли 10 - Юуп первую группу сумматоров 11 к по модулю два (где К - число разрядов входного и выход ного регистров , пороговые элементы 12| , выходной регистр 13, в рые умножителя 14:. вторые группы сумматоров 15, 15-- 15 15т- 15типо модулю два. Устройство работает следующим об разом , При.записи на все регистры подаются адресные коды (или кодыпризнаки) . На выходах декорреляторов формируются псевдослучайные ключевые функции. Информационны кода подаются на регистры 5/)- 5,. Л формационные сигналы с выходов регистров 5.-ЗУ, суммируются сумматора ми сумматорами , результа ты суммирования после умножения в множителях 14 14 на ключеqfcje сигналы, поступающие С выходов декорреляторов 2„, .суммируются сумматорами 8у) - Зуу, и, запоминаются в элементах памяти 9. При считывании подается адресный код на один из регистров l,-lj. Сигналы с выхода элементов памяти 9 , умножаются в умножителях 10,-lOv/,, на ключевые сигналы, поступающие от декоррелятора 2 через сумматора 4. Резул таты перемножения суммируются сумматорами Их;- llfcH после преобразования в пороговых элементах .2. попадают на регистр 13, в котором формируется считанный код. Таким образом, предлагаемое запоминаюмдее устройство осуществляет одновременную запись по нескольким каналам в одну и ту же область памяти. При этом отпадает необходимость распределения памяти, обработки таблиц распределения памяти, использования коммутатора и формирования сигналов управления коммутатором, за счет чего повыщается быстродействие устройства. Техпико-экономическое преимущество предложенного запоминающего устройства заключается в его более 1ЫСОКОМ быстродействии по сравнению ; известным. Формула изобретения Запоминающее устройство, содержащее канал обращения к памяти, состоящий из адресного регистра, выходы которого подключены к входам декоррелятора и информационного регистра, первую группу сумчаторов по модулю два, пороговые элементы, выходной регистр и блоки памяти, каждый из которых состоит из многоуровневого элемента памяти, выход которого соединен с первым входом первого умножителя, первого сумматора по модулю два и второго умножителя, первый вход которого подключен к выходу первого сумматора по модулю два, а второй вход - к соответствующему выходу декоррелятора, причем входы первых сумматоров по модулю два соединены с выходами информационного регистра, входы и выходы сумматоров по модулю два первой группы подключены соответственно к выходам первых умножителей и к входам пороговых элементов, выходы которых соединены с входами выходного регистра, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены дополнительные каналы обращения к памяти, а каждый блок памяти содержит группу умножителей, вторую группу сумматоров по модулю два, выходы которых подключены к первым входам умножителей группы, вторрй и третий сумматоры по модулю два, входы которых соединены соответственно с вторыми входами второго умножителя и с выходами умножителей группы, причем выходы второго и третьего сумматоров по модулю два подключены соответственно к второму входу первого умножителя и к входу многоуровневого элемента памяти, входы каждого сумматора по модулю два второй группы и второй вход каждого умножителя группы соединены соответственно с выходами информационного регистра и с соответствующим выходом декоррелятора одноименного дополнительного канала обраиения к памяти.

Источники информации, принятые во внимание при экспертизе

(прототип).

/J

Sm /О

Авторы

Даты

1982-11-07—Публикация

1981-04-07—Подача