1

(21)4467181/24

(22)29.,07.88

(46) 23,04.91. Бюл. № 15

(71)Особое конструкторское бюро Института космических исследований

АН СССР

(72) С.Г. Гончаров (53) 681.325(088.8)

(56) Авторское свидетельство СССР № 663102, кл. Н 03 К 13/20, 1971.

Авторское свидетельство СССР № 1341717, кл. Н 03 М 1/10, 1986.

(54) ПРЕОБРАЗОВАТЕЛЬ КОД-КОД (57) Изобретение относится к автоматике и информационно-измерительной технике и может быть использовано в интерфейсных устройствах. В устройстве, содержащем блок 1 определения матис- сы и блок 2 определения положения запятой, оба блока выполнены соответственно на коммутаторах 1.1-1„М, а также шифраторе 3 и элементах 4.f- 4„2Р ИЛИ. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Преобразователь напряжения в код | 1980 |

|

SU924853A2 |

| Преобразователь частоты в код | 1985 |

|

SU1356207A1 |

| Операционное устройство | 1985 |

|

SU1367012A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Цифровое логарифмирующее устройство | 1985 |

|

SU1262490A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ПОРЯДКА ПРИ НОРМАЛИЗАЦИИ ЧИСЕЛ | 2017 |

|

RU2638724C1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

}

Ф Ј 4ь

W

эо

35

Изобретение относится к автоматике и информационно-измерительной технике и может быть использовано в интерфейсных устройствах.

Цель изобретения - повышение быстродействия.

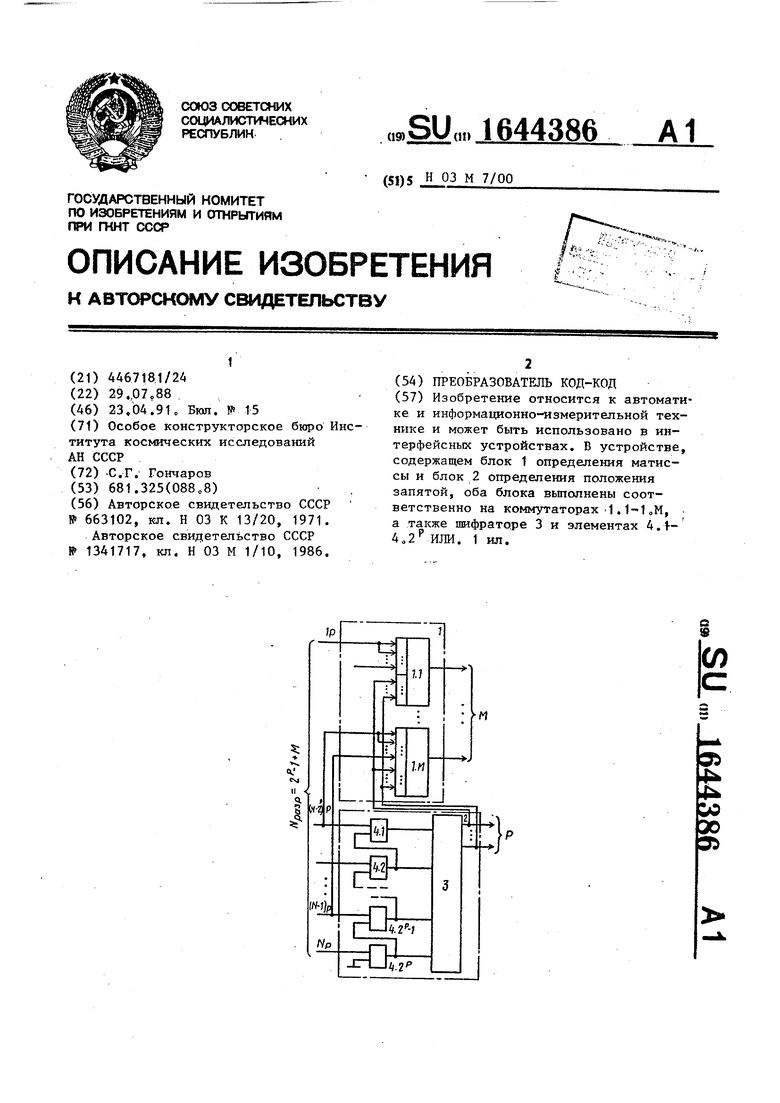

На чертеже приведена функциональная схема преобразователя.

Преобразователь содержит блок 1 определения мантиссы, выполненный на М коммутаторах 1.1-1сМ, блок 2 определения положения запятой, выполненный на шифраторе 3 и 2° элементах 4. ИЛИ.

Преобразователь работает следующим образом.

Согласно функциональной схеме на входную шину устройства подается N-разрядньй код. Число разрядов вход- ного и выходного кодов устройства связано соотношением

N ( 1) + М,

где N - число разрядов входного ко-

да устройства;

Р - число старших разрядов выходного кода устройства; М - число младших разрядов выходного кода устройства. На вход дези-цепочки 4 подаются старшие разряды входной шины, начиная от N разряда до N-2P разряда0 Срабатыванием дези-цепочки определяется положение первого значащего разряда входного кода с, На выходе, дези-цепоч- ки имеем позиционный код, который преобразуется шифратором 2 в Р-раз- рядный код старших разрядов йыходногс кода устройстэа Р-разрядный код старших разрядов подается также на , управление коммутдторами 3, подключающими к М-разрядному коду младших разрядов выходных шин устройства разряды входного кода, следующие за первым значащим разрядом входно- го кода. Как видно из указанного со- отношения, число выходных разрядов устройства М+Р меньше числа входных разрядов„ Входной и выгодной коды, исходя из указанного соотношения, связаны псевдологарифмической зависимостью, где М разряды указывают на мантиссу псевдологарифма, а Р разряды-- на положение запятой, Пре- образование разрядного кода в устрой стве в ,М+Р разрядный псевдологарифмический код АЦП обеспечивает выравнивание относительной погрешности по всему диапазону преобразования.

Применение дези-цепочки для выделения старшего значащего разряда позволяет повысить быстродействие устройства коррекции. В зависимости от конкретной серии микросхем, например для серии К155 и 564, среднее время срабатывания типового вентиля в 2-5 раз меньше времени срабатывания типового регистра сдвига. Соответственно и скорость срабатывания устройства увеличивается не мене чем в 2-5 раз

Формула изобретения

Преобразователь код-код, содержащий блок определения мантиссы и блок определения положения запя- той, выходы которого являются выходной шиной Р старших разрядов выходного кода, выходной шиной М младших разрядов выходного кода являются выходы блока определения мантиссы, входы которого являются (N-1)-разрядной входной шиной, где N-разрядность входного кода, равная 2 -1+М, отличающийся тем, что, с целью повышения быстродействия, блок определения мантиссы выполнен на М коммутаторах, а блок определения положения запятой выполнен на 2° элементах ИЛИ и шифраторе, выходы которого являются выходной шиной Р старших разрядов выходного кода, а входы подключены к выходам соответствующих элементов ИЛИ, первый вход каждого элемента ИЛИ, кроме последнего, подключен к, выходу последующего элемента ИЛИ, первый вход последнего элемента ИЛИ является шиной нулевого потенциала, вторые входы элементов ИЛИ являются шиной 2 старших разрядов входного кода, пвый и второй информационные входы кадого коммутатора, объединены и являются соответственно с первого по М-й разрядами входной шины, входы с третьего по ()-й. даждого 1-го коммутатора, где ,.MJ, являются соответственно с (i-M)-ro no Ј(i+1) + ( -3)J-ft разрядами входной шины, одноименные адресные входы коммутаторов объединены и подключены к соответствующим выходам шифратора.

Авторы

Даты

1991-04-23—Публикация

1988-07-29—Подача