Изобретение относится к вычислительной технике и может быть использовано в составе универсальных или специализированных вычислительных машин для выполнения арифметико-логических операций над операндами с плавающей запятой.

Цель изобретения - расширение функциональных возможностей устройства в части дополнительного выполнения операций вычитания и деления над операндами с плавающей запятой, логических операций И, ИЛИ, НЕ, сложения по модулю два, а также повышение быстродействия за счет асинхронного режима вьшолнения операций.

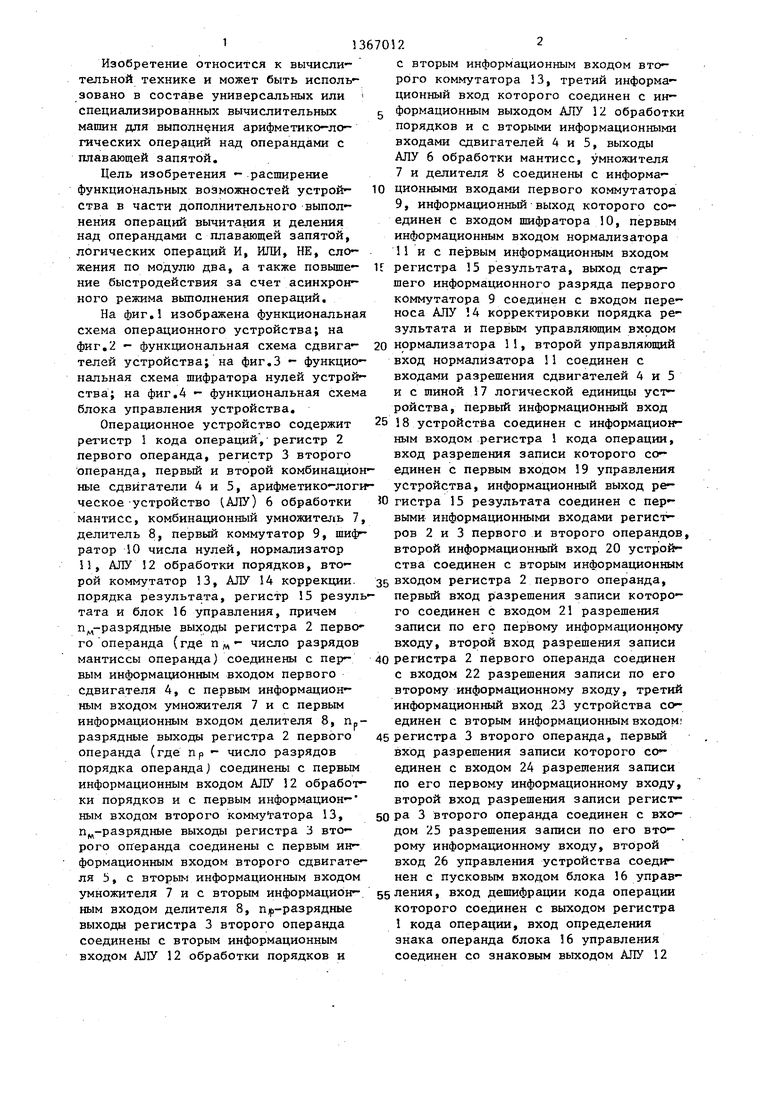

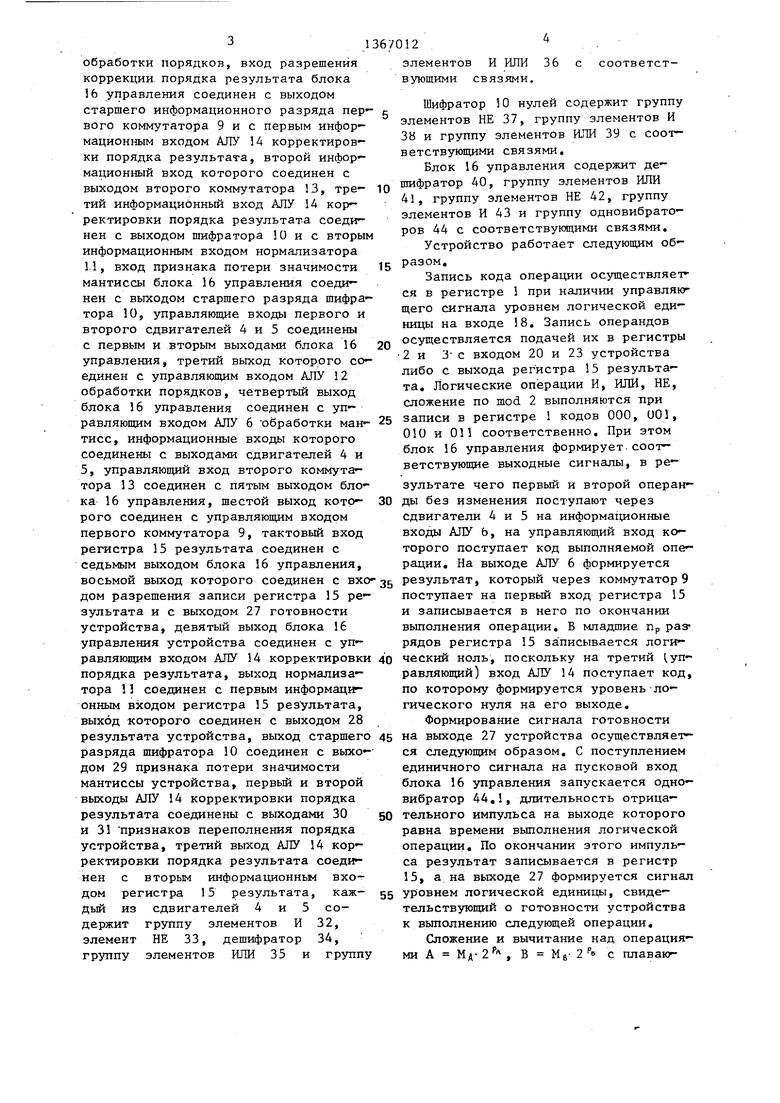

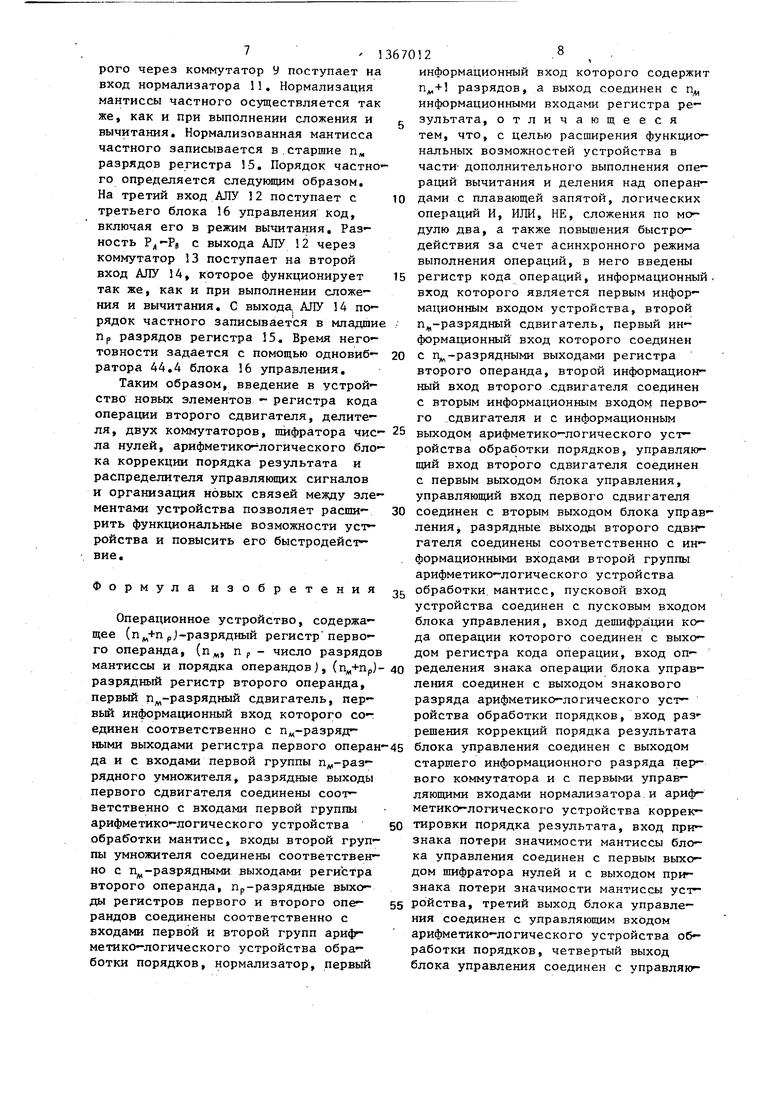

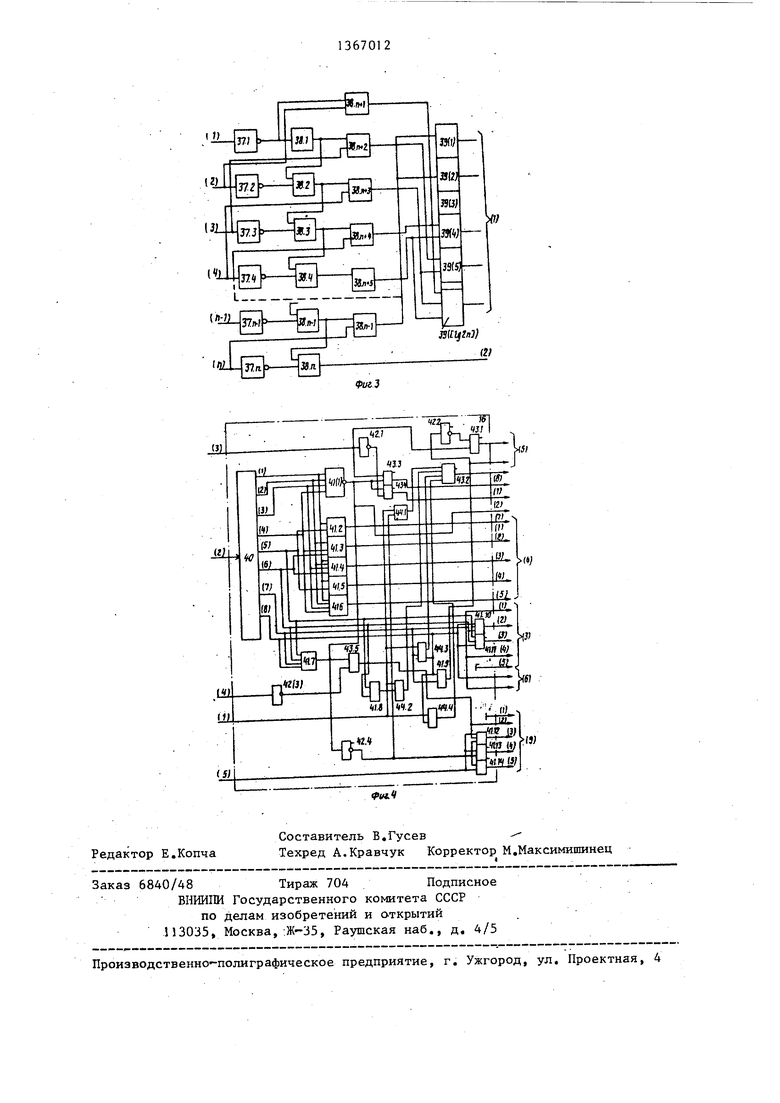

На фиг,1 изображена функциональная схема операционного устройства; на фиг,2 - функциональная схема сдвига- телей устройства; на фиг.З - функциональная схема шифратора нулей устройства; на фиг,А - функциональная схема блока управления устройства.

Операционное устройство содержит регистр 1 кода операций, регистр 2 первого операнда, регистр 3 второго операнда, первый и второй комбинацион

с вторым информационным входом второго коммутатора J3, третий информационный вход которого соединен с информационным выходом АЛУ 52 обработки порядков и с вторыми информационными входами сдвигателей 4 и 5, выходы АЛУ 6 обработки мантисс, умножителя 7 и делителя b соединены с информа-

ционными входами первого коммутатора 9, информационный-выход которого соединен с входом шифратора 10, первым информационным входом нормализатора И и с первым информационным входом

регистра 15 результата, выход старшего информационного разряда первого коммутатора 9 соединен с входом переноса АЛУ 14 корректировки порядка результата и первым управляющим входом

нормализатора 11, второй управляющий вход нормализатора 11 соединен с входами разрешения сдвигателей 4 и 5 и с шиной 57 логической единицы устройства, первый информационный вход

8 устройства соединен с информационным входом регистра 1 кода операции, вход разрешения записи которого соединен с первым входом 19 управления

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования двух чисел с плавающей запятой | 1988 |

|

SU1529214A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Вычислительное устройство | 1987 |

|

SU1456949A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

Изобретение относится к области вычислительной техники и может быть использовано в составе универсальных или специализированных вычислительных машин для выполнения арифметико- логических операций над операциями с плавающей запятой. Цель изобретения- расширение функциональных возможностей устройства в части дополнительноп го выполнения операций вычитания и деления над операндами с плавающей запятой, логических операций И, ИЛИ, НЕ, сложения по модулю два, а также повышение быстродействия за счет асинхронного режима выполнения операций. Операционное устройство содержит регистр 1 кода операций, регистры 2, 3 первого и второго операндов, первый и второй комбинационные сдви- гатели 4, 5, арифметико-логическое устройство 6 обработки мантисс, инационный умножитель 7, делитель 8, первый коммутатор 9, шифратор ла нулей,нормализатор 1 1,арифметико- логическое устройство 12 обработкипо- рядков ,второй коммутатор 13, арифметико-логическое устройство 14 коррекции порядка результата,регистр 15 результата и блок 16 управления с соответствующими связями.Операционное устройство производит арифметические и логические операции над операндами с пла-. вающей запятой в асинхронном режиме.4kn. Ч i (Л со Од , i 9utt

ные сдвигатели 4 и 5, арифметико-лопг- устройства, информационный выход ре- ческое устройство (АЛУ) 6 обработки О гистра 15 результата соединен с пер- мантисс, комбинационный умножитель 7, выми информационными входами регист- делитель 8, первый коммутатор 9, шиф- ров 2 и 3 первого и второго операндов, ратор 10 числа нулей, нормализатор второй информационный вход 20 устрой- П, АЛУ 12 обработки порядков, вто- ства соединен с вторым информационным рой коммутатор 13, АЛУ 14 коррекции. 35 регистра 2 первого операнда, порядка результата, регистр 15 резуль- первый вход разрешения записи которо- тата и блок 16 управления, причем го соединен с входом 21 разрешения

п,-разрядные выходы регистра 2 перво го операнда (где п ;, - число разрядов мантиссы операнда) соединены с первым информационным входом первого сдвигателя 4, с первым информационным входом умножителя 7 и с первым информационным входом делителя 8, п,- разрядные выходы регистра 2 первого операнда (где Пр - число разрядов порядка операнда) соединены с первым информационным входом АЛУ 12 обработки порядков и с первым информацион- ным входом второго комму гатора 13, п„-разрядные выходы регистра 3 второго операнда соединены с первым информационным входом второго сдвигателя 5 , с вторы информационным входом умножителя 7 и с вторым информацион-. ным входом делителя 8, П1(1-разрядные выходы регистра 3 второго операнда соединены с вторым информационным входом АЛУ 12 обработки порядков и

записи по его первому информационному входу, второй вход разрешения записи

40 регистра 2 первого операнда соединен с входом 22 разрешения записи по его второму информационному входу, третий информационный вход 23 устройства соединен с вторым информационным входом;

45 регистра 3 второго операнда, первый вход разрешения записи которого соединен с входом 24 разрешения записи по его первому информационному входу, второй вход разрешения записи регист50 ра 3 второго операнда соединен с входом 25 разрешения записи по его второму информационному входу, втОрой вход 26 управления устройства соед1г- нен с пусковым входом блока 16 управ55ления, вход дешифрации кода операции которого соединен с выходом регистра 1 кода операции, вход определения знака операнда блока 16 управления соединен со знаковым выходом АЛУ 12

обработки порядков, вход разрешения коррекции порядка результата блока 16 управления соединен с выходом старшего информационного разряда пер вого коммутатора 9 и с первым информационным входом АЛУ 14 корректировки порядка результата, второй информационный вход которого соединен с выходом второго коммутатора 13, третий информационный вход АЛУ 14 корректировки порядка результата соединен с выходом шифратора 10 и с вторы информационным входом нормализатора 1.1, вход признака потери значимости мантиссы блока 16 управления соединен с выходом старшего разряда шифратора 10, управляющие входы первого и второго сдвигателей 4 и 5 соединены с первым и вторым выходами блока 16 управления, третий выход которого соединен с управляющим входом АЛУ 12 обработки порядков, четвертый выход блока 16 управления соединен с управляющим входом АЛУ 6 обработки мантисс, информационные входы которого соединены с выходами сдвигателей 4 и 5, управляющий вход второго коммутаг- тора 13 соединен с пятым выходом блока 16 управле1шя, шестой выход которого соединен с управляющим входом первого коммутатора 9, тактовый вход регистра 15 результата соединен с седьмым выходом блока 16 управления, восьмой выход которого соединен с дом разрешения записи регистра 15 результата и с выходом 27 готовности устройства, девятый выход блока 16 управления устройства соединен с уп-

вхо

равляющим входом АЛУ 14 корректировки 40 ческий ноль, поскольку на третий (,управляющий) вход АЛУ 14 поступает код, по которому формируется уровень -логического нуля на его выходе.

равляющий) вход АЛУ 14 поступает код, по которому формируется уровень -логического нуля на его выходе.

Формирование сигнала готовности

порядка результата, выход нормализатора 1 соединен с первым информационным входом регистра 15 результата, выход которого соединен с выходом 28 результата устройства, выход старшего 45 на выходе 27 устройства осуществляет- разряда шифратора 10 соединен с выхо- ся следующим образом, С поступлением дом 29 признака потери значимости единичного сигнала на пусковой вход мантиссы устройства, первый и второй блока 16 управления запускается одновыходы АЛУ 14 корректировки порядка результата соединены с выходами 30 и 31 признаков переполнения порядка устройства, третий выход АЛУ 14 корректировки порядка результата соед1г- нен с вторым информационньм входом регистра 15 результата, каждый из сдвигателей 4 и 5 содержит группу элементов И 32, элемент НЕ 33, дешифратор 34, группу элементов ИЛИ 35 и групп

в И ИЛИ связями.

4 36

соответст10

g 15 20

Шифратор 10 нулей содержит группу элементов НЕ 37, группу элементов И 38 и группу элементов ИЛИ 39 с соответствующими связями.

Блок 16 управления содержит дешифратор 40, группу элементов ИЛИ 41, группу элементов НЕ 42, группу элементов И 43 и группу одновибрато- ров 44 с соответствующими связями.

Устройство работает следующим образом.

Запись кода операции осуществляет ся в регистре 1 при наличии управляющего сигнала уровнем логической единицы на входе 18, Запись операндов осуществляется подачей их в регистры 2 и 3-е входом 20 и 23 устройства либо с выхода регистра 15 результата. Логические операции И, ИЛИ, НЕ, сложение по mod 2 выполняются при записи в регистре 1 кодов 000, 001, 010 и 011 соответственно. При этом блок 16 управления формирует.соответствующие выходные сигналы, в результате чего первый и второй операнды без изменения поступают через сдвигатели 4 и 5 на информационные входы АЛУ 6, на управляющий вход которого поступает код выполняемой операции. На выходе АЛУ 6 формируется 3g результат, который через коммутатор 9 поступает на первый вход регистра 15 и записывается в него по окончании вьтолнения операции, В младшие Пр раз рядов регистра 15 записывается логи25

30

ческий ноль, поскольку на третий (,управляющий) вход АЛУ 14 поступает код, по которому формируется уровень -логического нуля на его выходе.

Формирование сигнала готовности

на выходе 27 устройства осуществляет- ся следующим образом, С поступлением единичного сигнала на пусковой вход блока 16 управления запускается одновибратор 44,1, длительность отрица- тельного импульса на выходе которого равна времени выполнения логической операции. По окончании этого импульса результат записывается в регистр 15, а на выходе 27 формируется сигнал уровнем логической единицы, свидетельствующий о готовности устройства к выполнению следующей операции,

Сложение и вычитание над операциями

А Мд- 2 , В MS- 2 с плаваютщей запятой выполняется при записи в регистр 1 соответственно кодов 100 и 101, На управляющий вход АЛУ 12 поступает с третьего выхода блока 16 уп равления сигнал, включая его в режим вычитания. На выходе АЛУ 12 формиру- ется разность , по знаку которо включается один из сдвигателей 4 или 5, Если знак равен О (число Pj( Рв положительное), то на выходах 1 и 2 блока 16 управления формируютс соответственно О и 1, приводя к сдвигу Mg, .Если знак равен 1 Счисло РД-РВ отрицательное), то на выходах 1 и 2 блока 16 управления формируются соответственно 1 и О приводя к сдвигу Мд, Сдвиг Mg или Мд осуществляется вправо на число разрядов, равное модулю значения Р.-Ро, В

,п Р

АЛУ 6 формируется соответственно сумма или разность мантисс М, и Mg, поступающих с выходов сдвигателей 4 и 5, Результат с выхода АЛУ 6 через коммутатор 9 поступает на входы шиф- ратора 10 числа нулей и нормализатор 11, На выходе шифратора 10 формируется код, равный числу последовательных нулей, начиная со старщего разряда входного слова.

Этот код поступает на второй вход нормализатора 11, на выходе которого формируется нормализованное значение мантиссы (значение старшего разряда равно 1), которое записывается в .

старшие п, разрядов регистра 15, При сложении возможно .переполнение результата мантиссы (в старшем разряде АЛУ формируется единица, В этом случае нормализация мантиссы осуществляется сдвигом результата мантиссы на один разряд вправо с помощью нормализатора 11,.

Порядок результата находится следующим образом,

Если РД-РВ О, то на пятом выходе блока 16 управления формируется код 00 и через коммутатор 13 на второй вход АЛУ 14 поступает Рд, Если

Р,-Р

-; О, то на пятом йыходе блока 16 управления формируется код 10 и через з оммутатор 13 на второй вход АЛУ 14 поступает Pg, На первый вход АЛУ 14 поступает код с выхода шифратора 10 числа нулей. На третий вход АЛУ 14 поступает код, включающий его в режим вычитания, если значение Признака потери значимости мантиссы, формирующееся на втором выходе шиф-

ратора 10 числа нулей, не равно единице. Если значение признака потери значимости мантиссы равно единице, то на вход АЛУ 14 поступает код, по которому на его выходе формируется сигнал уровнем логического нуля. Если имеет место переполнение результата (значение единицы на выходе стершего разряда коммутатора 9), то на третий вход АЛУ 14 поступает код, который осуществляет в АЛУ 14 сложение содержимого, поступающего на второй вход, с единицей, поступающей на вход переноса АЛУ 14, Результат с выхода АЛУ 14 записывается в. щие Пр разрядов регистра 15, В АЛУ 14 осуществляется также формирование признаков отрицательного и положительного переполнения порядка результата. Время неготовности операций сложения и вычитания задается с помощью одновибратора 44,2 блока 16 управления,

Умножение с плавающей запятой над

операндами А

Мл-2

В

М.-2

Ре,

выполняется при записи в регистр 1 кода 110, В результате мантиссы Мд, Mj перемножаются с помощью умножителя 7, с выхода которого результат через коммутатор 9 поступает на вход нормализатора 11 и шифратора 10 числа нулей. Нормализация мантиссы произведения осуществляется так же, как и при выполнении сложения и вычитания, и записывается в старшие п разрядов регистра 15, Порядок определяется следующим образом. На третий вход АЛУ 12 с третьего выхода блока 16 управления поступает код, включаю

щий его в режим сложения порядков Р.

0

и Pg, Значение РА+РВ через коммутатор 13 поступает на второй вход АЛУ 14, включенного в режим вычитания, ес 5 ли признак потери значимости мантиссы не равен 1, В противном случае АЛУ 14 включается в режим формирования логического нуля. Результат с выхода АЛУ 14 записывается в мпадшие Пр разрядов регистра 15, Время неготов- . ности выполнения операции умножения задается с помощью одновибратора 44,3 блока управления.

Деление с плавающей запятой над. операндами А Мд-. , В Мв;2 выполняется при записи в регистр 1 кода 111, В результате мантисса М д делится на мантиссу М с помощью делителя 8, результат на выходе кото-

5

рого через коммутатор У поступает на вход нормализатора 11. Нормализация мантиссы частного осуществляется так же, как и при выполнении сложения и вычитания. Нормализованная мантисса частного записывается в.старшие п„ разрядов регистра 15, Порядок частного определяется следующим образом. На третий вход АЛУ 12 поступает с третьего блока 16 управления код, включая его в режим вычитания. Разность РД-РВ с выхода АЛУ 12 через коммутатор 13 поступает на второй вход АЛУ 14, которое функционирует так же, как и при выполнении сложения и вычитания, С выхода АЛУ 14 порядок частного записывается в младши Пр разрядов регистра 15, Время него-

товности задается с помощью одновиб- ратора 44,4 блока 16 управления.

Таким образом, введение в устройство новых элементов - регистра кода операции второго сдвигателя, делителя, двух коммутаторов, шифратора чис- ла нулей, арифметико-логического блока коррекции порядка результата и распределителя управляющих сигналов н организация новых связей между элементами устройства позволяет расширить функциональные возможности устройства и повысить его быстродействие.

Формула изобретения

Операционное устройство, содержащее (пц,+Пр -разрядный регистр первого операнда, (п,, Пр - число разрядов

устройства соединен с пусковым входом блока управления, вход дешифрации кода операции которого соединен с выходом регистра кода операции, вход опмантиссы и порядка операндовJ, ()-40 ределения знака операции блока управ-

разрядный регистр второго операнда, первый п -разрядный сдвигатель, первый информационный вход которого соединен соответственно с Пд,-разряд- ными выходами регистра первого операн-45 да и с входами первой группы Пд|,-раз- рядного умножителя, разрядные выходы первого сдвигателя соединены соответственно с входами первой группы арифметико-логического устройства обработки мантисс, входы второй группы умножителя соединены соответственно с п -разрядными выходами регистра

ления соединен с выходом знакового разряда арифметико-логического устройства обработки порядков, вход раз решения коррекций порядка результата блока управления соединен с выходом старшего информационного разряда первого коммутатора и с первыми управляющими входами нормализатора.и арифметико-логического устройства корректировки порядка результата, вход признака потери значимости мантиссы блока управления соединен с первым выходом шифратора нулей и с выходом признака потери значимости мантиссы уст- 55 ройства, третий выход блока управления соединен с управляющим входом арифметико-логического устройства обработки порядков, четвертый выход блока управления соединен с управляю50

второго операнда, Пр-разрядные выходы регистров первого и второго опег- рандов соединены соответственно с входами первой и второй групп арифг- метико-логического устройства обработки порядков, нормализатор, первый

5

0

5

информационный вход которого содержит п,+1 разрядов, а выход соединен с Пд, информационными входами регистра результата, отличающееся тем, что, с целью расширения функциональных возможностей устройства в части- дополнительного выполнения операций вычитания и деления над операндами с плавающей запятой, логических операций И, ИЛИ, НЕ, сложения по мсг- дулю два, а также повышения быстродействия за счет асинхронного режима выполнения операций, в него введены регистр кода операций, информационный, вход которого является первым информационным входом устройства, второй п -разрядный сдвигатель, первый информационный вход которого соединен с п -разрядными выходами регистра второго операнда, второй информационный вход второго .сдвигателя соединен с вторым информационным входом первого сдвигателя и с информационным выходом арифметико-логического устройства обработки порядков, управляю- вход второго сдвигателя соединен с первым вьпсодом блока управления, управляющий вход первого сдвигателя соединен с вторым выходом блока управления разрядные выходы второго сдвигателя соединены соответственно с информационными входами второй группы арифметико-логического устройства г обработки, мантисс, пусковой вход

устройства соединен с пусковым входом блока управления, вход дешифрации кода операции которого соединен с выходом регистра кода операции, вход оп0

5

ления соединен с выходом знакового разряда арифметико-логического устройства обработки порядков, вход раз решения коррекций порядка результата блока управления соединен с выходом старшего информационного разряда первого коммутатора и с первыми управляющими входами нормализатора.и арифметико-логического устройства корректировки порядка результата, вход признака потери значимости мантиссы блока управления соединен с первым выходом шифратора нулей и с выходом признака потери значимости мантиссы уст- 5 ройства, третий выход блока управления соединен с управляющим входом арифметико-логического устройства обработки порядков, четвертый выход блока управления соединен с управляю0

щим входом арифметико-логического ус ройства обработки мантисс, пятый вы- .ход блока управления соединен с управляющим входом второго коммутатора шестой выход блока управления соединен с управляющим входом первого коммутатора, седьмой выход блока управления соединен с тактовым входом регистра результата, восьмой выход блока управления соединен с входом разрешения записи регистра результата и с выходом готовности устройства девятый выход блока управления соеди нен с управляющим входом арифметико- логиче-ркого устройства корректировки порядка результата, П|,,-разрядный делитель, первый и второй информационные входа которого соединены соответственно с разрядными выходами ре- гистров первого и второго операндов, информационные входы первой группы первого коммутатора соединены соответственно с разрядными выходами арифметико-логического устройства обработки мантисс, информационные входы второй группы первого коммутатора соединены соответственно с разрядными выходами умножителя, информационные входы третьей группы первого коммутатора соединены соответственно с разрядными выходами делителя, информационный выход первого коммутатора соединен с информационным входом шифратора нулей, с первым инфор- мационным входом нормализатора и с первым информационным входом регистра результата, информационные входы первой группы второго коммутатора соединены соответственно с Пр-раз- рядными выходами регистра первого операнда, информационные входы вто- рой группы второго коммутатора соеди нены соответственно -с разрядными выходами арифметико-логического устройства обработки порядков, информационные входы третьей группы второго коммутатора соединены соответственно с Пр-разрядными выходами регистра второго операнда, второй выход шифратора нулей соединен с вторым информационным входом нормализатора .и с входами первой группы арифметико-логического устройства коррекции порядка результата входы второй группы которого соединены с выходами второго коммутатора, первый и второй выходы арифметико-логического устройства коррекции порядка результата соединены с выходами признаков переполнения порядка устрой- ртва 5 третий выход арифметико-логи° ческого устройства коррекции результата соединен с Пр информационным входом регистра результата, выход которого соединен с информационным выходом устройства и с первыми ( р)-разрядными входами регистров первого и второго операндов, второй (п,+Пр )-разрядный вход регистра первого операнда соединен с вторым ин- форма1Ц1Онным входом устройства, второй ( р)-разрядный вход регистра второго операнда соединен с третьим информационным входом устройства, управляющий вход регистра кода операций, соединен с первым управляющим входом устройства, второй и третий управляющие входы которого соединены соответственно с управляющими входами регистра первого операнда, управляющие входы регистра второго операнда соединены соответственно с четвертым и пятым управляющими входами устройства.

| Авторское свидетельство СССР № 758146, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительные процессы и системы | |||

| М.: Наука,1983,вып.1,с.96,рис.5 | |||

Авторы

Даты

1988-01-15—Публикация

1985-12-30—Подача