1

(21)4648793/24

(22)2J.12.88

(46) 23.04,91. Вюл. Р 15

(71)Киевский политехнический институт имс 50-летия Великой Октябрьской со- циалистической революции

(72)К.А. Семенов (53) 621.325(088.8)

(56) Авторское свидетельство СССР й 318939, кл„ Н 03 М 13/22, 1971.

Сброс Ввод

(54) УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ДВОИЧНЫХ СООБЩЕНИЙ

(57) Изобретение относится к классу устройств-кодеров двоичных сообщений и может найти применение в тех областях вычислительной техники и техники передачи данных, где повышение помехоустойчивости информации производится с помощью циклического кодирования, в частности в больших инАор

| название | год | авторы | номер документа |

|---|---|---|---|

| Корректор ошибок | 1989 |

|

SU1810909A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| Устройство для имитации сбоев | 1990 |

|

SU1836684A3 |

| Устройство для обмена информацией | 1986 |

|

SU1363228A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

2

Јь

00 СО

со

мационных и управляющих системах. Цель изобретения - повышение быстро действия устройства. Поставленная цель достигается тем, что устройство выполняет кодирование га-разрядного слова и выдачу контрольного слова, за tn-1 такт путем введения двунаправленного параллельного блока задания направления передачи и блока синхронизации Таким образом, в данном устройстве рабочий цикл уменьшаетИзобретение относится к классу стройств-кодеров двоичных сообщений 20 и может найти применение в тех областях вычислительной техники и техники передачи данных, где повышение помехоустойчивости информации произвоится с помощью циклического коди- 25 ования, в частности в больших инормационных и управляющих системах„

Цель изобретения - повышение быстродействия устройствао

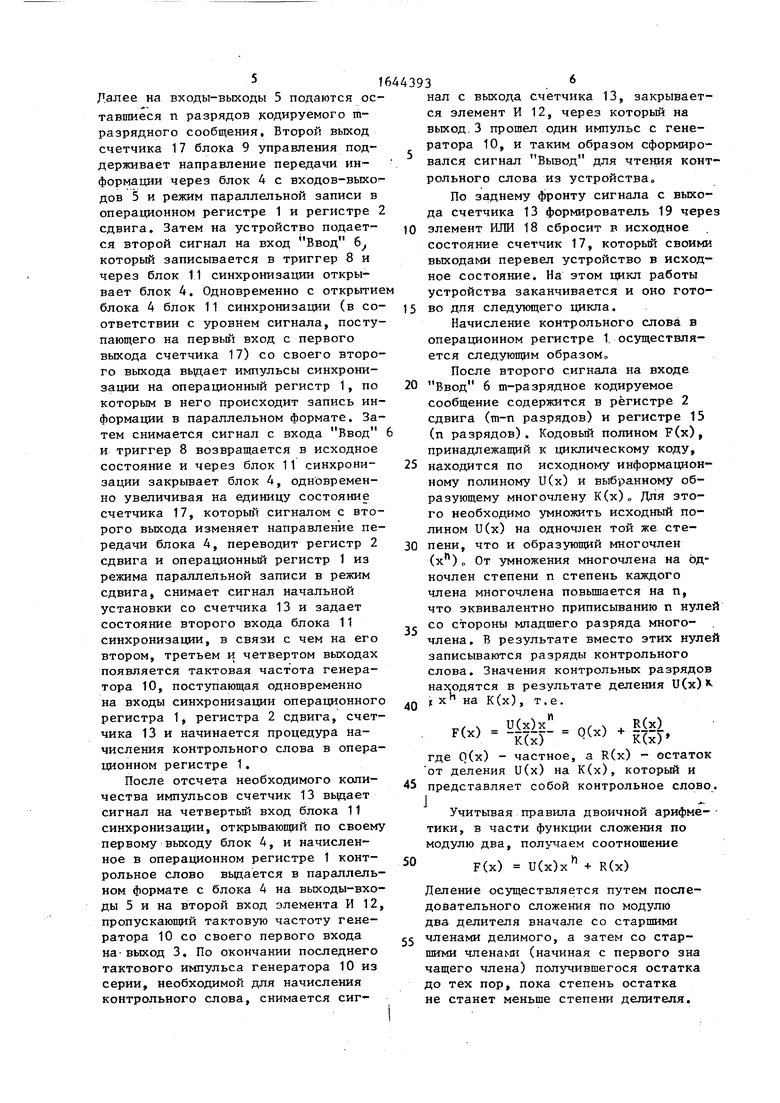

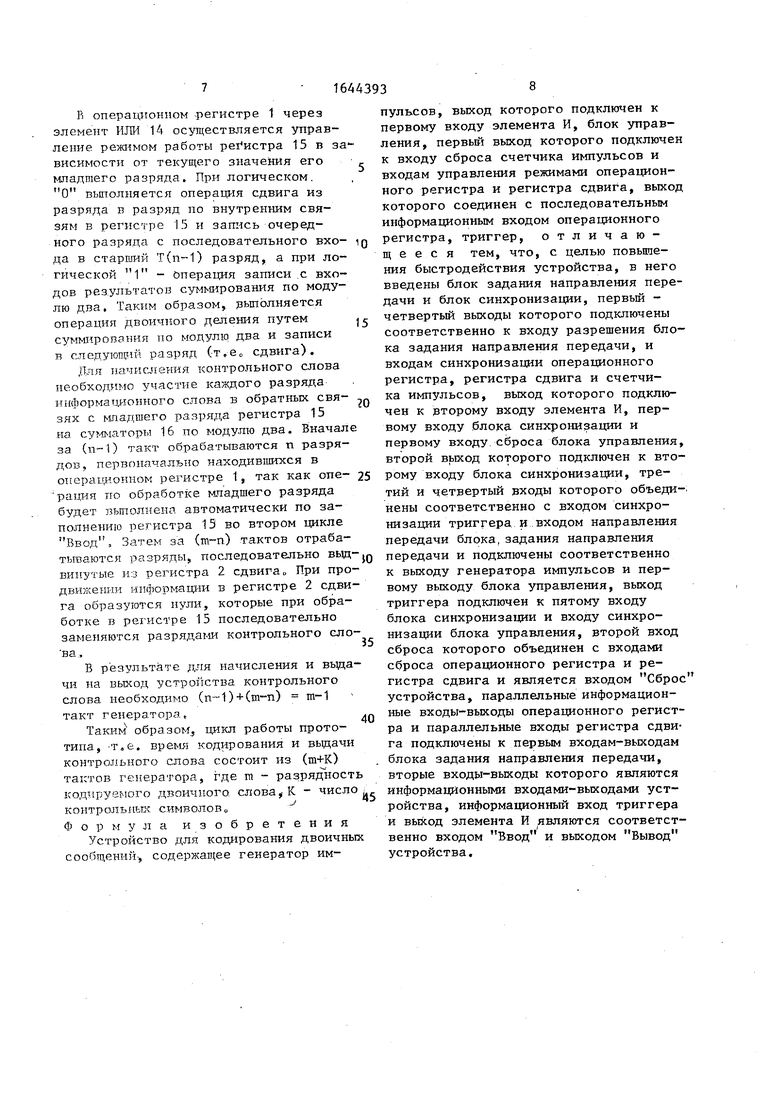

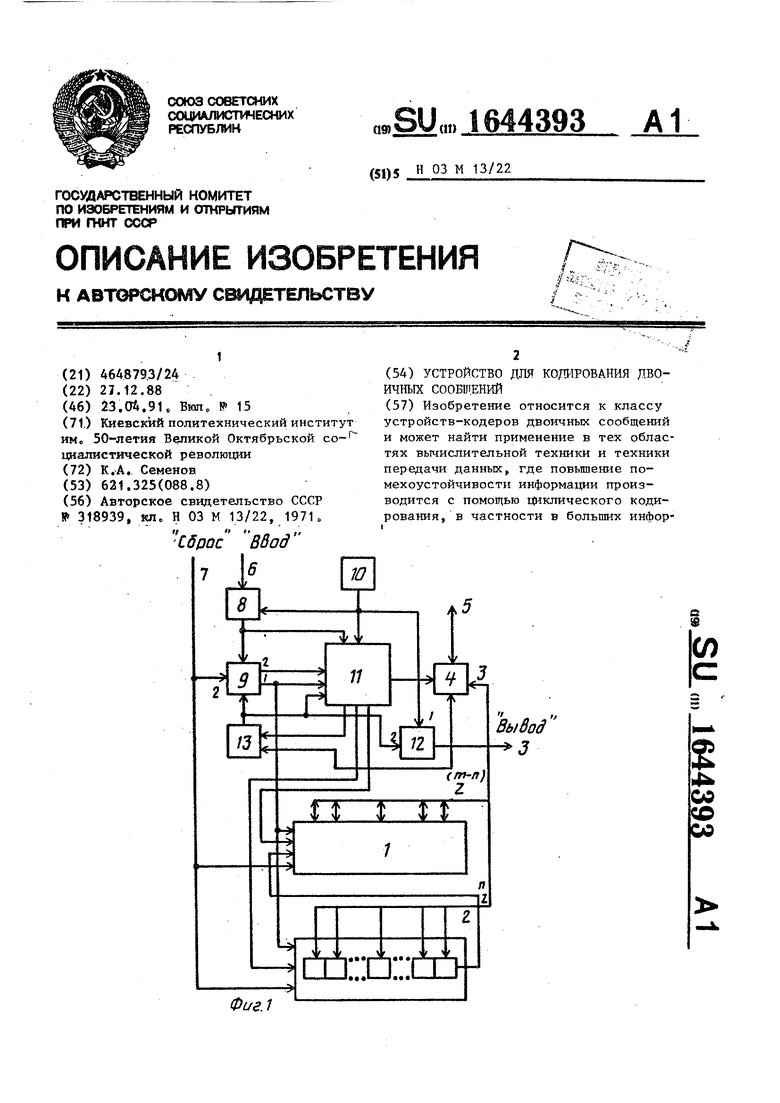

На фиг о 1 представлена функцио- 30 нальная схема устройства; на фиг.2 - функциональная схема операционного регистра; на фиг. 3 - функциональная схема блока управления.

Устройство содержит операционный ,5 регистр 1, регистр 2 сдвига, выход Вывод 3, блок 4 задания направления передачи, информационные входы- , выходы 5, вход Брод 6, вход Сброс 7, триггер 8, блок 9 управления, 0 генератор 10 импульсов, блок 11 синх-, ронизации, элемент И 12 и счетчик 13 импульсов,,

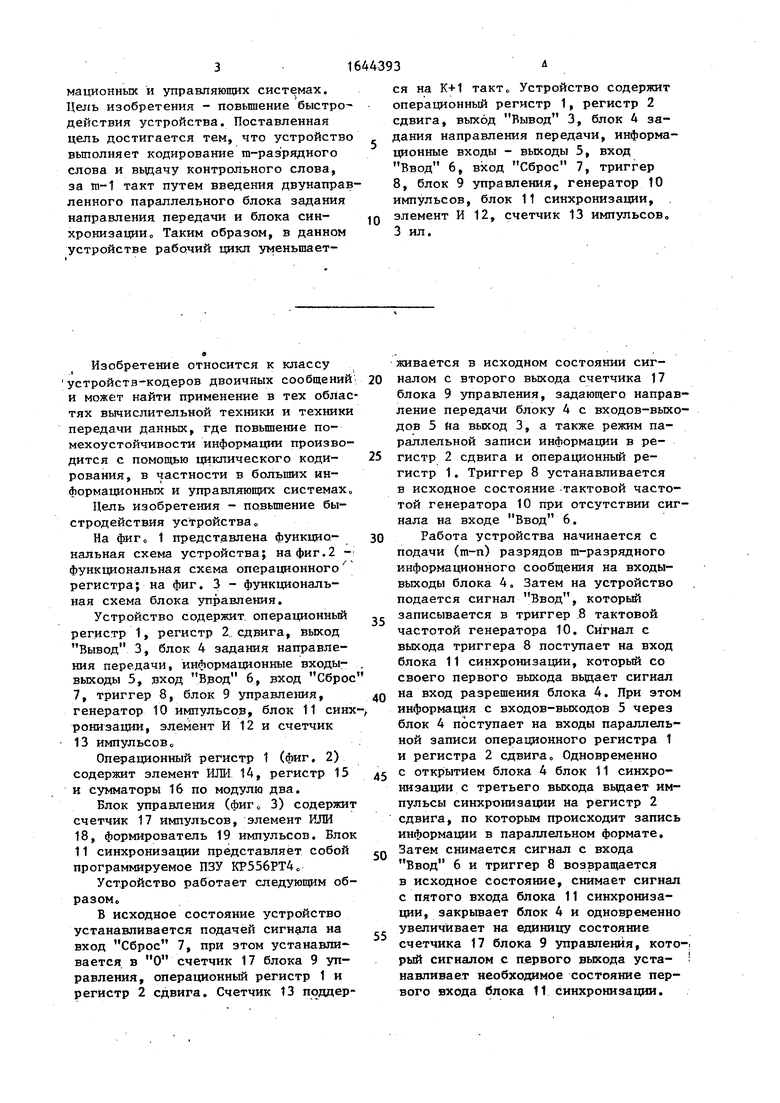

Операционный регистр 1 (фиг. 2) содержит элемент ИЛИ 14, регистр 15 д5 и сумматоры 16 по модулю два.

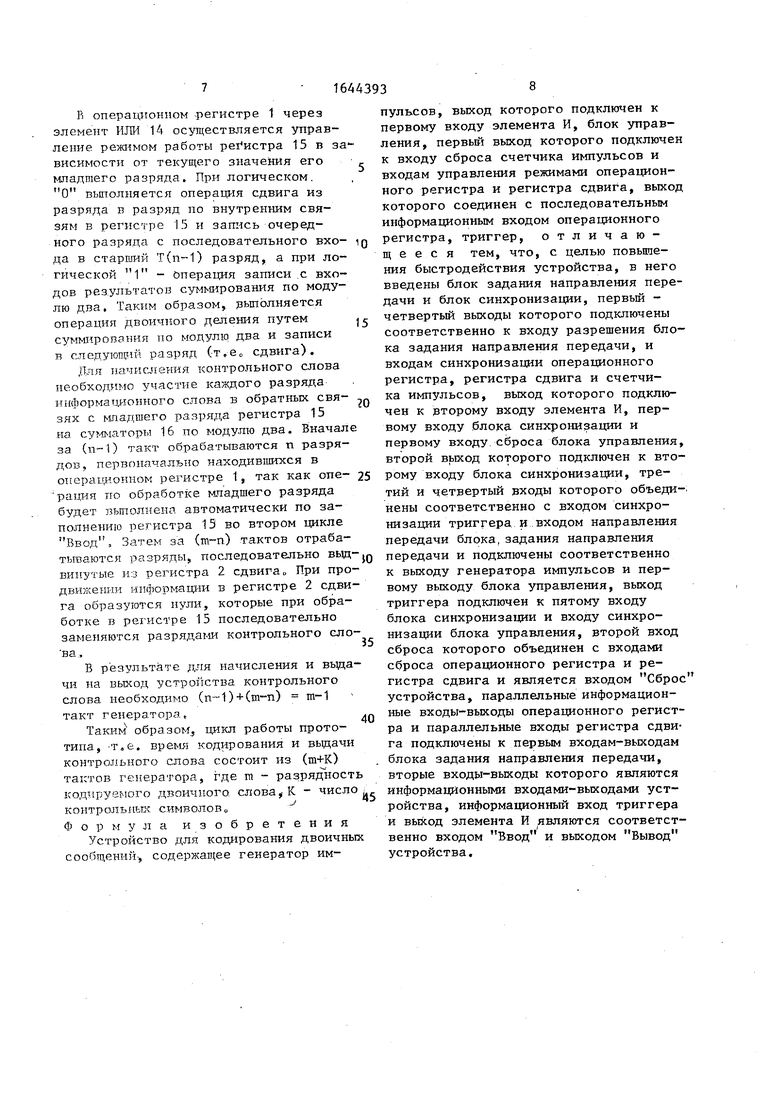

Блок управления (фиг„ 3) содержит счетчик 17 импульсов, элемент ИЛИ 18, формирователь 19 импульсов. Блок 11 синхронизации представляет собой Q программируемое ПЗУ КР556РТ4,

Устройство работает следующим образом

В исходное состояние устройство устанавливается подачей сигнала на вход Сброс 7, при этом устанавли- вается в О счетчик 17 блока 9 управления, операционный регистр 1 и регистр 2 сдвига. Счетчик 13 поддер55

J

ся на К+1 такт с Устройство содержит операционный регистр 1, регистр 2 сдвига, выход Вывод 3, блок 4 задания направления передачи, информационные входы - выходы 5, вход Ввод 6, вход Сброс 7, триггер 8, блок 9 управления, генератор 10 импульсов, блок 11 синхронизации, 10 элемент И 12, счетчик 13 импульсов 3 ил.

5 0

5

Q

5

живается в исходном состоянии сигналом с второго выхода счетчика 17 блока 9 управления, задающего направление передачи блоку 4 с входов-выходов 5 на выход 3, а также режим параллельной записи информации в регистр 2 сдвига и операционный регистр 1. Триггер 8 устанавливается в исходное состояние тактовой частотой генератора 10 при отсутствии сигнала на входе Ввод 6.

Работа устройства начинается с подачи (m-n) разрядов т-разрядного информационного сообщения на входы- выходы блока 4. Затем на устройство подается сигнал Ввод, который записывается в триггер 8 тактовой частотой генератора 10. Сигнал с выхода триггера 8 поступает на вход блока 11 синхронизации, который со своего первого выхода выдает сигнал на вход разрешения блока 4. При этом информация с входов-выходов 5 через блок 4 поступает на входы параллельной записи операционного регистра 1 и регистра 2 сдвига„ Одновременно с открытием блока 4 блок 11 синхронизации с третьего выхода выдает импульсы синхронизации на регистр 2 сдвига, по которым происходит запись информации в параллельном формате. Затем снимается сигнал с входа Ввод 6 и триггер 8 возвращается в исходное состояние, снимает сигнал с пятого входа блока 11 синхронизации, закрывает блок 4 и одновременно увеличивает на единицу состояние счетчика 17 блока 9 управления, кото-, рый сигналом с первого выхода уста- навливает необходимое состояние первого входа блока 11 синхронизации.

Далее на входы-выходы 5 подаются оставшиеся п разрядов кодируемого т- разрядного сообщения. Второй выход счетчика 17 блока 9 управления поддерживает направление передачи информации через блок 4 с входов-выходов 5 и режим параллельной записи в операционном регистре 1 и регистре 2 сдвига. Затем на устройство подается второй сигнал на вход Ввод б, который записывается в триггер 8 и через блок 11 синхронизации открывает блок 4. Одновременно с открытие блока 4 блок 11 синхронизации (в соответствии с уровнем сигнала, поступающего на первый вход с первого выхода счетчика 17) со своего второго выхода выдает импульсы синхронизации на операционный регистр 1, по которым в него происходит запись информации в параллельном формате. Затем снимается сигнал с входа Ввод и триггер 8 возвращается в исходное состояние и через блок 11 синхронизации закрывает блок 4, одновременно увеличивая на единицу состояние счетчика 17, который сигналом с второго выхода изменяет направление передачи блока 4, переводит регистр 2 сдвига и операционный регистр 1 из режима параллельной записи в режим сдвига, снимает сигнал начальной установки со счетчика 13 и задает состояние второго входа блока 11 синхронизации, в связи с чем на его втором, третьем и четвертом выходах появляется тактовая частота генератора 10, поступающая одновременно на входы синхронизации операционного регистра 1, регистра 2 сдвига, счетчика 13 и начинается процедура начисления контрольного слова в операционном регистре 1.

После отсчета необходимого количества импульсов счетчик 13 выдает сигнал на четвертый вход блока 11 синхронизации, открывающий по своему первому выходу блок 4, и начисленное в операционном регистре 1 контрольное слово выдается в параллельном формате с блока 4 на выходы-входы 5 и на второй вход элемента И 12, пропускающий тактовую частоту генератора 10 со своего первого входа на выход 3. По окончании последнего тактового импульса генератора 10 из серии, необходимой для начисления контрольного слова, снимается сиг1644393

нал с выхода счетчика 13, закрывается элемент И 12, через который на выход 3 прошел один импульс с генератора 10, и таким образом сформировался сигнал Вывод для чтения контрольного слова из устройства

По заднему фронту сигнала с выхода счетчика 13 формирователь 19 через

10 элемент ИЛИ 18 сбросит в исходное состояние счетчик 17, который своими выходами перевел устройство в исходное состояние. На этом цикл работы устройства заканчивается и оно гото-

5 во для следующего цикла.

Начисление контрольного слова в операционном регистре 1 осуществляется следующим образом„

После второго сигнала на входе

20 Ввод 6 m-разрядное кодируемое сообщение содержится в регистре 2 сдвига (m-n разрядов) и регистре 15 (п разрядов). Кодовый полином F(x), принадлежащий к циклическому коду,

5 находится по исходному информационному полиному U(x) и выбранному образующему многочлену К(х)„ Для этого необходимо умножить исходный полином U(x) на одночлен той же сте0 пени, что и образующий многочлен

(хп)„ От умножения многочлена на одночлен степени п степень каждого члена многочлена повышается на п, что эквивалентно приписыванию п нулей со стороны младшего разряда многочлена. В результате вместо этих нулей записываются разряды контрольного слова. Значения контрольных разрядов находятся в результате деления U(x). f х на К(х), т.е.

F(x), H«f:, оы +1$,

где 0(х) - частное, a R(x) - остаток от деления U(x) на К(х), который и 5 представляет собой контрольное слово.

J

Учитывая правила двоичной арифметики, в части функции сложения по модулю два, получаем соотношение

0 F(x) U(x)xh + R(x)

Деление осуществляется путем последовательного сложения по модулю два делителя вначале со старшими 5 членами делимого, а затем со старшими членами (начиная с первого зна чащего члена) получившегося остатка до тех пор, пока степень остатка не станет меньше степени делителя.

5

0

В операционном регистре 1 через элемент ИЛИ 14 осуществляется управление режимом работы регистра 15 в зависимости от текущего значения его младшего разряда. При логическом О выполняется операция сдвига из разряда в разряд по внутренним связям в регистре 15 и запись очередного разряда с последовательного вхо- да в старший Т(п-1) разряд, а при логической 1 - операция записи с входов результатов суммирования по модулю два. Таким образом, выполняется операция двоичного деления путем 1 суммирования по модулю два и записи в следующий разряд (т,е„ сдвига).

Д 1Я начисления контрольного слова необходимо участие каждого разряда информационного слова в обратных свя- зях с младшего разряда регистра 15 на сумматоры 16 по модулю два. Вначале за (n-i) такт обрабатываются п разрядов, первоначально находившихся в операционном регистре 1, так как one- 2 рация по обработке младшего разряда будет выполнен автоматически по заполнению регистра 15 во втором цикле Ввод, за () тактов отрабатываются разряды, последовательно ВЫДвшплые из регистра 2 сдвига„ При продвижении информации в регистре 2 сдвига образуются нули, которые при обработке в регистре 15 последовательно заменяются разрядами контрольного сло- ва,

В результате для начисления и выдачи на выход устройства контрольного слова необходимо (n-1)+(m-n) m-1

4

такт генератора

Таким4 образом цикл работы прототипа, т.о. время кодирования и выдачи контрольного слова состоит из (т+К) тактов генератора, где то - разрядность кодируемого двоичного слова у К - число контрольных символов,, J Формула изобретения

Устройство для кодирования двоичных сообщений, содержащее генератор им

Q 5 Q

0

пульсов, выход которого подключен к первому входу элемента И, блок управления, первый выход которого подключен к входу сброса счетчика импульсов и входам управления режимами операционного регистра и регистра сдвига, выход которого соединен с последовательным информационным входом операционного регистра, триггер, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок задания направления передачи и блок синхронизации, первый - четвертый выходы которого подключены соответственно к входу разрешения блока задания направления передачи, и входам синхронизации операционного регистра, регистра сдвига и счетчика импульсов, выход которого подключен к второму входу элемента И, первому входу блока синхронизации и первому входу сброса блока управления, второй выход которого подключен к второму входу блока синхронизации, третий и четвертый входы которого объединены соответственно с входом синхронизации триггера и входом направления передачи блока,задания направления передачи и подключены соответственно к выходу генератора импульсов и первому выходу блока управления, выход триггера подключен к пятому входу блока синхронизации и входу синхронизации блока управления, второй вход сброса которого объединен с входами сброса операционного регистра и регистра сдвига и является входом Сброс устройства, параллельные информационные входы-выходы операционного регистра и параллельные входы регистра сдвига подключены к первым входам-выходам блока задания направления передачи, вторые входы-выходы которого являются информационными входами-выходами устройства, информационный вход триггера и выход элемента И являются соответственно входом Ввод и выходом Вывод устройства.

1в

т

Фиг. 2

77

Фиг.З

Авторы

Даты

1991-04-23—Публикация

1988-12-27—Подача