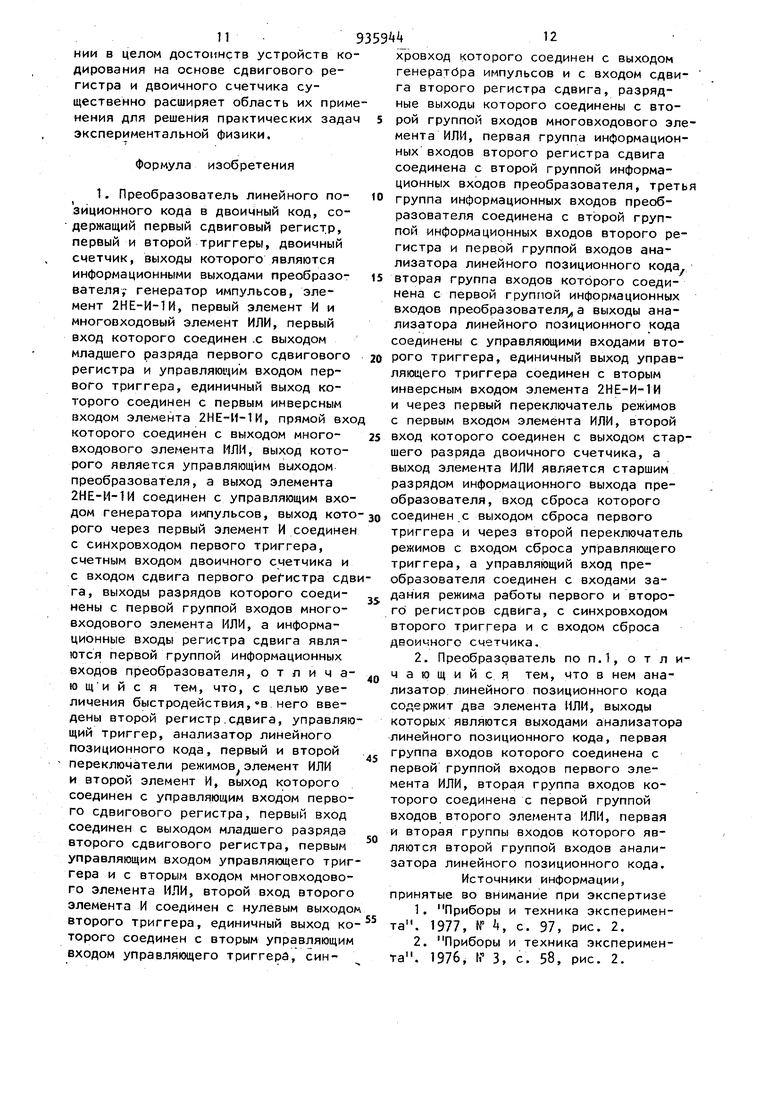

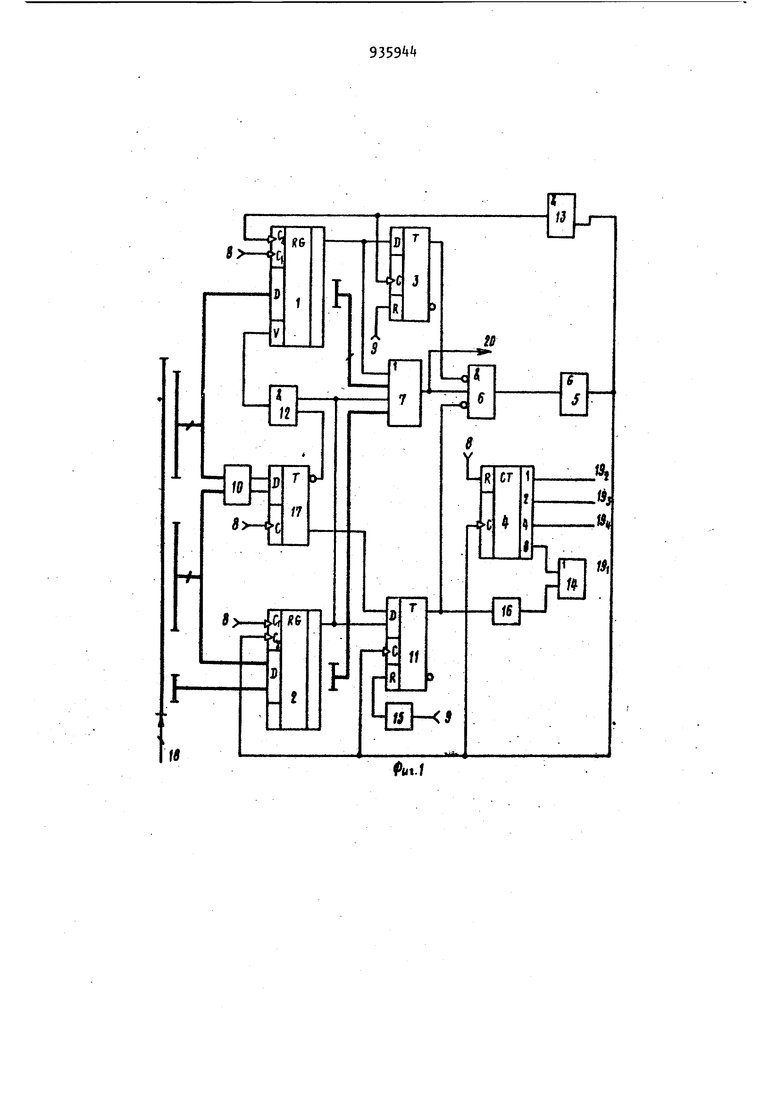

5) ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНОГО ПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении уст ройств преобразования и кодирования информации, получаемой в многокоорди натных и многодатчиковых системах. Известен преобразователь, содержащий регистр сдвига счетчик, триггер опроса, триггер управления, элементы И, ИЛИ 1. Недостаток известного преобразователя состоит в необходимости больших аппаратных затрат. Наиболее близким по технической сущности и схемному построению к предлагаемому является устройство пр образования линейного позиционного кода в двоичной код, содержащее сдви говый регистр, выход младшего разряда которого соединен с информацйон ным входом синхронного триггера, дво ичный счетчик кодирования, генератор импульсов, к выходу которого под ключены входы синхронизации сдвигового регистра и триггера и счетный вход двоичного счетчика, управляющий вход генератора импульсов подключен к выходу элемента запрета, сигнальный вход которого соединен с выходом многовходного элемента ИЛИ, сигнальные входы которого подключены к выходам сдвигового регистра, а вход Запрет подключен к выходу триггера. Устройство содержит также формироватьель сигнала записи данных в регистр, вход которого связан с соответствующим входом сдвигового регистра, формирователь сигнала сброса, выход которого соединен с установочным R входом триггера, и блок управления, выход которого (для перевода регистра из режима записи в режим сдвига и наоборот) соединен с управляющим входом сдвигового регистра 2. Недостатком известного преобразователя является сравнительно невысокое его быстродействие, которое линейно убывает с увеличением длины кодируемого слова и соответственно с увеличением разрядности N-сдвигового регистра, вследствие-чего среднее время преобразования, обеспечиваемое известным устройством при кодировании слов, содержащих одну еди ницу в позиционном коде, оказывается равным f 0,5-()-(1/Fc), F - частота тактовых (сдвигающих где импульсов. Сравнительно большое время преобразования известного устройства существенно сужает область его применения, поскольку средняя скорость кодирования данных с многодатчиковых систем при этом характерном для практики случае .в лучшем случае оказывает ся порядка/ 0,5 мГц/16-разрядное ело. во, что вынуждает в целом ряде практических случаев переходить либо к более быстродействующим способам преобразования кодов, либо к использованию разравнивающего буфера с вытекающим отсюда, как правило, отказом от асинхронного способа считывания данных с многодатчиковых систем. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем что в преобразователь линейного позиционного кода в двоичный код содержащий первый сдвиговый регистр, первый и второй триггеры, двоичный счетчик, выходы которого являются информационными выходами, преобразователя, генератор импульсов, элемент 2НЕ-И-1И первый элемент И и многовходовой элемент ИЛИ, первый вход которого соеди нен с выходом младшего разряда первого сдвигового регистра и управляющим входом первого триггера, единич ный выход которого соединен с первым инверсным входом элемента 2НЕ-И-1И, прямой вход которого соединен с выходом многовходового элемента ИЛИ, выход которого является управляющим выходом преобразователя, а выход эле мента 2НЕ-И-1И, соединен с управляющим входом генератора импульсов, выход которого через первый элемент И соединен с синхровходом первого три1- гера, счетным входом двоичного счетчика и с входом сдвига первого регистра сдвига, выходы разрядов которого соединены с первой группой входов многовходового элемента ИЛИ, а информационные входы ре гистра сдвига являются первой группо Э3 4 информационных входов преобразователя введены второй регистр сдвига, управляющий тpиггep,анализатор линейного позиционного кода, первый и второй переключатели режимов, элемент ИЛИ и второй элемент И, выход которого соединен с управляющим входом первого сдвигового регистра, первый вход соединен с выходом младшего разряда второго сдвигового регистра, первым управляющим входом управляющего триггера и с вторым входом многовходового элемента ИЛИ, второй вход второго элемента И соединен с нулевым выходом второго триггера, единичный выход которого соединен со вторым управляющим входом управляющего триггера, синхровход которого соединен с выходом генератора импульсов и с входом сдвига второго регистра сдвига, разрядные выходы которого соединены со второй группой входов многовходового элемента ИЛИ, первая группа информационных входов второго регистра сдвига соединена со второй группой информационных входов преобразователя, третья группа информационных входов преобразователя соединена со второй группой информационных входов второго регистра и первой группой входов анализатора линейного позиционного кода, вторая группа входов которого соединена с первой группой информационных входов преобразователя, а выходы анализатора линейного позиционного кода соединены с управляющими входами второго триггера, единичный выход управляющего триггера соединен со вторым инверсным входом элемента 2НЕ-И-1И и через первый переключатель режимов с первым входом элемента ИЛИ, второй вход которого соединен с выходом старшего разряда двоичного счетчика, а выход элемента ИЛИ является старшим разрядом информационного выхода преобразователя, вход сброса которого соединен с входом сброса первого триггера и через второй переключатель режимов со входом сброса управляющего триггера, а управляющий вход преобразователя соединен с входами задания режимов работы первого и второго регистров сдвига, с синхровходом второго триггера и с входом сброса двоичного счетчика, а также тем, что в нем анализаторлинейного позиционного кода содержит два элемента ИЛИ, выходы которых являются выходами анализатора линейного позиционного кода, первая группа входов которого соединена с первой группой входов первого элемента ИЛИ, вторая группа входов которого соединена с первой группой входов второго элемента ИЛИ первая и вторая группы входов которого являются второй группой входов анализатора линейного позиционного кода. На фиг. 1 представлена блок-схема предложенного преобразователя линейного Позиционного кода в двоичный ко для случая 16-разрядного позиционного кода (п); на фиг. 2 - блок-схе ма анализатора линейного позиционного кода. Преобразователь содержит 16-раз- рядный сдвиговый регистр (), состоящий из двух {1-ого и 2-ГО) восьми разрядных регистров со своими незави симыми входами управления, первый триггер 3, счетчик k, генератор импульсов 5, элемент 2НЕ-И-1И 6, много входовый элемент ИЛИ 7, первый управляющий, вход 8 преобразователя, вход сброса 9 анализатор 10 линейно го позиционного кода, второй триггер 11, первый и второй элементы И 12 и 13, элемент ИЛИ 1t, первый и второй переключатели режимов 15 и третий триггер 17. Входной код посту пает на преобразователь через информационный вход 18 преобразователя, выходной код формируется на выходах преобразователя, а сигнал запроса ин формации на управляющем выходе 20 преобразователя. Анализатор 10 позиционного кода (фиг.2) построен на двух элементах ИЛИ 21 и 22,а переключатели 15 и 1б в этом слууае могут быть вы полнены в виде перемычек, при этом для конкретности даны обозначения входов управления сдвигового регистра применительно к универсальному сдвигово му регистру типа 155ИР1, а именно; Vrj - последовательный вход регистра С - вход синхронизации для режима записи данных в регистр, вход синхронизации для режима сдвига содержимого регистра, вход управления режимом работы регистра. Устройство работает следующим образом . В момент занесения в сдвиговые ре гистры 1 и 2 входных данных, представленных в линейном позиционном ко де, по управляющему входу 8 сигнал для записи данных одновременно поступает на вход синхронизации триггера 17, задающего режим перестройки преобразователя. В случае, когда на оба информационных входа этого триггера 17 от анализатора 10 поступают единичные уровни, то триггер режима взводится и блокирует при этом три1- гер t1, а с другой стороны - отпирает элемент И 12, благодаря чему содержимое сдвигового регистра 2 в такт со сдвигающими импульсами от генератора 5 передается в сдвиговый регистр 1. Таким образом, преобразователь в этом случае работает аналогично известному устройству,.а именно - по достижении лидирующей единицы первого разряда сдвигового регистра и соответственно при срабатывании от следующего тактового импульса : триггера 3 единичный уровень с его выхода поступает на первый вход запрета элилента 7 и через элемент 6 блокирует дальнейшую работу генератора тактовых импульсов 5. При этом на выходах счетчика 4 устанавливается двоичнь1Й код соответствующего разряда линейного позиционного кода. После считывания в накопитель (ЭВМ) этого двоичного кода по входу 9 на установочный R вход триггера 3 поступает сигнал сброса,в результате чего снимается Запрет с элемента 7. Если при этом в сдвиговых регистрах 1-2 все еще содержатся единицы, то это вновь ведет к появлению разрешающего уровня на выходе элемента 7 и соответственно к включению генератора В- После окончания преобразования каждого слова от многовходового элемента ИЛИ 7 подается сигнал на управ ляющий выход 20, в ответ на который через вход 8 поступит:разрешающий уровень для генерации сигнала записи позиционного кода уже следующего слова, посредством которого одновременно осуществляется установка счетчика k в начальное состояние. В случае, если при занесении новых данных в сдвиговые регистры, от анализатора 10 на хотя бы один из двух информационных входов триггера режима 17 поступает нулевой уровень то преобразователь переходит в режим раздельного кодирования с помощью двух уже независимьр в этом случае регистров 1 и 2. Нулевой сигнал с прямого выхода триггера 17 в этом случае блокирует элемент 12i так что содержимое второго регистра уже не может быть передано (сдвинуто) в первый регистр 1 в теч ние всего цикла преобразования. В то же время триггер режима 17 в этом случае снимает блокировку со второго информационного входа триггера 11, в результате чего дополнительно введенный триггер 11 начинает выполнять те же функции, что и триггер 3 но только для логических единиц второй половины позиционного кода , выводимых из 9-8 )ого разряда сдвигового регистра. Одновременно триггер 11 в этом случае выполняет функции датчика сигнала переноса, к старшему разряду двоичного кода для логических единиц старшей половины позиционного кода, которые и обуславливают срабатывание триггера 11. При срабатывании триггера 1( единичный уровень с его прямого выхода приводит к останову генератора импульсов 5 и одновременно чер второй переключатель 16 поступает на вход элемента ИЛИ 14, Таким образом, если, например, срабатывание триггера 1Т происходит от логической единицы в разряде линейного позиционного кода, то двоичный счетчик просчитывает при этом лиш 6 импульсов, его выходах (при начальной установке счетчика в нуле вое состояние) устанавливается двоичный код ОНО. Благодаря искусственному приданию к этому коду через элементы 16 и Н сигнала переноса н выходах преобразователя устанавливается код 1110, отвечающий разрядности преобразуемого линейного позиционного кода. Принципиальным моментом для пред лагаемого устройства является обеспечение такого режима, при котором в случае наличия в позиционном коде нескольких логических единиц осущес вляется строго упорядоченное преобразование в двоичный код номеров по зиционного кода в порядке возрастания их весов. Это обеспечивает анализатор структуры линейного позицио ного кода 10 ,фиг.2). В случае есл одновременно от,8-входовых элементов ИЛИ 22 и 21, на которых строится анализатор 10, поступают единичные уровни, то преобразователь рабо 48 тает в обычном режиме. Если же, например, в позиционном коде содержатся две единицы во 2-ом и 13-ом его разрядах, то ггреобразование осуществляется раздельно-сначала передается код 0010, а затем после сброса триггера 3 и повторного запуска преобразователя на выход передается код 1101. При подобном построении анализатора исключается возможность одновременного срабатывания обоих триггеров 3 и 11, поэтому переключатели режимов в этом случае могут быть выполнены в виде перемычек. В еще большей степени уменьшение вероятности работы преобразователя в обычном режиме достигается при сужении зоны охвата анализатора 10, т.е. при отключении (обесточивании)1-ой входной клеммы у элемента ИЛИ-22 при одновременном отключении от 14-ра.зрядного параллельного входа сдвигового регистра восьмого сигнального входа у элемента ИЛИ 21. В этом случае оба переключателя 15 и 1б выполняются в виде элементов запрета-элемент 1б для обеспечения приоритетной передачи в накопитель данных от первого регистра, а элемент 15 - для обеспечения селективного сброса триггера 3 после считывания этих данных. Для обеспечения селективного сброса триггера 3 в ситуации, когда в режиме раздельного кодирования одновременно срабатывают оба триггера 3 и 11.вводится четвертый синхронный триггер ( не показан) с логикой 2И на информационных входах, каждый из входов которого соединен с прямым выходом триггеров 3 и 11. При этом вход синхронизации этого четвертого тактируемого триггера управляется сигналами сброса со входа 9- Во всех вариантах обеспечение высокой помехоустойчивости работы преобразователя достигается за счет выполнения синхронного триггера 17 в виде триггера fl-V типа (фиг.2), у которого информационный V-вход соединяется с вхсздом 8, на котором (в зависимости от типа используемого сдвигового регистра ) вырабатывается сигнал задания режима сдвига содержимого регистров 1-2. В частности при использовании сдвигового регистра с двумя независимыми входами синхронизации один для режима записи, а другой для режима сдвига содержимого регистра (как, например, у сдвигового регистра типа 155ИР1), V-вход синхронного триггера 17 соединяется непосредственно с тем выходом триггера 17, который соединен с У2,-управляющим входом сдвигового регистра. Таким образом, при задании от триггера 17 на входы Уд сдвиговых регистров 1-2 нулевого уровня, при :котором регистр переводится в режим сдвига своего со держимого, одновременно за счет блокировки при этом триггера 17 по его информационному входу U исключается какая-либо возможность случайной переустановки этого триггера в течение всего цикла преобразования. Сопоставительные экспериментальные испытания предлагаемого преобразователя линейного позиционного ,кода в двоичной код с известным преобразователемТ выполненных на основе мик росхем одного и того же типа (155 серия) показывают надежную и помехоустойчивую работу предлагаемого кодировщика вплоть до той we предельной частоты следования тактовых импульсо (с той же скважностью 1/З), при котс5рой в известном преобразователе t уже начинают иметь место сбои. Таким образом в условиях обеспечения предлагаемым преобразователем той же рабочей тактовой частоты сдвигающих импульсов, что и в известном за счет нового принципа шифрации в предлагаемом устройстве скорость,, преобразования линейного позиционного кода одиночных событий в двоичный код возрастает вдвое. При этом благодаря сохранению в предлагаемом преобразователе (при подключении к нему стандартного блока со вторым двоичным сметчиком возможности одноаремённого кодирования также числа подряд следующих единиц в смежных разрядах позиционного кода сохраняется также одно из основных достоинств преобразователя на основе сдвигового регистра - возможность ус корения передачи данных и уменьшения объема занимаемой памяти при шифрации кластерных событий, когда попадание заряженной частицы в многопроволочный детектор, например, при ее наклонном прохождении через детектор приводит к срабатыванию нес кольких подряд следующих каналов регистрации. Вместе с этим поскольку вероятность того, что одновременно 9 + попадание двух и тем более трех заряженных частиц в одну и ту же опрашиваемую группу из двух датчиков (обычно n или 5) на практике достаточно мала .(так как их регистрация производится лишь во время строб-импульса длительностью порядка бОнс, а сама зона -охвата одной группой составляет всего несколько сантиметров) , то и в случае наличия в общем массиве обрабатыЕзаемых данных подобного типа слов с разнесенны,1и единицами в целом средняя скорость преобразования данных, обеспечиваемая предлагаемым устройством по отношению к известному, практически вдвое выше. Действительно предлагаемый преобразователь работает в таком же режиме что и известный лишь в том случае, когда разнесенные между собой единицы содержатся как в первой половине линейного позиционного кода (т.е. до Z eго-разряда) , так и одновременно в третьей его четверти, т.е. с () по 32 его разрядах. Между тем наиболее ощутимый выигрыш в скорости преобразования, т.е. в числе сдвигающих тактов, соответствует такой ситуации, когда единицы в линейном позиционном коде разнесены между собой на значите;льное число разрядов,, например, когда единица размещена в первой четверти позиционного кода, а вторая находится в последней четверти преобразуемого кода. Именно при такой структуре линейного позиционного кода, когда наиболее важно выиграть во времени преобразования, в предлагаемом преобразователе происходит его перестройка, и без использования каких-либо блокировочных обратных связей происходит раздельная и одновременная шифрация обоих событий. Более того.усиление положительного эффекта при преобразовании подобных структур линейного позиционного кода может быть в еще большей степени усилено при дополнительном использовании в анализаторе линейного позиционного кода уже добавочных элементов 2 VlЛИ-HE для анализа взаиморасположения единиц внутри запретной зоны во 2-3 четвертях линейного позиционного кода и в последней его четверти до 1 разряда, Увеличение средней скорюсти кодирования в предлагаемом преобразователе практически вдвое при сохранеНИИ в целом достоинств устройств ко дирования на основе сдвигового регистра и двоичного счетчика существенно расширяет область их прим нения для решения практических зада экспериментальной физики. Формула изобретения 1. Преобразователь линейного позйционного кода в двоичный код, содержащий первый сдвиговый регистр, первый и второй триггеры, двоичный счетчик, выходы которого являются информационными выходами преобразователяу генератор импульсов, эле мент 2НЕ-И-1И, первый элемент И и многовходовый элемент ИЛИ, первый вход которого соединен .с выходом младшего разряда первого сдвигового регистра и управляющим входом первого триггера, единичный выход которого соединен с первым инверсным входом элемента 2НЕ-И-1И, прямой вх которого соединен с выходом многовходового элемента ИЛИ, выход которого является управляющим выходом преобразователя, а выход элемента 2НЕ-И-1И соединен с управляющим вхо дом генератора импульсов, выход кото рого через первый элемент И соединен с синхровходом первого триггера, счетным входом двоичного счетчика и с входом сдвига первого регистра сдв га, выходы разрядов которого соединены с первой группой входов многовходового элемента ИЛИ, а информационные входы регистра сдвига являются первой группой информационных входов преобразователя, о т л и ч аю щи и с я тем, что, с целью увеличения быстродействия,В.него введены второй регистр.сдвига, управляю щий триггер, анализатор линейного позиционного кода, первый и второй переключатели режимов элемент ИЛИ и второй элемент И, выход которого соединен с управляющим входом первого сдвигового регистра, первый вход соединен с выходом младшего разряда второго сдвигового регистра, первым управляющим входом управляющего три1- гера и с вторым входом многовходового элемента ИЛИ, второй вход второго элемента И соединен с нулевым выходо второго триггера, единичный выход ко торого соединен с вторым управляющим входом управляющего триггера, синхровход которого соединен с выходом генератбра импульсов и с входом сдвига второго регистра сдвига, разрядные выходы которого соединены с второй группой входов многовходового элемента или, первая группа информационных входов второго регистра сдвига соединена с второй группой информационных входов преобразователя, третья группа информационных входов преобразователя соединена с второй группой информационных входов второго регистра и первой группой входов анализатора линейного позиционного кода, вторая группа входов которого соединена с первой группой информационных входов преобразователя а выходы анализатора линейного позиционного кода соединены с управляющими входами второго триггера, единичный выход управляющего триггера соединен с вторым инверсным входом элемента 2НЕ-И-1И и через первый переключатель режимов с первым входом элемента ИЛИ, второй вход которого соединен с выходом старшего разряда двоичного счетчика, а выход элемента ИЛИ является старшим разрядом информационного выхода преобразователя, вход сброса которого соединен с выходом сброса первого триггера и через второй переключатель режимов с входом сброса управляющего триггера, а управляющий вход преобразователя соединен с входами задания режима работы первого и второгс регистров сдвига, с синхровходом второго триггера и с входом сброса двоичного счетчика. 2, Преобразователь по п.1, о т л ичающийся, тем, что в нем анализатор линейного позиционного кода содержит два элемента ИЛИ, выходы которых являются выходами анализатора линейного позиционного кода, первая группа входов которого соединена с первой группой входов первого элемента ИЛИ, вторая группа входов которого соединена с первой группой входов второго элемента ИЛИ, первая и вторая группы входов которого являются второй группой входов анализатора линейного позиционного кода. Источники информации, принятые во внимание при экспертизе 1, Приборы и техника эксперимента. 1977, № k, с. 97, рис. 2. 2. Приборы и техника эксперимента. 1976, 3, с. 58, рис. 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| Преобразователь кода | 1980 |

|

SU1168922A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Шифратор позиционного кода | 1989 |

|

SU1642588A1 |

| Преобразователь кодов | 1987 |

|

SU1450112A1 |

| Преобразователь @ -значного двоичного кода в @ -значный | 1983 |

|

SU1156057A1 |

Авторы

Даты

1982-06-15—Публикация

1980-07-09—Подача