Изобретение относится к радиотехнике и может быть использовано в системах передачи информации.

Цель изобретения - повышение пропускной способности канала связи путем увеличения коэффициента сжатия.

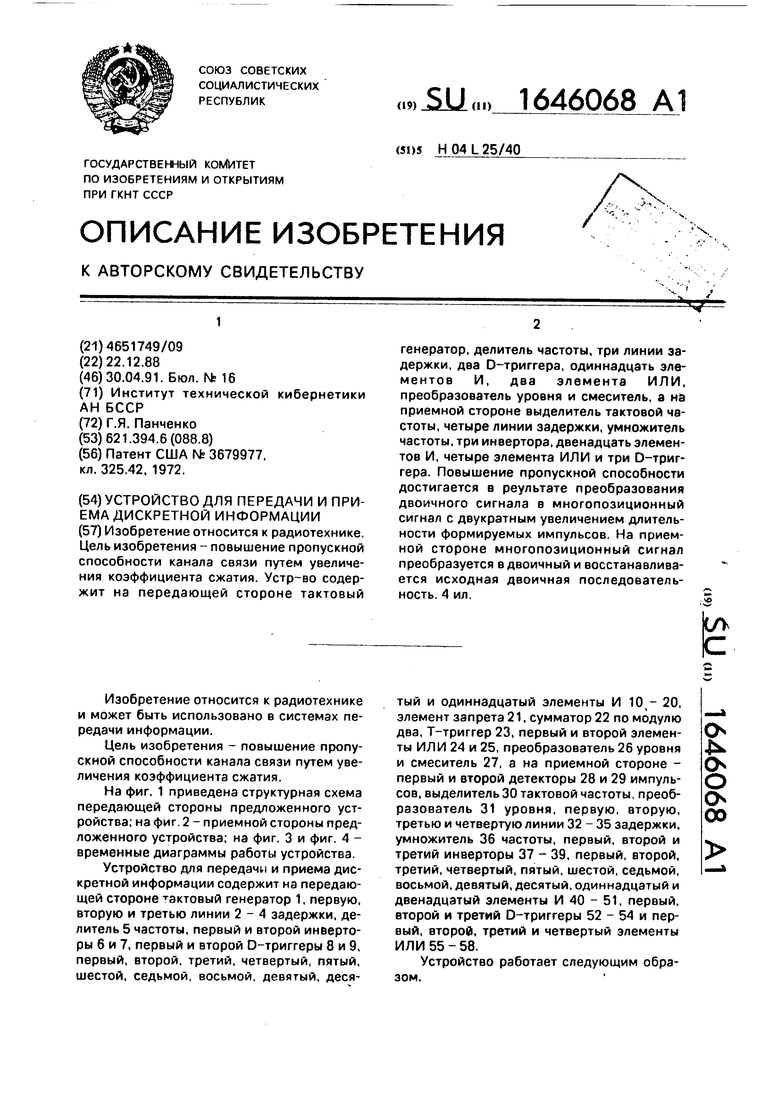

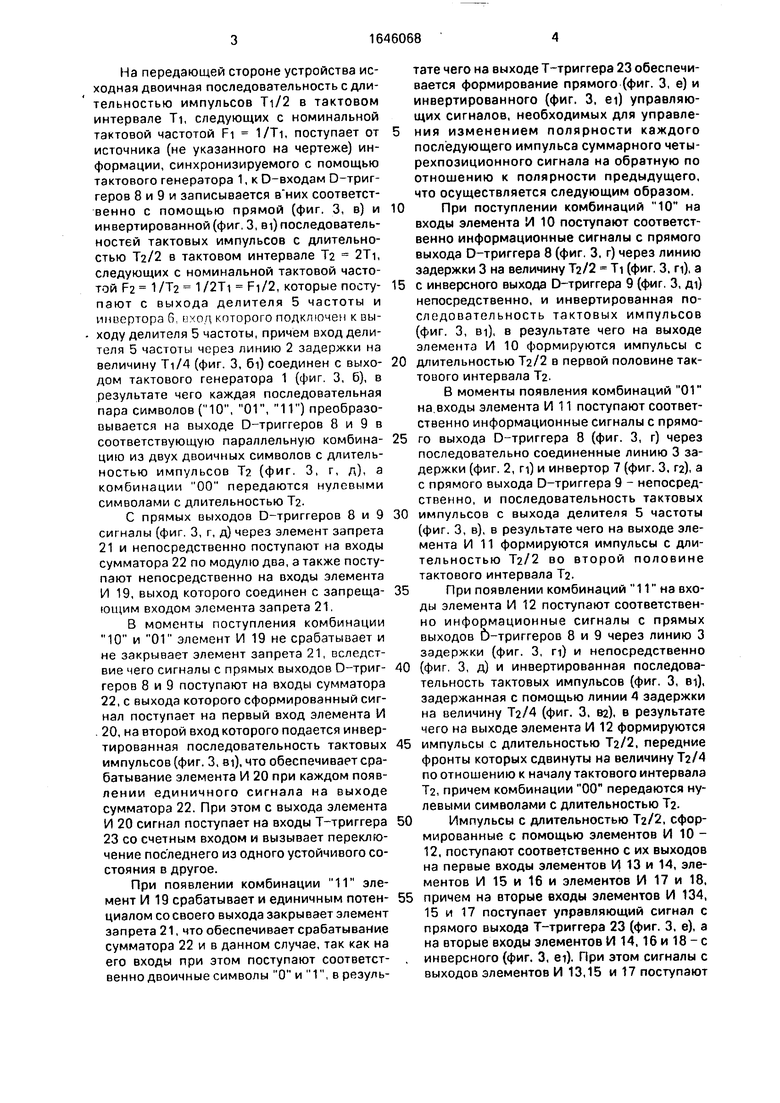

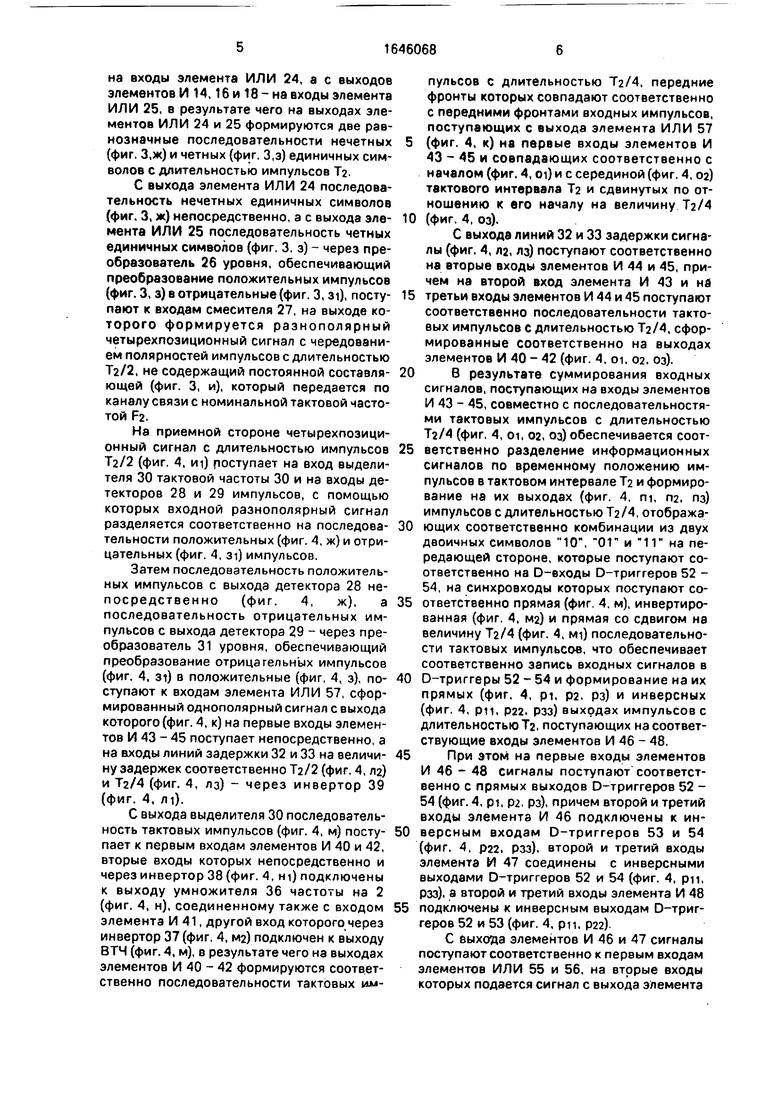

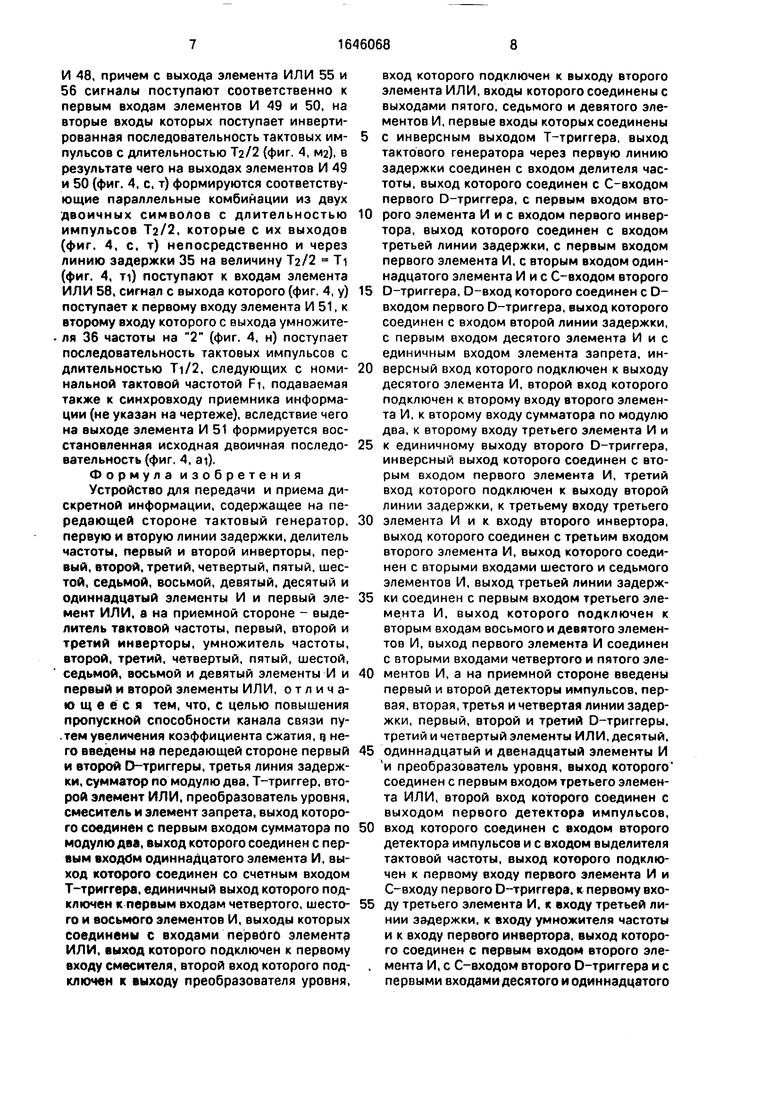

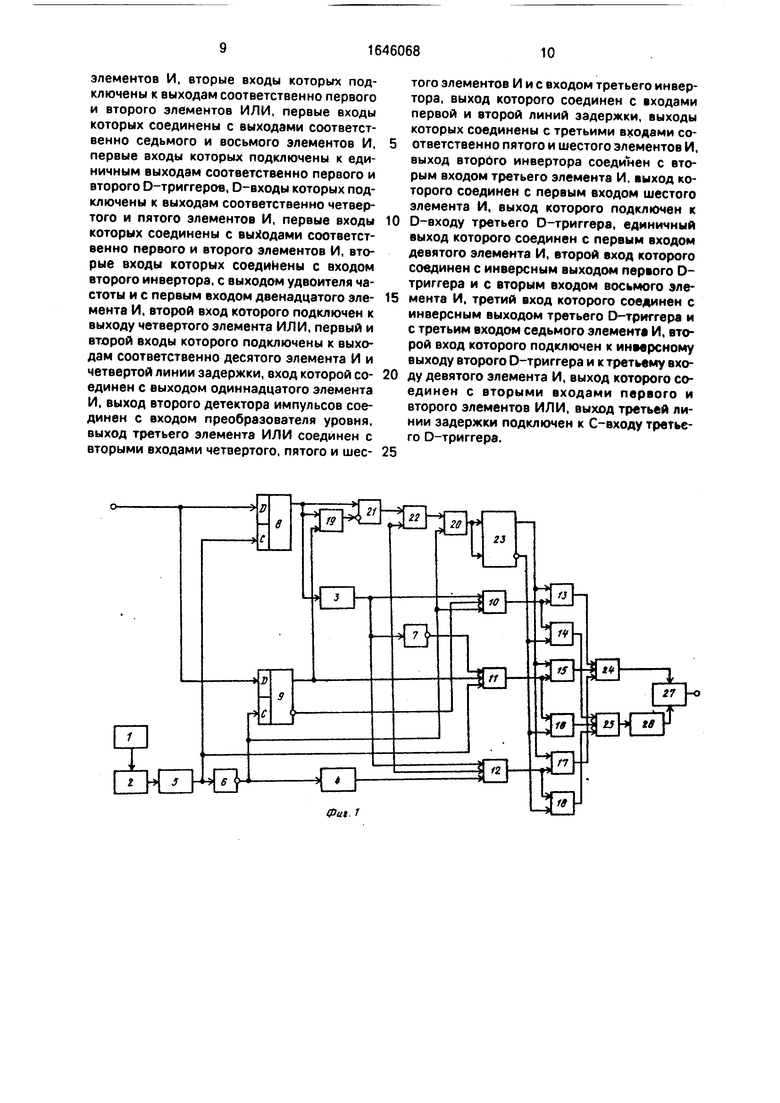

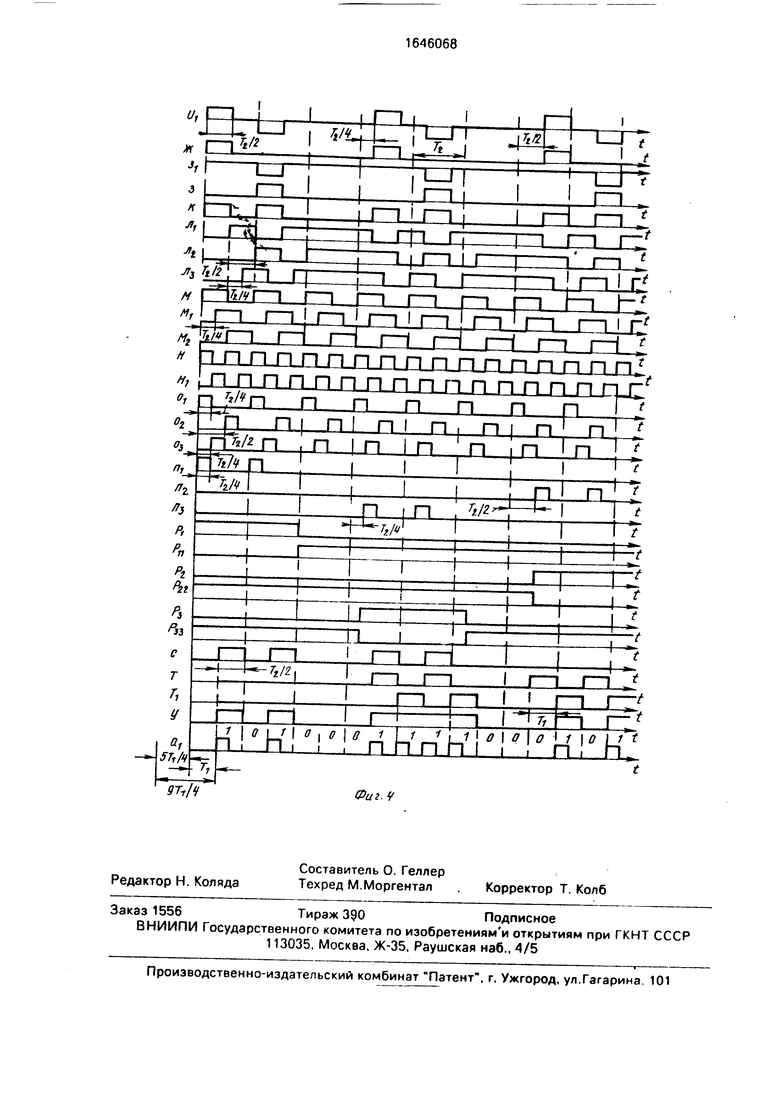

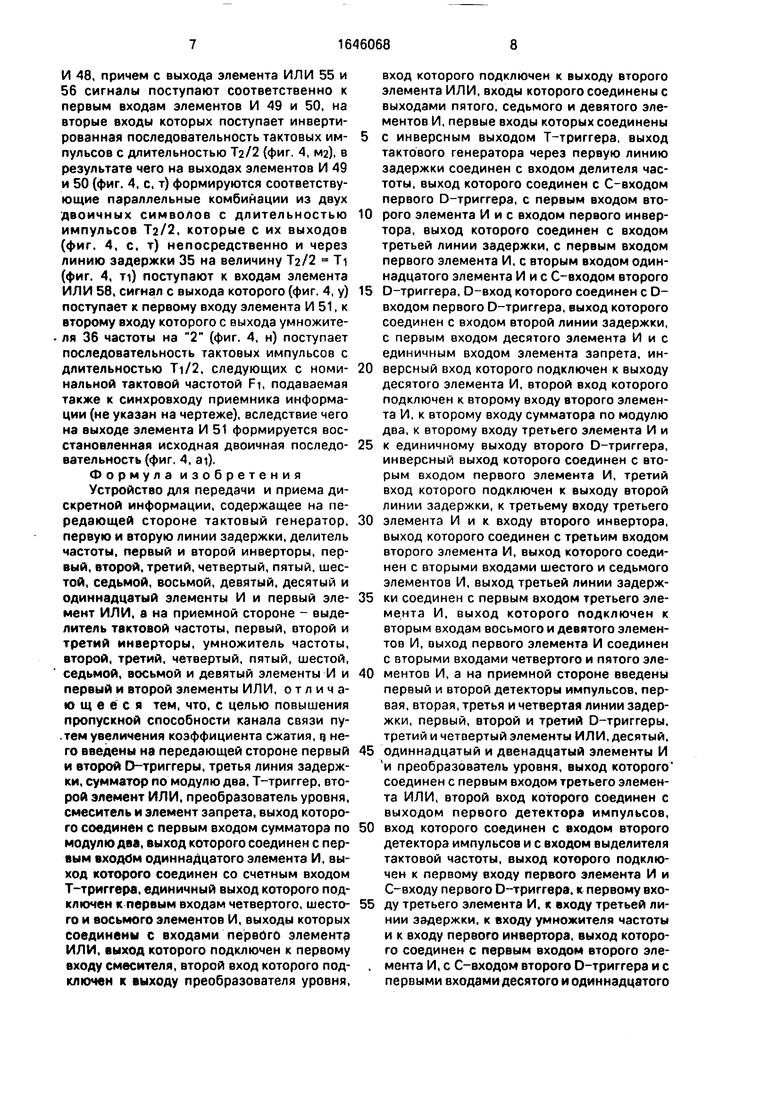

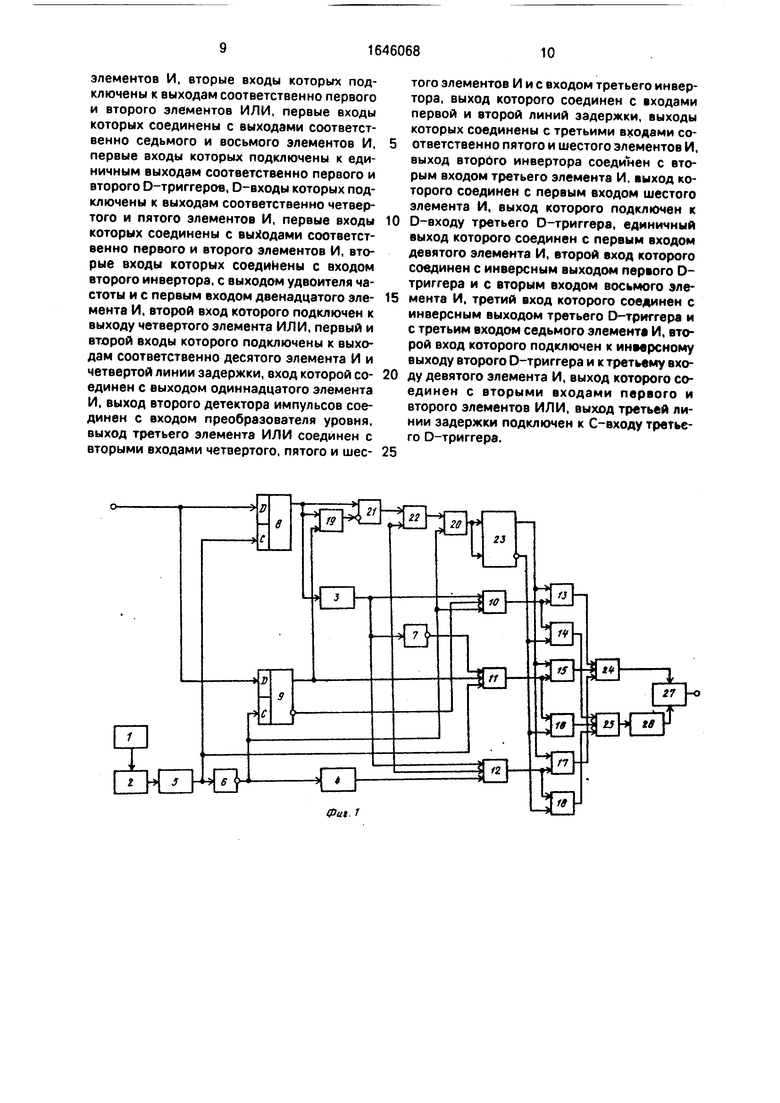

На фиг. 1 приведена структурная схема передающей стороны предложенного устройства; на фиг. 2 - приемной стороны предложенного устройства; на фиг. 3 и фиг. 4 - временные диаграммы работы устройства.

Устройство для передачи и приема дискретной информации содержит на передающей стороне тактовый генератор 1, первую, вторую и третью линии 2-4 задержки, делитель 5 частоты, первый и второй инверторы б и 7, первый и второй D-триггеры 8 и 9, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый элементы И 10,- 20, элемент запрета 21, сумматор 22 по модулю два, Т-триггер 23, первый и второй элементы ИЛИ 24 и 25, преобразователь 26 уровня и смеситель 27, а на приемной стороне - первый и второй детекторы 28 и 29 импульсов, выделитель 30 тактовой частоты, преобразователь 31 уровня, первую, вторую, третью и четвертую линии 32 - 35 задержки, умножитель 36 частоты, первый, второй и третий инверторы 37 - 39, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый элементы И 40 - 51, первый, второй и третий D-триггеры 52 - 54 и первый, второй, третий и четвертый элементы ИЛИ 55 - 58.

Устройство работает следующим образом.

О

4

В

О 00

На передающей стороне устройства исходная двоичная последовательность с длительностью импульсов Ti/2 в тактовом интервале Ti, следующих с номинальной тактовой частотой Fi 1/Ti, поступает от источника (не указанного на чертеже) информации, синхронизируемого с помощью тактового генератора 1, к D-входам D-триг- геров 8 и 9 и записывается в них соответственно с помощью прямой (фиг. 3, в) и инвертированной (фиг. 3, BI) последовательностей тактовых импульсов с длительностью Та/2 в тактовом интервале Та 2Ti, следующих с номинальной тактовой частотой Fa 1 /Та 1 /2Ti Fi/2, которые поступают с выхода делителя 5 частоты и инвертора 6, F3voa которого подключен к выходу делителя 5 частоты, причем вход делителя 5 частоты через линию 2 задержки на величину Тч/4 (фиг. 3, 6i) соединен с выходом тактового генератора 1 (фиг. 3, б), в результате чего каждая последовательная пара символов (10, 01, 11) преобразовывается на выходе D-триггеров 8 и 9 в соответствующую параллельную комбинацию из двух двоичных символов с длительностью импульсов Та (фиг. 3, г, д), а комбинации 00 передаются нулевыми символами с длительностью Та.

С прямых выходов D-триггеров 8 и 9 сигналы (фиг. 3, г, д) через элемент запрета 21 и непосредственно поступают на входы сумматора 22 по модулю два, а также поступают непосредственно на входы элемента И 19, выход которого соединен с запрещающим входом элемента запрета 21.

В моменты поступления комбинации 10 и 01 элемент И 19 не срабатывает и не закрывает элемент запрета 21, вследствие чего сигналы с прямых выходов D-триггеров 8 и 9 поступают на входы сумматора 22, с выхода которого сформированный сигнал поступает на первый вход элемента И 20, на второй вход которого подается инвертированная последовательность тактовых импульсов (фиг. 3, BI), что обеспечивает срабатывание элемента И 20 при каждом появлении единичного сигнала на выходе сумматора 22. При этом с выхода элемента И 20 сигнал поступает на входы Т-триггера 23 со счетным входом и вызывает переключение последнего из одного устойчивого состояния в другое.

При появлении комбинации 11 элемент И 19 срабатывает и единичным потенциалом со своего выхода закрывает элемент запрета 21, что обеспечивает срабатывание сумматора 22 и в данном случае, так как на его входы при этом поступают соответственно двоичные символы О и 1, в результате чего на выходе Т-триггера 23 обеспечивается формирование прямого (фиг. 3, е) и инвертированного (фиг. 3, ei) управляющих сигналов, необходимых для управления изменением полярности каждого последующего импульса суммарного четы- рехпозиционного сигнала на обратную по отношению к полярности предыдущего, что осуществляется следующим образом.

0 При поступлении комбинаций 10 на входы элемента И 10 поступают соответственно информационные сигналы с прямого выхода D-триггера 8 (фиг. 3, г) через линию задержки 3 на величину Та/2 Ti (фиг. 3, п), а

5 с инверсного выхода D-триггера 9 (фиг. 3, Д1) непосредственно, и инвертированная последовательность тактовых импульсов (фиг. 3, вч), в результате чего на выходе элемента И 10 формируются импульсы с

0 длительностью Та/2 в первой половине тактового интервала Та.

В моменты появления комбинаций 01 на входы элемента И 11 поступают соответственно информационные сигналы с прямо5 го выхода D-триггера 8 (фиг. 3, г) через последовательно соединенные линию 3 задержки (фиг. 2, п) и инвертор 7 (фиг. 3, га), а с прямого выхода D-триггера 9 - непосредственно, и последовательность тактовых

0 импульсов с выхода делителя 5 частоты (фиг. 3, в), в результате чего на выходе элемента И 11 формируются импульсы с длительностью Та/2 во второй половине тактового интервала Та.

5 При появлении комбинаций 11 на входы элемента И 12 поступают соответственно информационные сигналы с прямых выходов D-триггеров 8 и 9 через линию 3 задержки (фиг. 3, п) и непосредственно

0 (фиг. 3, д) и инвертированная последовательность тактовых импульсов (фиг. 3, BI), задержанная с помощью линии 4 задержки на величину Та/4 (фиг. 3, ва), в результате чего на выходе элемента И 12 формируются

5 импульсы с длительностью Та/2, передние фронты которых сдвинуты на величину Та/4 по отношению к началу тактового интервала Та, причем комбинации 00 передаются нулевыми символами с длительностью Та.

0 Импульсы с длительностью Та/2, сформированные с помощью элементов И 10 - 12, поступают соответственно с их выходов на первые входы элементов И 13 и 14, элементов И 15 и 16 и элементов И 17 и 18,

5 причем на вторые входы элементов И 134, 15 и 17 поступает управляющий сигнал с прямого выхода Т-триггера 23 (фиг. 3, е), а на вторые входы элементов И 14,16 и 18 - с инверсного (фиг, 3, ei), При этом сигналы с выходов элементов И 13,15 и17 поступают

на входы элемента ИЛИ 24, а с выходов элементов И 14,16 и 18-на входы элемента ИЛИ 25, в результате чего на выходах элементов ИЛИ 24 и 25 формируются две равнозначные последовательности нечетных (фиг. 3,ж) и четных (фиг. 3,з) единичных символов с длительностью импульсов Т2.

С выхода элемента ИЛИ 24 последовательность нечетных единичных символов (фиг, 3, ж) непосредственно, а с выхода элемента ИЛИ 25 последовательность четных единичных символов (фиг. 3. з) - через преобразователь 26 уровня, обеспечивающий преобразование положительных импульсов (фиг. 3, з) в отрицательные (фиг. 3, 3i), поступают к входам смесителя 27, на выходе которого формируется разнополярный четыре/позиционный сигнал с чередованием полярностей импульсов с длительностью Т2/2, не содержащий постоянной составляющей (фиг. 3, и), который передается по каналу связи с номинальной тактовой частотой F2.

На приемной стороне четырехпозици- онный сигнал с длительностью импульсов Тг/2 (фиг. 4, HI) поступает на вход выделителя 30 тактовой частоты 30 и на входы детекторов 28 и 29 импульсов, с помощью которых входной разнополярный сигнал разделяется соответственно на последовательности положительных (фиг. 4, ж) и отрицательных (фиг. 4, 3i) импульсов.

Затем последовательность положительных импульсов с выхода детектора 28 непосредственно (фиг. 4, ж), а последовательность отрицательных импульсов с выхода детектора 29 - через преобразователь 31 уровня, обеспечивающий преобразование отрицательных импульсов (фиг. 4, зт) в положительные (фиг. 4, з), поступают к входам элемента ИЛИ 57, сформированный однополярный сигнал с выхода которого (фиг. 4, к) на первые входы элементов И 43 - 45 поступает непосредственно, а на входы линий задержки 32 и 33 на величину задержек соответственно Т2/2 (фиг. 4, Л2) и Т2/4 (фиг. 4, лз) - через инвертор 39 (фиг. 4, Л1).

С выхода выделителя 30 последовательность тактовых импульсов (фиг, 4, м) поступает к первым входам элементов И 40 и 42, вторые входы которых непосредственно и через инвертор 38 (фиг. 4, HI) подключены к выходу умножителя 36 частоты на 2 (фиг. 4, н), соединенному также с входом элемента И 41, другой вход которого через инвертор 37 (фиг. 4, М2) подключен к выходу ВТЧ (фиг. 4, м), в результате чего на выходах элементов И 40 - 42 формируются соответственно последовательности тактовых импульсов с длительностью Т2/4, передние фронты которых совпадают соответственно с передними фронтами входных импульсов, поступающих с выхода элемента ИЛИ 57

(фиг. 4, к) на первые входы элементов И 43 - 45 и совпадающих соответственно с началом (фиг. 4, oi) и с серединой (фиг. 4, 02) тактового интервала Т2 и сдвинутых по отношению к его началу на величину Та/4

0 (фиг. 4, оз).

С выхода линий 32 и 33 задержки сигналы (фиг, 4, Л2, лз) поступают соответственно на вторые входы элементов И 44 и 45, причем на второй вход элемента И 43 и нд

5 третьи входы элементов И 44 и 45 поступают соответственно последовательности тактовых импульсов с длительностью Т2/4, сформированные соответственно на выходах элементов И 40 - 42 (фиг. 4, oi, 02. 03).

0 В результате суммирования входных сигналов, поступающих на входы элементов И 43 - 45, совместно с последовательностями тактовых импульсов с длительностью Т2/4 (фиг. 4, oi, O2, оз) обеспечивается соот5 ветственно разделение информационных сигналов по временному положению импульсов в тактовом интервале Т2 и формирование на их выходах (фиг. 4, щ, П2. пз) импульсов с длительностью Т2/4, отобража0 ющих соответственно комбинации из двух двоичных символов 10, 01 и 11 на передающей стороне, которые поступают соответственно на D-еходы D-триггеров 52 - 54, на синхровходы которых поступают со5 ответственно прямая (фиг. 4. м), инвертированная (фиг, 4, М2) и прямая со сдвигом на величину Т2/4 (фиг. 4, MI) последовательности тактовых импульсов, что обеспечивает соответственно запись входных сигналов в

0 D-триггеры 52 - 54 и формирование на их прямых (фиг. 4, pi. P2, рз) и инверсных (фиг, 4, р11, Р22. рзз) выходах импульсов с длительностью Т2, поступающих на соответствующие входы элементов И 46 - 48,

5 При этом на первые входы элементов И 46 - 48 сигналы поступают соответственно с прямых выходов D-триггеров 52 - 54 (фиг. 4, pi, рг, рз), причем второй и третий входы элемента И 46 подключены к ин0 версным входам D-триггеров 53 и 54 (фиг. 4. р22. рзз). второй и третий входы элемента И 47 соединены с инверсными выходами D-триггеров 52 и 54 (фиг. 4, рп, рзз), а второй и третий входы элемента И 48

5 подключены к инверсным выходам D-триггеров 52 и 53 (фиг. 4, рп, Р22)

С выхода элементов И 46 и 47 сигналы поступают соответственно к первым входам элементов ИЛИ 55 и 56, на вторые входы которых подается сигнал с выхода элемента

И 48, причем с выхода элемента ИЛИ 55 и 56 сигналы поступают соответственно к первым входам элементов И 49 и 50, на вторые входы которых поступает инвертированная последовательность тактовых импульсов с длительностью Та/2 (фиг. 4, М2), в результате чего на выходах элементов И 49 и 50 (фиг. 4, с, т) формируются соответствующие параллельные комбинации из двух двоичных символов с длительностью импульсов Т2/2. которые с их выходов (фиг. 4, с, т) непосредственно и через линию задержки 35 на величину Т2/2 Ti (фиг. 4, TI) поступают к входам элемента ИЛИ 58, сигнал с выхода которого (фиг. 4, у) поступает к первому входу элемента И 51, к второму входу которого с выхода умножителя 36 частоты на 2 (фиг. 4, н) поступает последовательность тактовых импульсов с длительностью Ti/2, следующих с номинальной тактовой частотой FI, подаваемая также к синхровходу приемника информации (не указан на чертеже), вследствие чего на выходе элемента И 51 формируется восстановленная исходная двоичная последовательность (фиг. 4, ai).

Формула изобретения Устройство для передачи и приема дискретной информации, содержащее на передающей стороне тактовый генератор, первую и вторую линии задержки, делитель частоты, первый и второй инверторы, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый и одиннадцатый элементы И и первый элемент ИЛИ, а на приемной стороне - выделитель тактовой частоты, первый, второй и третий инверторы, умножитель частоты, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И и первый и второй элементы ИЛИ, отличающееся тем, что, с целью повышения пропускной способности канала связи пу- .тем увеличения коэффициента сжатия, ч него введены на передающей стороне первый и второй D-триггеры, третья линия задержки, сумматор по модулю два, Т-триггер, второй элемент ИЛИ, преобразователь уровня, смеситель и элемент запрета, выход которого соединен с первым входом сумматора по модулю два, выход которого соединен с первым входом одиннадцатого элемента И, выход которого соединен со счетным входом Т-триггера, единичный выход которого подключен к первым входам четвертого, шестого и восьмого элементов И, выходы которых соединены с входами первого элемента ИЛИ, выход которого подключен к первому входу смесителя, второй вход которого подключен к выходу преобразователя уровня,

вход которого подключен к выходу второго элемента ИЛИ, входы которого соединены с выходами пятого, седьмого и девятого элементов И, первые входы которых соединены

с инверсным выходом Т-триггера, выход тактового генератора через первую линию задержки соединен с входом делителя частоты, выход которого соединен с С-входом первого D-триггера, с первым входом вто0 рого элемента И и с входом первого инвертора, выход которого соединен с входом третьей линии задержки, с первым входом первого элемента И. с вторым входом одиннадцатого элемента И и с С-входом второго

5 D-триггера, D-вход которого соединен с D- входом первого D-триггера, выход которого соединен с входом второй линии задержки, с первым входом десятого элемента И и с единичным входом элемента запрета, ин0 версный вход которого подключен к выходу десятого элемента И, второй вход которого подключен к второму входу второго элемента И, к второму входу сумматора по модулю два, к второму входу третьего элемента И и

5 к единичному выходу второго D-триггера, инверсный выход которого соединен с вторым входом первого элемента И, третий вход которого подключен к выходу второй линии задержки, к третьему входу третьего

0 элемента И и к входу второго инвертора, выход которого соединен с третьим входом второго элемента И, выход которого соединен с вторыми входами шестого и седьмого элементов И, выход третьей линии задерж5 ки соединен с первым входом третьего элемента И, выход которого подключен к вторым входам восьмого и девятого элементов И, выход первого элемента И соединен с вторыми входами четвертого и пятого эле0 ментов И, а на приемной стороне введены первый и второй детекторы импульсов, первая, вторая, третья и четвертая линии задержки, первый, второй и третий D-триггеры, третий и четвертый элементы ИЛИ, десятый,

5 одиннадцатый и двенадцатый элементы И и преобразователь уровня, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого детектора импульсов,

0 вход которого соединен с входом второго детектора импульсов и с входом выделителя тактовой частоты, выход которого подключен к первому входу первого элемента И и С-входу первого D-триггера. к первому вхо5 ду третьего элемента И. к входу третьей линии задержки, к входу умножителя частоты и к входу первого инвертора, выход которого соединен с первым входом второго эле- . мента И, с С-входом второго D-триггера и с первыми входами десятого и одиннадцатого

элементов И, вторые входы которых подключены к выходам соответственно первого и второго элементов ИЛИ, первые входы которых соединены с выходами соответственно седьмого и восьмого элементов И, первые входы которых подключены к единичным выходам соответственно первого и второго D-триггерои, D-входы которых подключены к выходам соответственно четвертого и пятого элементов И, первые входы которых соединены с выходами соответственно первого и второго элементов И, вторые входы которых соедийены с входом второго инвертора, с выходом удвоителя частоты и с первым входом двенадцатого эле- мента И, второй вход которого подключен к выходу четвертого элемента ИЛИ, первый и второй входы которого подключены к выходам соответственно десятого элемента И и четвертой линии задержки, вход которой со- единен с выходом одиннадцатого элемента И, выход второго детектора импульсов соединен с входом преобразователя уровня, выход третьего элемента ИЛИ соединен с вторыми входами четвертого, пятого и шее-

того элементов И и с входом третьего инвертора, выход которого соединен с входами первой и второй линий задержки, выходы которых соединены с третьими входами соответственно пятого и шестого элементов И, выход второго инвертора соединен с вторым входом третьего элемента И, выход которого соединен с первым входом шестого элемента И, выход которого подключен к D-входу третьего D-триггера, единичный выход которого соединен с первым входом девятого элемента И, второй вход которого соединен с инверсным выходом первого D- триггера и с вторым входом восьмого элемента И, третий вход которого соединен с инверсным выходом третьего D-триггера и с третьим входом седьмого элемент И, второй вход которого подключен к инверсному выходу второго D-триггера и к третьему входу девятого элемента И, выход которого соединен с вторыми входами первого и второго элементов ИЛИ, выход третьей линии задержки подключен к С-входу третьего D-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в четырех-позиционный временной код | 1990 |

|

SU1757104A1 |

| Устройство для регистрации действий спортсмена на дистанции | 1990 |

|

SU1784247A1 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1990 |

|

SU1723658A2 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

| Устройство для передачи фазоманипулированного сигнала | 1985 |

|

SU1288928A1 |

| Цифровой приемник дельта-модулированных сигналов | 1989 |

|

SU1732499A1 |

| Устройство для приема и передачи данных в дуплексном режиме | 1987 |

|

SU1506576A1 |

| Селектор импульсной последовательности | 1990 |

|

SU1748238A1 |

| УСТРОЙСТВО ДЛЯ УСПОКОЕНИЯ КОЛЕБАНИЙ УПРУГОГО ЭЛЕМЕНТА ПЕРЕМЕННОЙ ЖЕСТКОСТИ | 2003 |

|

RU2249243C2 |

| Многоканальный коммутатор | 1988 |

|

SU1541764A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение пропускной способности канала связи путем увеличения коэффициента сжатия. Устр-во содержит на передающей стороне тактовый генератор, делитель частоты, три линии задержки, два D-триггера, одиннадцать элементов И, два элемента ИЛИ, преобразователь уровня и смеситель, а на приемной стороне выделитель тактовой частоты, четыре линии задержки, умножитель частоты, три инвертора, двенадцать элементов И, четыре элемента ИЛИ и три D-триггера. Повышение пропускной способности достигается в реультате преобразования двоичного сигнала в многопозиционный сигнал с двукратным увеличением длительности формируемых импульсов. На приемной стороне многопозиционный сигнал преобразуется в двоичный и восстанавливается исходная двоичная последовательность. 4 ил. Ё

Фиг 1

Фш.1

tr

Till

WU

+Г

l

en

-M.

- 1 jl

i,

I-I -1

J

-f-L

n П

ГП1 Г

Г ГП Гг

H Kf

i-LI r

АГ5УГП ГП Г1, M .M. J- ГП /

пппппппп n..n.nj ixijn n n n.r.

/ LrLTLTLrLn П П rLTLTL PL rTJnjn nnJ7

TZJT

- .1

„I 51

a

rT rn /

т rp r

4-L

-M.

n П

ГП1 Г

Г ГП Гг

H Kf

i-LI r

| Патент США № 3679977, кл | |||

| Водяной двигатель | 1921 |

|

SU325A1 |

Авторы

Даты

1991-04-30—Публикация

1988-12-22—Подача