Изобретение относится к радиотехнике и вычислительной технике и может использоваться в системах передачи дискретной информации различного назначения,

Известно устройство для преобразования двоичного кода в троичный, содержащее элементы И, элементы НЕ и элементы ИЛИ, которое обеспечивает преобразование комбинаций из 3 двоичных символба (1;0) в комбинации из 2 троичных символов (+1;0;-1) по заданному алгоритму (3В ), в результате чего достигается сокращение полосы частот передаваемого сигнала в 1,5 раза.

Недостатком устройства является то, что оно обеспечивает небольшой коэффициент сжатия полосы частот передаваемого сигнала (К 1,5). Кроме того, троичный сигнал, сформированный в соответствии с заданным алгоритмом преобразования, является несбалансированным, что снижает его помехоустойчивость,

Наиболее близким к заявляемому является преобразователь двоичного кода в четырехпозиционный временной код, содержащий генератор импульсов, пераый- четвертый элементы задержки, делитель частоты, последовательный и параллельный регистры, первый-девятый элементы И, пер- вый-третий элементы ИЛИ, элемент НЕ, триггер со счетным входом, преобразователь уровня и сумматор, который обеспечивает двукратное сжатие полосы частот передаваемого сигнала путем преобразования двоичных сигналов в четырехпозицион- ные.

Существенным недостатком известного преобразователя является то, что в спектре четырехпозиционного сигнала содержится сравнительно высокий уровень компонентов второй гармоники тактовой частоты, возникающих в результате преобразования каждой комбинации на 2 двоичных символа 11 с длительностью импульсов Ti/2 в положительный или отрицательный импульс с длительностью Т2/2, сдвинутый по отношению к началу тактового интервала Т2 на величину Т2/4, вследствие чего возникает флуктуация частоты следования импульсов четырехпозиционного сигнала, изменяющаяся s соответствии с изменением структуры входной двоичной последовательности, что приводит, в свою очередь, к флуктуации полосы частот передаваемого сигнала.

Цель изобретения - повышение достоверности преобразователя путем устранения флуктуации частоты следования импульсов передаваемого сигнала в результате изменения алгоритма кодирования.

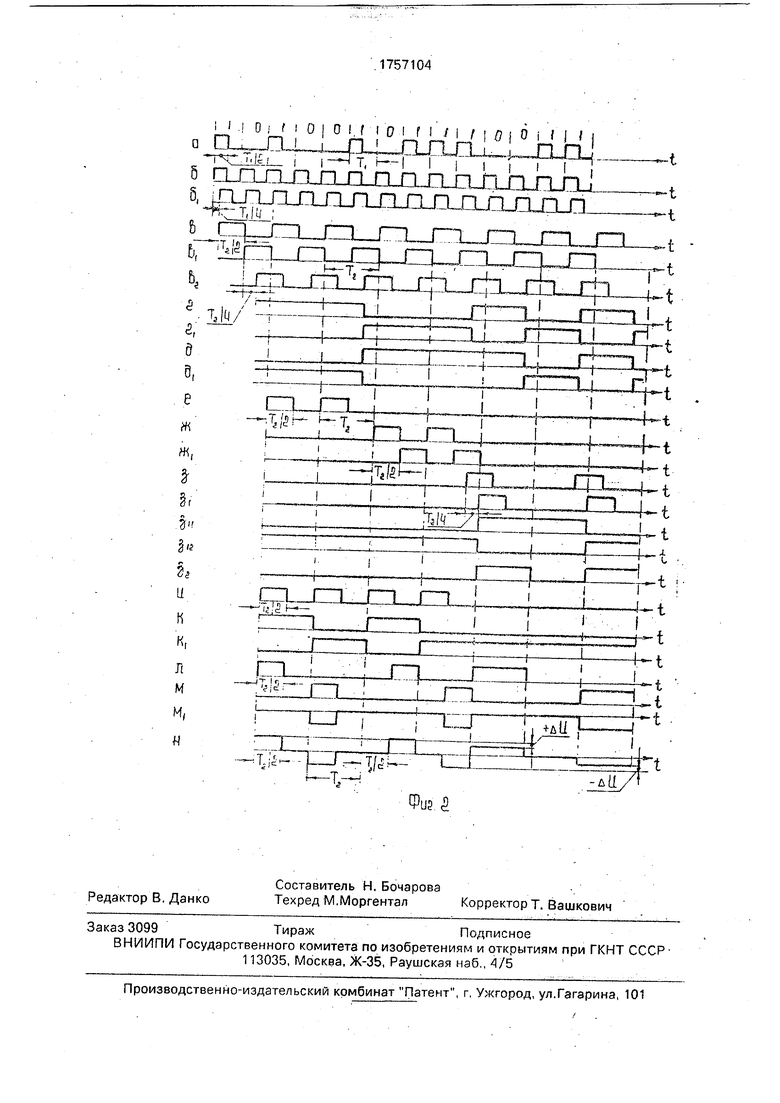

На фиг. 1 и 2 приведены структурная схема и временные диаграммы работы преобразователя.

Преобразователь содержит (фиг 1) генератор 1 импульсов, первый элемент 2 задержки, делитель 3 частоты, последовательный регистр 4, элемент НЕ 5, второй элемент б задержки, параллельный регистр 7, первый, третий и второй элементы И 8-10, первый

0 элемент ИЛИ 11, четвертый и третий элементы 12 и 13 задержки, триггеры 14 и 15 со счетным входом, 6-триггер 16, четвертый- девятый элементы И 17-22, второй и третий элементы ИЛИ 23, 24, преобразователь 25

5 уровня и сумматор 26,

Преобразователь двоичного кода в четырехпозиционный временной код работает следующим образом.

Исходная двоичная последователь0 ность с длительностью импульсов Ti/2 в тактовом интервале П, следующих с номинальной тактовой частотой FI 1/Ti, посту- паетот источника дискретной информации (фиг.2а), синхронизируемого с помощью

5 генератора 1 импульсов, на информационный вход последовательного регистра 4 и записывается в ячейки регистра с помощью последовательности тактовых импульсов, поступающих с выхода генера0 тора 1 (фиг.2б) через элемент 2 задержки на величину Ti/4 (фиг.26).

С одноименных выходов последовательного регистра 4 двоичные символы поступают соответственно к одноименным

5 входам параллельного регистра 7 и записываются в него с помощью последовательности тактовых импульсов с длительностью Та/2 в тактовом интервале 1г 2Ti, следующих с номинальной тактовой частотой

0 F2 1/Т2 1/2Ti Fi/2, формируемых с помощью делителя 3 частоты 1:2, вход которого соединен с выходом элемента 2 задержки (фиг.2б1), которые с его выхода (фиг.2в) через последовательно соединен5 ные элемент НЕ 5 (фиг.2в1) и элемент 6 задержки на величину Т2/4 (фиг.2в2) поступают на тактовый вход параллельного регистра 7, в результате чего исходная двоичная последовательность разделяется на группы

0 на 2 двоичных символов, каждая из которых преобразовывается далее в соответствующую параллельную комбинацию из 2 двоичных символов с длительностью Т2 (фиг.2г,д).

5 С первого и второго прямых выходов параллельного регистра (фиг.2г,д) сигналы поступают к первому и второму входам элемента И 10 и соответственно к первым входям элементов И 8 v 9, вторые входы , которых подключены соответственно к второму (фиг,2д1) и первому (фиг 2п) инверсным выходим параллельного реги-стра, причем третьи входы элементов И 8 и 9 подключены к выходу делителя 3 частоты (фиг.2в), а третий вход элемента И 10 соединен с выходам элемента 6 задержки (фиг.2в2), в результате ч его при поступлении входной комбинации (фиг2г,д) вида 10 срабатывает элемент И 8, при комбинации 01 - элемент И 9, а при комбинации 11 - элемент И 10. При этом на выходе элементов И 8-10 формируются соответственно импульсы с длительностью Та/2 (фиг.2е,ж,з), причем при поступлении комбинаций 00 формируются нулевые символы с длительностью Т2.

Сигналы, сформированные на выходе элементов И 8 и 9 (фиг.2е,ж), поступают через элемент ИЛИ 11 (фиг,2и) на счетный вход триггера 14 и управляют его переключением, на выходе которого формируются сигналы (фиг.2к,К1), управляющие изменением полярности импульсов с длительностью Та/2, сформированных на выходе элементов И 17-20, которые в зависимости от состояния триггера 14 поступают на входы элементов ИЛИ 23 или 24.

Сигнал, сформированный на выходе элемента И 10(фиг.2з), поступает на D-вход D-триггера 16, синхровход которого соединен с выходом делителя 3 частоты (фиг.2в), на выходе которого формируются импульсы с длительностью Та (фиг.2за). С выхода элемента И 10 сигнал поступает через элемент 13 задержки на величину Та/4 (фиг,2з1) на счетный вход триггера 15 и управляет его переключением, на выходе которого формируются сигналы (фиг,2зц,31а), управляющие изменением полярности импульсов с длительностью Та, сформированных на выходе элементов И 21 и 22, которые в зависимости от состояния триггера 15 поступают аналогично к входам элементов ИЛИ 23 или 24,

С выхода элемента И 8 (фиг.2е) сигналы к первым входам элементов И 17 и 18 поступают непосредственно, а с выхода элемента И 9 (фиг.2ж) к первым входам элементов И 19 и 20 - через элемент 12 задержки на величину Та/2 (фиг.2ж1). Вторые входы элементов И 17 и 19 подключены соответственно к единичному выходу триггера 14 (фиг.2к), а вторые входы элементов И 18 и 20 - к инверсному (фиг.2м), в результате чего на выходе элементов И 17 и 18 формируются импульсы с длительностью Та/2 в первой половине тактового интервала Та, а на выходе элементов И 19 и 20 - во второй.

Импульсы с длительностью Та, сформированные на выходе D-триггера 16 С иг.2аа) поступают к первым входам И

21 и 22, вторые входы которых подключены соответственно к единичному (фиг.2зц) и инверсному (фиг,2з1а) выходам триггера 15, в результате чего на выходе элементое 5 И 21 и 22 формируются импульсы с длительностью Та.

Сигналы, сформированные на выходе элементов И 17, 19 и 21, поступают через элемент ИЛИ 23 (фиг,2л) к первому инфор0 мационному входу сумматора 26, а сигналы, сформированные на выходе элементов И 18, 20 и 22, поступают через элемент ИЛИ 2 (фиг.2м) к входу преобразователя 25 уровня, обеспечивающего преобразова5 ние положительных импульсов (фиг.2м) в отрицательные (фмг.2м1), которые с его выхода поступают к второму информационному входу сумматора, на выходе которого формируется разнополярный четырехпози0 ционный сигнал с длительностью импульсов Та/2 и Та строгим чередованием полярно1 стей импульсов по их длительности (фиг.2н), в спектре которого постоянная составляющая отсутствует, что обеспечивает его высп5 кую помехоустойчивость.

Для обеспечения одинаковой помехозащищенности импульсов, передаваемых с длительностью Та/2 и Та, введена корректировка выходных импульсов, в соответствии

0 с которой амплитуда положительных и отрицательных импульсов с длительностью Та уменьшается соответственно на величину ± A U (с учетом искажений, вносимых линией связи при заданной скорости пере5 дачи), что достигается в результате воздействия единичного сигнала, поступающего с выхода D-триггера 16 (фиг.2за), к управляющему входу сумматора 26.

Практическая реализация преобразовэ0 теля выполнена, в основном, на элементах логики (И, ИЛИ, НЕ), генераторе импульсов, делителе частоты 1:2, последовательном и паралпельном регистрах, триггерах со счетным входом, D-триггере и сумматоре,

5 Элемент (2, 6, 12, 13) задержки может быть реализован на-одновибраторе с регулируемой времязадающей цепочкой RC с переменным резистором R, включенной в цепи его запуска.

0 Преобразователь 25 уровня может быть реализован на операционном усилите с с обратной связью с использованием инвертирующего входа.

Учитывая, что в процессе преобразова5 ния двоичных символов в разнополярный четырехпозиционный сигнал с длительностью импульсов Т2/2 и Та со строгим чередованием полярностей импульсов по их длительности минимальные временные интервалы между следующими друг за другом

импульсами в структуре передаваемого сигнала соответствуют значениям Т2/2, то, следовательно, компоненты второй гармоники тактовой частоты в спектре четыр хпозици- онного сигнала отсутствуют, так как частота следования импульсов передаваемого сигнала сохраняется при этом номинальной и не зависит от изменения структуры сходной двоичной последовательности, что и соответствует повышению достоверности преобразования.

Формула изобретения Преобразователь двоичного кода в че- тырехпозиционный временной код, содержащий последовательный регистр, информационный вход которого является входом преобразователя, выходы соединены с одноименными информационными входами параллельного регистра, первые прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго элементов И и третьего элемента И, вторые входьГи инверсный выходы параллельного регистра соединены с вторыми входами соответственно второго и третьего элементов И и первого элемента И, выход которого соединен с первыми входами четвертого и пятого элементов Л и первого элемента ИЛИ, выход которого соединен со счетным входом первого Т- триггера, прямой выход первого Т-триггерз соединен с первым входом шестого элемента И и вторым входом четвертого элемента И, инверсный выход первого Т--триггера соединен с первым входом седьмого элемента И и вторым входом пятого элемента И, восьмой элемент И, выход которого и выходы четвертого и шестого элементов И соединены с соответствующими входами второго

элемента ИЛИ, выход которого соединен с первым информационным входом сумматора, девятый элемент И, выход которого и выходы пятого и седьмого элементов И соединены с соответствующими входами третьего элемента ИЛИ, выход которого через преобразователь уровня соединен с вторым информационным входом сумматора, выход которого является выходом преобразователя, генератор импульсов, выход которого через первый элемент задержки соединен с тактовым входом последовательного регистра и входом делителя частоты, выход которого соединен через последовательно

соединенные первый элемент НЕ и второй элемент задержки с тактовым входом параллельного регистра и третьим входом второго элемента И, выход которого соединен с входом третьего элемента задержки, выход

третьего элемента И соединен непосредственно с вторым входом первого элемента ИЛИ и через четвертый элемент задержки с вторыми входами шестого и седьмого элементов И, отличающийся тем, что, с

целью повышения достоверности преобразователя, в него введены второй Т-триггер и D-триггер, информационный вход которого подключен к выходу второго элемента И, синхровход D-триггера объединен с третьими входами первого и третьего элементов И и подключен к выходу делителя частоты, выход D-триггера соединен с управляющим входом сумматора и первыми входами восьмого м девятого элементов И, выход третьего элемента задержки соединен со счетным входом второго Т-триггера, прямой и инверсный выходы которого соединены с вторыми входами соответственно восьмого и девятого элементов И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в четырехпозиционный код | 1988 |

|

SU1594703A1 |

| Преобразователь двоичного кода в восьмипозиционный временной код | 1990 |

|

SU1730725A1 |

| Преобразователь четырехпозиционного временного кода в двоичный код | 1990 |

|

SU1797162A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1646068A1 |

| Преобразователь двоичного кода в унитарный код | 1982 |

|

SU1049897A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь кода | 1980 |

|

SU1168922A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

Изобретение относится к радиотехнике и вычислительной технике и может использоваться в системах передачи дискретной информации различного назначения, Устройство обеспечивает двукратное сокраще 7 ние полосы частот передаваемого сигнала путем преобразования двоичных сигналов в рэзнополярный четырехпозиционный сиг; нал с различной длительностью импульсов со строгим чередованием полярностей импульсов по их длительности путем увеличения длительности формируемых импульсов и уменьшения частоты их следования, что повышает достоверность преобразователя. Преобразование двоичного кода в четырехпозиционный временной код обеспечивается с помощью генератора 1 импульсов, делителя 3 частоты, элементов И 8-10,17-22, ИЛИ f 1,23,24, НЕ 5, элементов задержки 6, 12, 13, последовательного 4 и параллельного регистров Т-триггеров 14,15 со счетным входом, преобразователя 25 уровня, D-триг- гера 16 и сумматора 26. 2 ил. М Фиа

| УСТРОЙСТВО ДЛЯ СТАБИЛИЗАЦИИ ВИНОГРАДНЫХ СОКОВ И ВИН | 1997 |

|

RU2124049C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Преобразователь двоичного кода в четырехпозиционный код | 1988 |

|

SU1594703A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1992-08-23—Публикация

1990-12-17—Подача