Я

СП

о

Од СП

о

Изнбретеине относится к технике связи и исг111ЛЬ човаться при построении приемопередатчиков сигналов nnipoTHo-ifMnyjibCHoi i манигтуляции. Целью итобретонпя является повышение достоперности приема при обмене цифрово информацией по последовательным каналам л луплексном режиме.

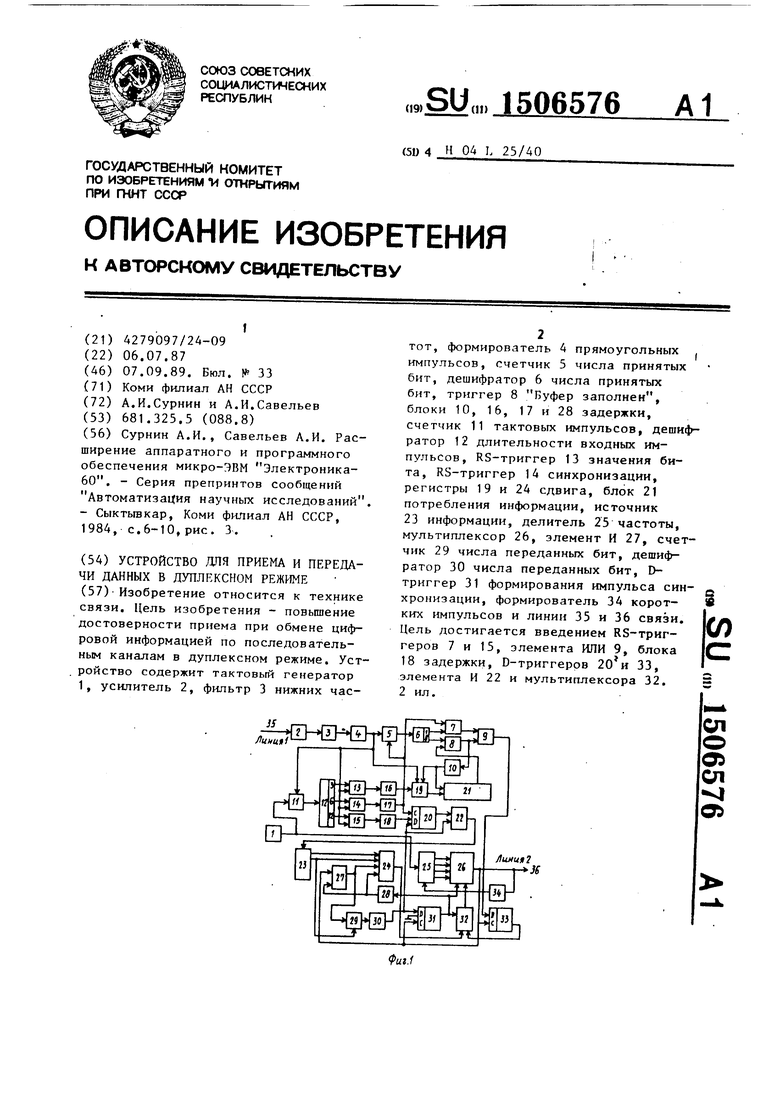

На фиг. 1 приведена структурная электрическая устройства; на фиг. 2 - лрс ме ные диагра -гмы, поясняющие его работу.

Устройство содержит чактов) генератор 1, усилитель 2, фштьтр 3 нижних частот, формирователь А прямоугольных импульсов, счетчик 5 числа принятых бит, д л гифратор 6 числа принятых бит, первьп RS-триггер 7, триггер 8 Буфер заполнен, элемент ИЛИ 9, четвертьп 6jTOK 10 задержки, счетчик 11 т. штоных импульсов, дешифратор длительное и входных импульсов, RS-ipnrrep 13 значения бита, RS-тригг ер 14 c:vnfxpoHn3aiuiH, второй RS-триггер 15, первьи 16, второй 17 и пятый 18 блс кп задержки, первый регистр 19 сдвига, второй D-rpiirrep 20, блок 21 потребителя информации, второй элемент Я 22, источник 23 информадии, второй регистр 24 сдвига делитель 25 частоты, перьы мультиплексор 26, первый 5ле ;-1ент И 27, третий блок 28 задержки, счетчик 29 числа переданных бит, дешифратор 30 числа переданных бит, Т)-триггер 31 формирования импульса синхронизацтш, второй мультиплекссзр 32, перв1 1Й D- триггер 33, формирователь 34 коротких импульсов, первая 35 и вторая 36 линии связи.

Устройство для приема и передачи данных в дуплексном режиме работает следукидим образом.

Делитель 23 частоты делит частоту тактового генератора 1 и формирует четыре последовательности им- пудьсов разной дшпельностп, поступающие на мультиплексор 26. Выбор серии импульсов и их длительность на выходе мультиплексора 26 зависит от значения cirrnaj.OB на его управляющих входах, Фо1)ма импульсов на выходе мультиплексора 26 приведена пр н;гличии передаваемой информапии на фиг. 2(а), а при отсутствии - на фиг, 2(6). С, помощью формирователя 34 коротких импульсов по за71нему

5

0

5

0

5

0

5

фронту каждого импульса npoиcxoдиt сброс счетчиков делите.гтя 25 частоты для получения импул1,сов со скважностью 1/2, Данные от источника 23 информадии записываются в параллель- 1ГОМ коде в регистр 24. (троГ сопровождения данных устанавливает в нуль счетчик 29. Очередным перепадом (задним )импульса с выхода мультиплексора 26 триггер 31 устанавливается в состояние, разрешающее, через элемент И 27, выполнение сдвига в регистре 24 и счет числа переданных бит счетчиком 29, Кроме того, на управляющих входах мультиг1лект:о- ров 26 и 32 устанавливается значение сигнала, обеспечивающее формирование импульсов длительностью Т1 и Т2, Далее происходит сдвиг по каждому заднему фронту 11мпульсов с выхода мультиплексора 26 данных в регистре 24, В зависимости от значения очередного бита формируется импульс длительностью Т1 или Т2, По окончании передачи происходит изменение значения cniMirTJia на выходе дешифратора 30 (код, занесенный в счетчик 29, соответствует числу передаваемых бит в каждом поле данных) и установка триг- гера 31 в состояние, обеспечивающее

пс1)(дачу импульсов синхронизации, длительностью ТЗ и Т4, прекращение сдвига информации в регистре 24 и счета числа импульсов счетчиком 29, Япительность импульсов синхронизации зависит от Состояния ГЬ-триггера 33. Информация в него записьшается. по каждому заднему фронту импульса с выхода мультиплексора 26 и зависит от готовности, к приему. Дпя продолже- 1П1Я передачи записывают новые данные из источника 23 информации в ре- г истр 24.

Входной аналоговый сигнал из линии 35 связи через (рходной) усилитель 2, фильтр 3 нижних частот и формирователь 4 прямоугольных импульсов поступает на блоки 5, 11 и 19. Импульс, поступающий на установочный вход счетчика 11, разрещает начать измерение его длительности путем подсчета импульсов с выхода тактового генератора 1. В зависимости от длительности входньрс импульсов, с помощью дешифратора 12 устанавливаются в 1 триггеры 13-15. Если длительность импульса Т4, то все триггеры установятся в 1, при ТЗ - триггеры 13 и

14, при Т2 - триггер 13. По заднему фронту входного импульса происходит сдвиг данных в регистре 19. Необходимая задержка обеспечивается блоком 16 задержки. Одновременно происходит счет числа принятых бит счетчиком 5. Если принят хотя бы один бит, то сигналом с выхода дешифратора 6 устанавливается в 1 триггер 7, что означает Приемник занят. После приема всего поля данных с известным фиксированным числом бит устанавливается в 1 триггер 8. С помощью элемента ИЛИ 9 формируется сигнал К приему не готов для триггера 33. Сигнал Буфер заполнен с выхода триггера 8 через блок 10 задержки поступает-на вход регистра 19, запрещая сдвиг в нем. Одновременно он поступает в блок 21 потребителя информации. После считывания данных из регистра 19 блок 21 устанавливает триггер 8 в О. При поступлении импульсов синхронизации длительностью ТЗ или Т4 происходит сброс триггера 7 в О, установка счетчика 5 принятых бит, занесение значения сигнала готовности к приему из триггера 15 в триггер 20. Последнее происходит лишь при отсутствии сигнала на установочном входе D-триггера 20 и соответствует завершению передачи данных. Необходимая задержка сигналов синхронизации обеспечивается блоками 17 и 18 задержки. С помощью- элемента И 22 формируется сигнал К передаче готов, поступающий на вход источника 23 информации для занесения в регистр 24 новых данных в па- раллельном коде. После окончания входного импульса (во время паузы) происходит сброс триггеров 13-15 и прекращение счета счетчиком 11. В результате источник 23 информации осуществляет занесение данных в регистр 24 для передачи при одновременном наличии сигнала завершения передачи с выхода дешифратора 30 и сигнала к приему готов с выхода триггер а 20.

Формула изобретения

Устройство для приема и передачи данных в дуплексном режиме, содержащее последовательно соединенные усилитель, фильтр нижних частот, формирователь прямоугольных угмпульсов.

0

0

счетчик числа принятых бит и дешифратор числа принятых бит, последовательно соединенные T.iKfoBbtfi генератор, счетчик тактовых импульсов и дешифратор длительности входных ffM- пульсов, последовательно соединенные RS-триггер значения бита, первый блок задержки и первый регистр сдвига, последовательно соединенные RS5

0

5

0

триггер синхронизации и второй блок задержки, последовательно соединенные источник информации и второй регистр сдвига, последовательно соединенные первый элемент И, счетчик числа переданных бит, дешифратор ч-ис- ла переданных бит, D-триггер формирования импульса синхронизации и третий блок задержки, пос.педователь- но соединенные делитель частоты, первый мультиплексор и формирователь коротких импульсов, а также триггер Буфер заполнен и четвертый блок задержки, выход которого соединен с вторым входом первого регистра сдвига и с входом готовности блока потребителя информации, выход формирователя прямоугольных импульсов подключен к установочному входу счетчика тактовых импульсов, к первым входам RS-триггеров значения бита и синхронизации и к тактовому входу первого регистра сдвига| вход усилителя соединен с первой линией связи, выход строба сопровождения данных источ- 5 ника информации подключен к второму входу второго регистра сдвига и к установочному входу счетчика числа переданных бит, выход тактового генератора соединен с входом делителя частоты, выход первого мультиплексора подключен к второй линии связи, к тактовому входу D-триггера формирования импульса синхронизации и к первому входу первого элемента И, 5 выход формирователя коротких импульсов соединен с установочным входом делителя чистоты, выход третьего блока задержки подключен к второму входу первого элемента И, выход ко- 0 торого соединен с тактовым входом

второго регистра сдвига, выход второго блока задержки подключен к входу установки счетчика числа принятых бит, первый и второй выходы дешифра- 5 тора длительности входных импульсой соединены с вторыми входами соответственно RS-триггера значения бита и RS-триггера синхронизации, а D-вход D-триггера формирования импульса

синхронизации заземлен, отличающееся тем, что, с целью повьппения достоверности приема при обмене цифровой информацией по последовательным каналам в дуплексном режиме, введены последовательно соединенные первьп RS-триггер, элемент ИЛИ, первый D-триггер и второй мультиплексор, выход которого подключен

к первому управляющему входу первого мультиплексора, и последовательно соединенные второй RS-триггер, пятый блок задержки, второй D-триггер и второй элемент И, выход которого под ключен к входу готовности источника информации, первый и второй выходы дешифратора числа принятых бит соединены с первыми входами соответственно первого RS-триггера и триггера Буфер заполнен, выход которого подключен к второму входу элемента ИЛИ, и к входу четвертого блока задержки, выход второго блока задержки подключен к тактовому входу второго П-триг гера и к втодому входу первого RS- триггера, выход первого регистра

сдвига соединен с информационным входом блока потребителя информации, выход Буфер сосчитан которого подключен к второму входу триггера Буфер заполнен, третий выход дешифратора длительности входных импульсов соединен с первым входом второго RS-триггера, выход формирователя прямоугольных импульсов подключен к второму входу второго RS-триггера, выход дешифратора числа переданных бит соединен с установочным входом второго D-триггера и с вторым входом второго элемента И, выход второго регистра сдвига подключен к второму входу второго мультиплексора, выход D-триггера формирования импульса синхронизации соединен с управляющим входом второго мультиплексора и с вторым управляющим входом первого мультиплексора, §ыход третьего блока задержки подключен к управляющему входу второго регистра сдвига, а выход первого мультиплексора соединен с тактовым входом первого П-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема информации | 1990 |

|

SU1748276A1 |

| Устройство для приема и передачи цифровой двоичной информации | 1989 |

|

SU1693734A1 |

| Устройство для последовательного обмена данными с квитированием | 1989 |

|

SU1720164A1 |

| Устройство для передачи и приема двоичной информации | 1989 |

|

SU1688439A1 |

| Устройство для приема и передачи двоичной информации | 1984 |

|

SU1748275A1 |

| Устройство для передачи и приема данных | 1988 |

|

SU1589417A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1665529A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1721836A2 |

| Устройство для передачи и приема данных в полудуплексном режиме | 1990 |

|

SU1732485A1 |

| Устройство для приема и передачи данных | 1989 |

|

SU1688438A1 |

Изобретение относится к технике связи. Цель изобретения - повышение достоверности приема при обмене цифровой информацией по последовательным каналам в дуплексном режиме. Устройство содержит тактовый генератор 1, усилитель 2, фильтр 3 нижних частот, формирователь 4 прямоугольных импульсов, счетчик 5 числа принятых бит, дешифратор 6 числа принятых бит, триггер 8 "буфер заполнен", блоки 10,16,17 и 28 задержки - счетчик 11 тактовых импульсов, дешифратор 12 длительности входных импульсов, RS - триггер 13 значения бита, RS - триггер 14 синхронизации, регистры 19 и 24 сдвига, блок 21 потребления информации, источник 23 информации, делитель 25 частоты, мультиплексор 26, элемент И 27, счетчик 29 числа переданных бит, дешифратор 30 числа переданных бит, D - триггер 31 формирования импульса синхронизации, формирователь 34 коротких импульсов и линии 35 и 36 связи. Цель достигается введением RS - триггеров 7 и 15, элемента ИЛИ 9, блока 18 задержки, D - триггеров 20 и 33, элемента И 22 и мультиплексора 32. 2 ил.

rpij rina. инрирмацилниыя uJttnt/MCoo (SaUm

tlTLJllRJinmi Синховаипу ке ff.is еторпго SHuvcnan сигнала lonosHocma к п/)иему

| Сурнин А.И., Савельев А.И | |||

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| - Серия препринтов сообщений Автоматизация научных исследований | |||

| - Сыктьшкар, Коми филиал АН СССР, 1984, с.6-10,рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-09-07—Публикация

1987-07-06—Подача