держит блок 4,обработки данных, де- шиАратор 5 адресов, формирователь 7 сигналов управления, блок 6 захвата шин и блок R параллельного интер1

Изобретение относится к цифровой вычислительной технике, в частности к средствам автоматизации контроля и поиска неисправностей микропр оцес- сорной аппаратуры, и может быть ис- . пользовано для отладки аппаратных и программных средств цифровых, систем управления с использованием микропроцессоров.

Цель изобретения - упрощение устройства.

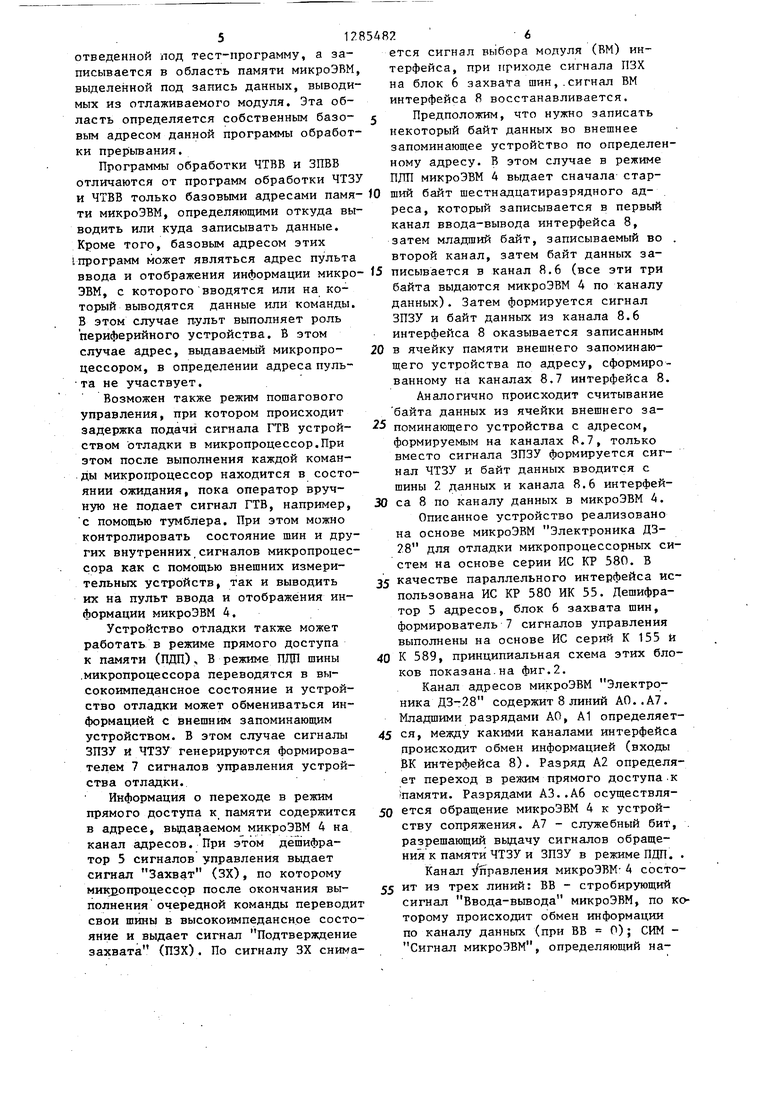

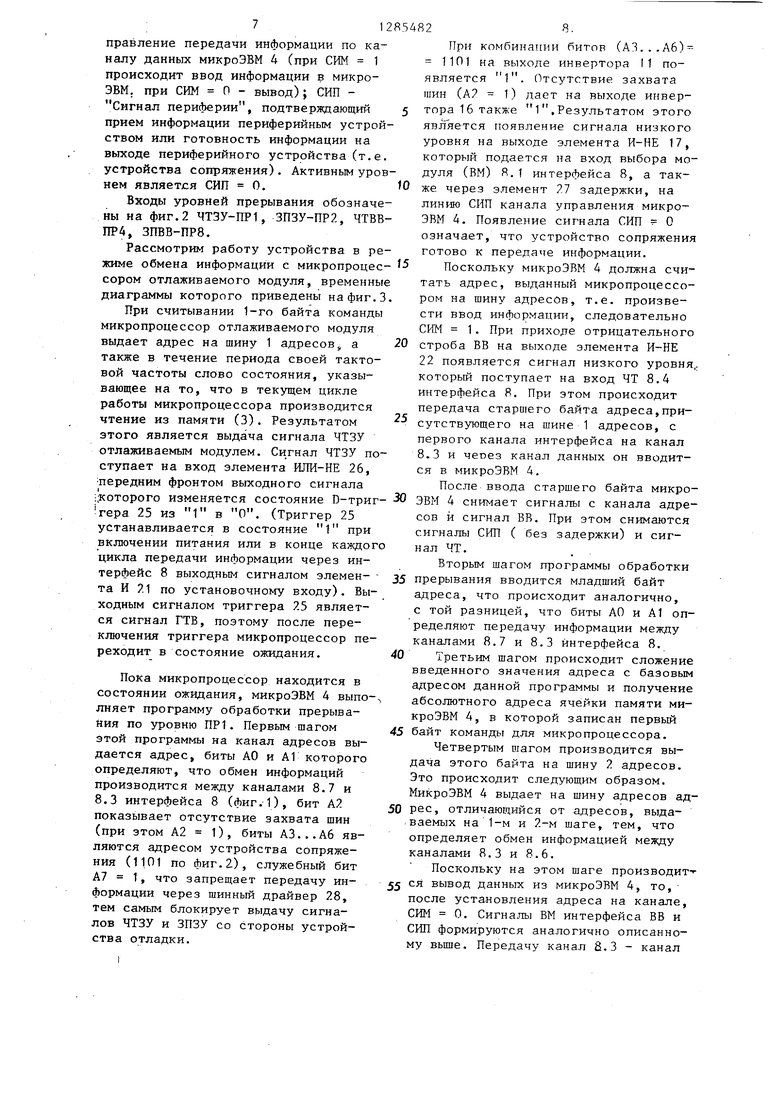

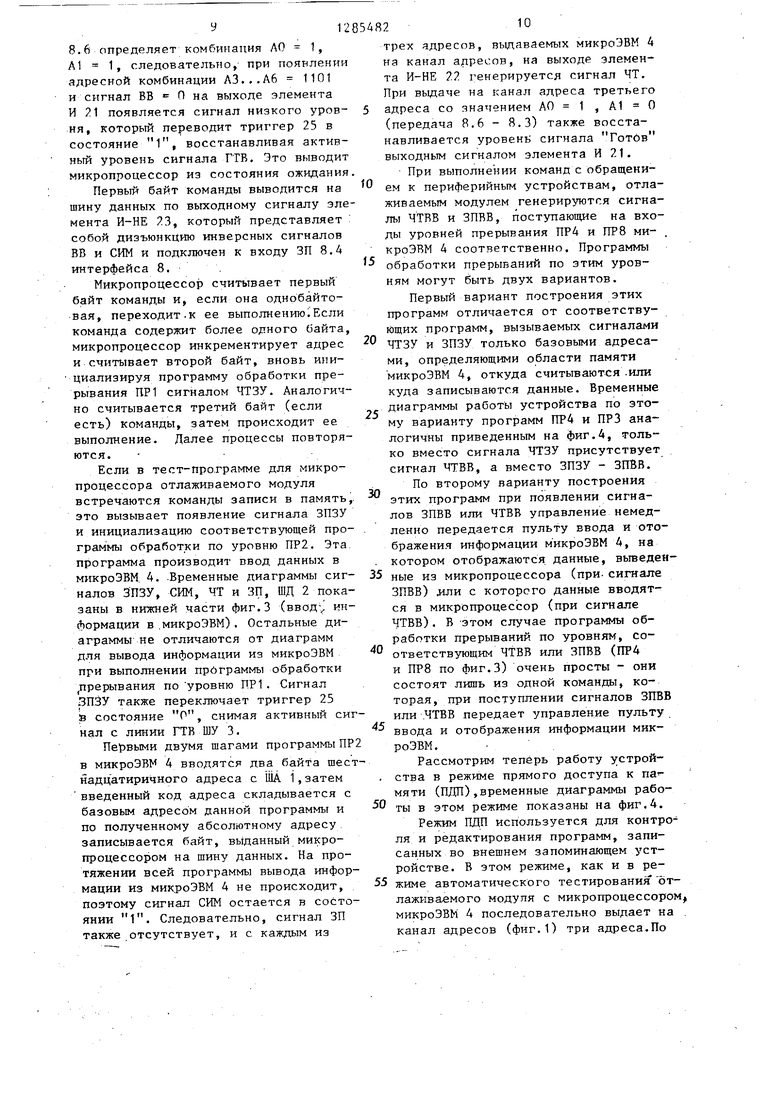

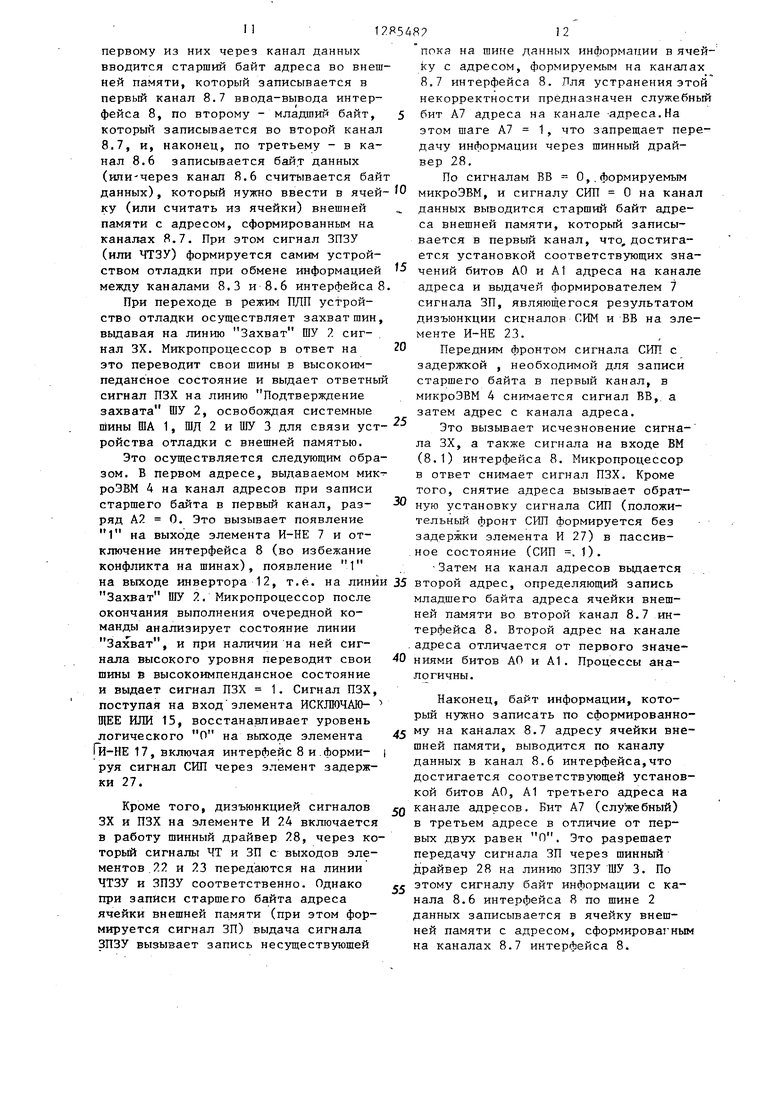

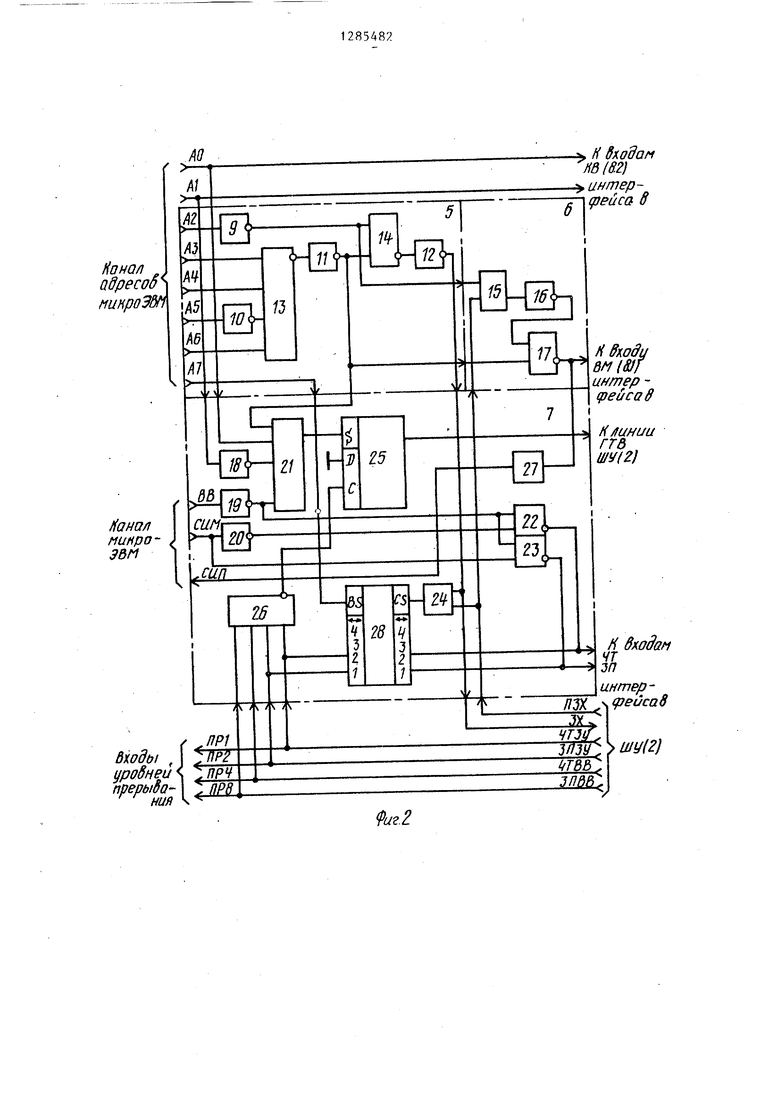

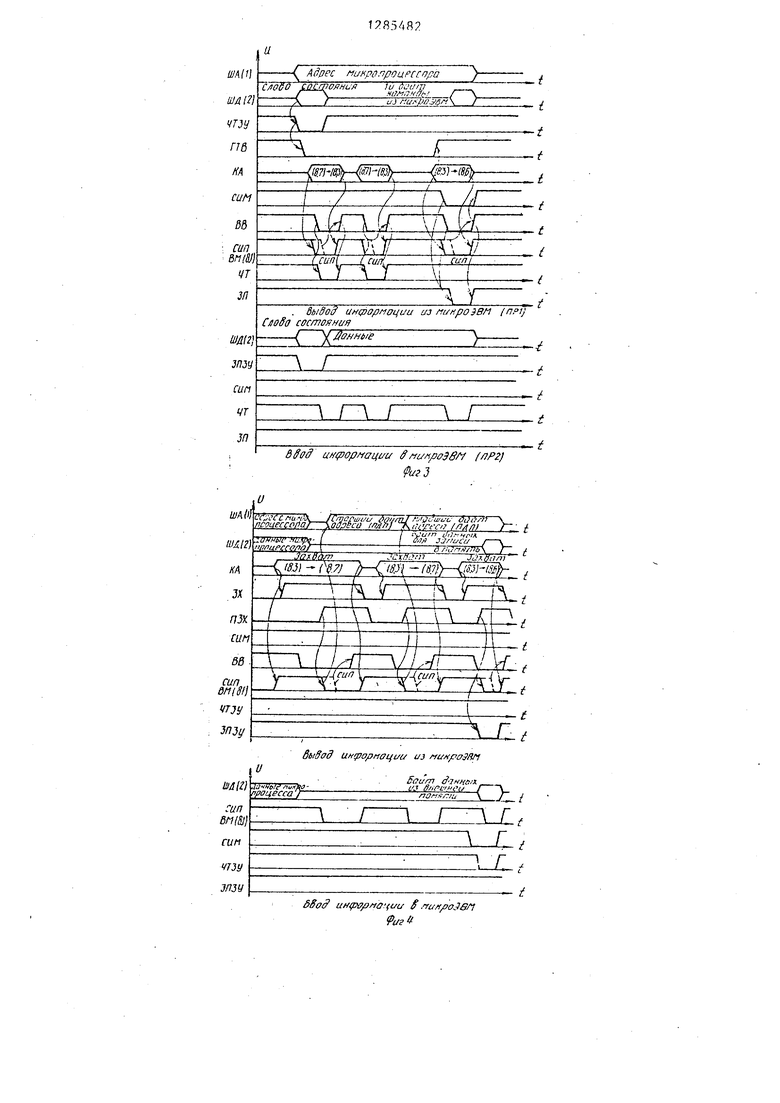

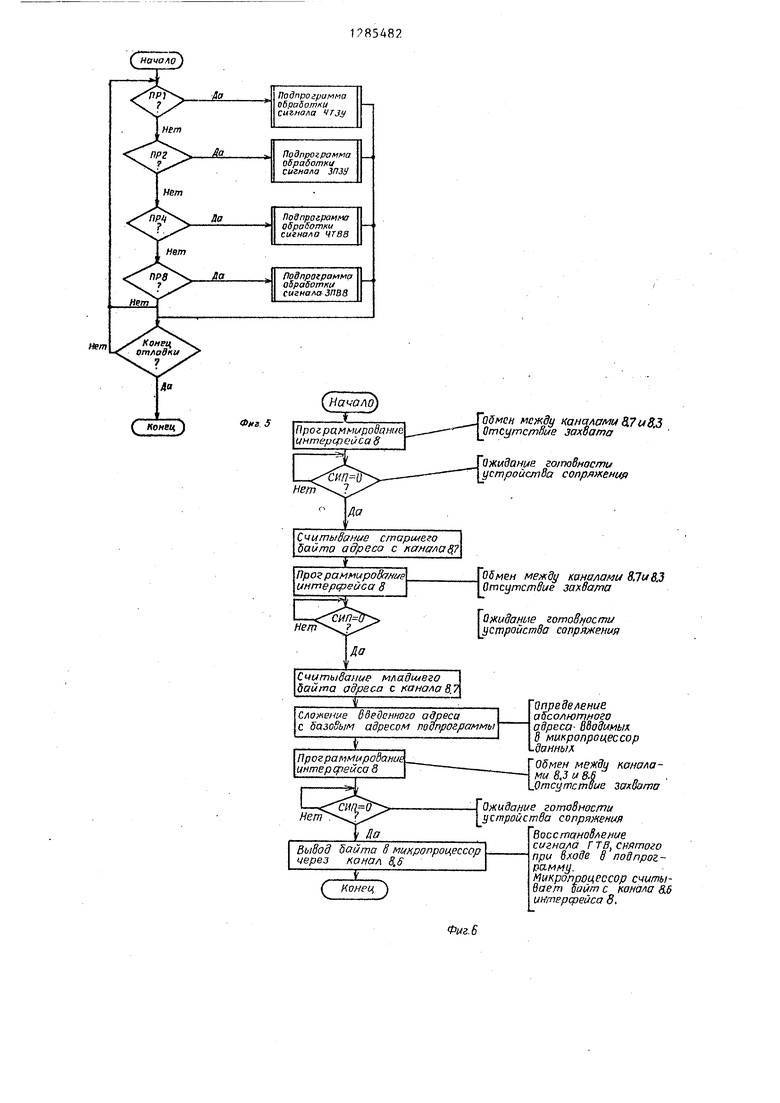

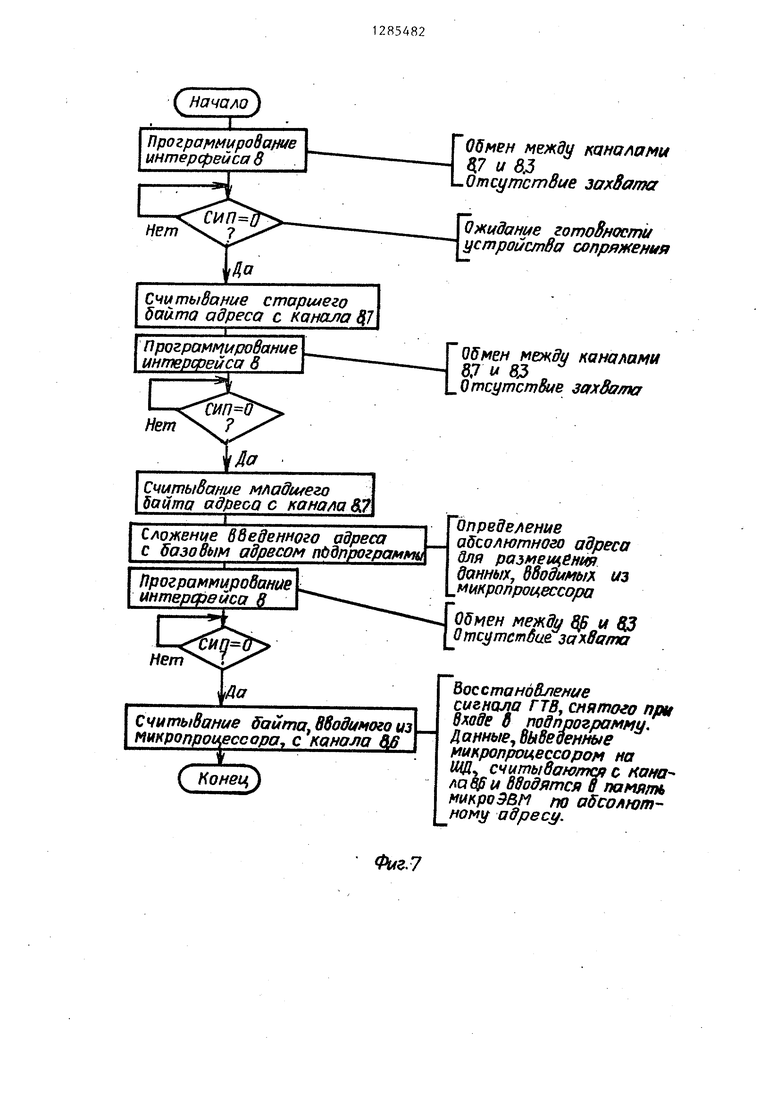

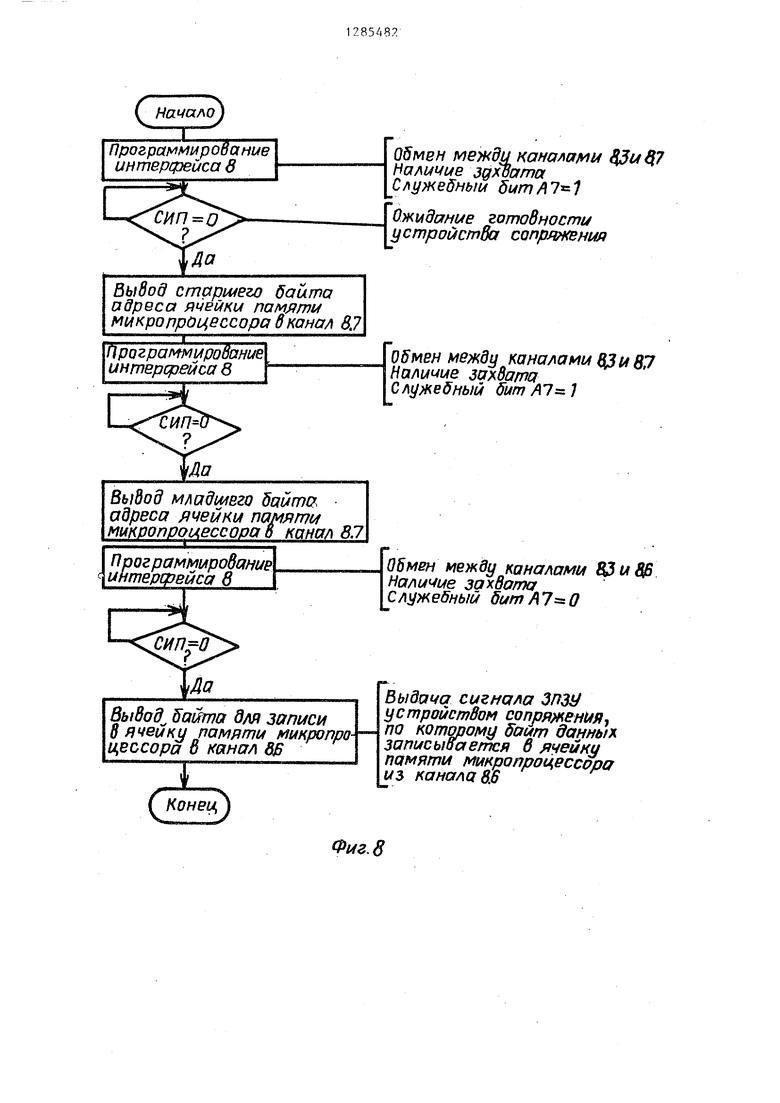

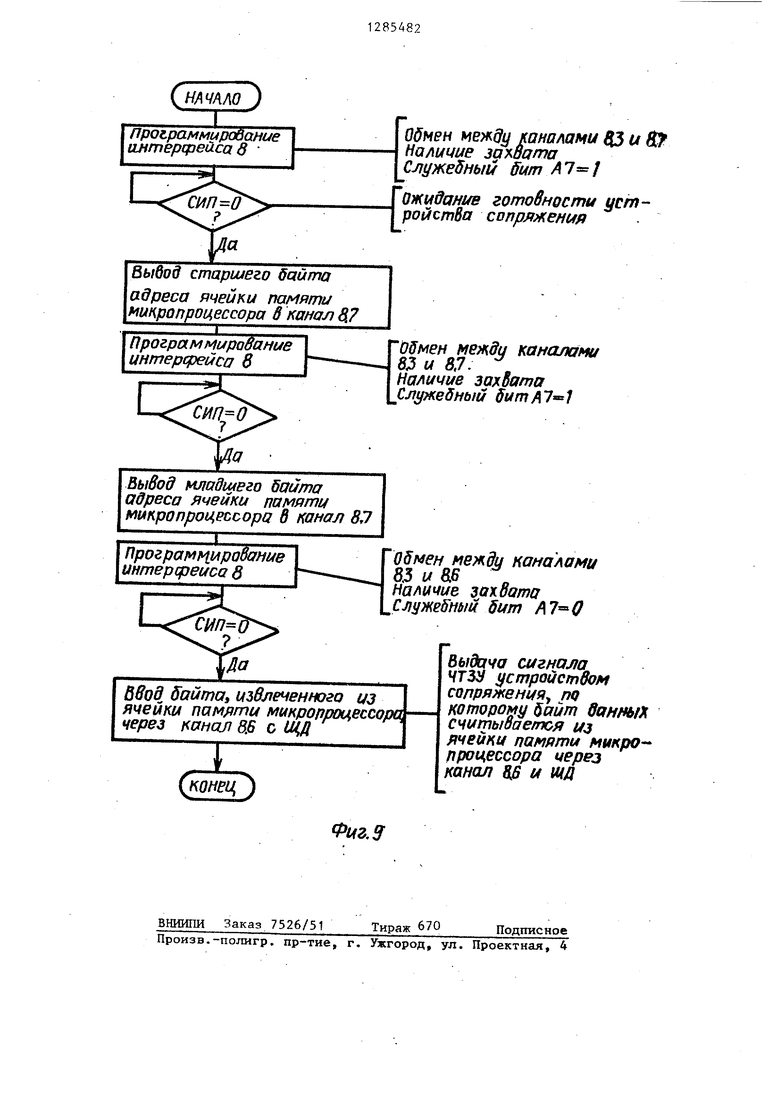

На фиг,1 представлена функциональная схема устройства для отладки микропроцессорных систем; на фиг.2 - функциональные схемы дешифратора адресов, блока захвата шин и формирователя сигналов управления со связями; на фиг.З - временные диаграммы работы устройства в режиме обмена информацией между блоком обработки Данных и отлаживаемой микропроцессорной системой; на фиг.4 - временные диаграммы работы устройства в режиме прямого доступа к памяти; на фиг.З - основной алгоритм работы блока обработки данных в процессе отладки; на Лиг.6 - алгоритм под программ обработки сигналов чтение из памяти (ЧТЗУ) и чтение из порта ввода-вывода (ЧТВВ); на фиг.7 - алгоритм подпрограмм обработки .сигналов запись в память (ПЗУ) и запись в порт ввода-вывода (ЗПВВ) ; на фиг. 8 алгоритм работы устройства в режиме прямого доступа к памяти (ПДП) при записи в память; на фиг. 9 - алгоритм работы устройства в режиме ПДП .при чтении из памяти.

Устройство (фиг.1) содержит шину адресов (ША) 1, шину данных (ШД) 2, шину управления (ШУ) 3 отлаживаемой микропроцессорной системы, блок 4 обработки данных, дешифратор 5 адресов, блок 6 захвата шин, формирователь 7 сигналов управления, блок 8 параллельного интерфейса, имеющий

фейса. В качестве блока обработки данных используется микроЭВМ. 1 3.п. ф-лы, 9 ил. .

5

0

5

0

5

0

5

вход 8,1 выбора модуля (ВМ), входы 8.2 выбора канала (ВК), информационный вход-выход 8.3, входы 8.4 Чтение (ЧТ) и Запись (ЗП), вход 8.5 сброса, входы-выходы данных 8.6 и адреса 8,7. На фиг.1 также даны обозначения: Сброс - СЕР, Готов - ГТВ, Чтение из памяти - ЧТЗУ, Запись в память - .ЗПЗУ, Чтение из порта авода-вывода - ЧТВВ, Запись в порт ввода-вывода - ЗПВВ, Захват - ЗХ, Подтверждение захвата - ПЗХ.

Дешифратор 5 адресов (фиг.2) содержит первый 9, второй 10, третий 11 и четвертый 12 элементы НЕ, первый 13 и второй 14 элементы И-НЕ, ,

Блок захвата шин 6 (фиг,2) содержит элемент ЙСКЛЮЧАКЯЦЕЕ ИЛИ 15, элемент НЕ 16, элемент И-НЕ 17,

Формирователь 7 сигналов управления (фиг.2) содержит первь1й 18, . второй 19 и третий 20 элементы НЕ, первый элемент И 21, первый 22 и второй 23 элементы И-НЕ, второй элемент И 24, D-триггер 25, элемент ИЛИ-НЕ 26, элемент 27 задержки, шинный формирователь 28.

Принцип работы устройства отладки состоит в том, что блок обработки данных (в качестве которого используется микроэвм) со схемой сопряжения являются по отношению к от- лаживаемому модулю (отлаживаемой микропроцессорной системе) эмулятором как памяти, так и внешних (периферийных) устройств ввода-вывода. Адрес, выдаваемый микропроцессором отлаживаемого модуля на шину адре- ,GOB, интерпретируется микроЭВМ как адрес ячейки памяти последней, где для микропроцессора записана команда, или же как адрес, по которому микропроцессор записывает какие-либо данные. Обмен информацией осуществляется через устройство сопряжения, состоящее из дешифратора 5 адресов,блка 6 захвата шин, формирователя 7 сигналов управления и блока. 8 парал лелт ного интерфейса, которое вкупе с микроэвм и является устройством оладки.

Адрес, выдаваемый микроЭВМ на выход адреса, содержит информацию об обращении к периферийному устройству, котррым в данном случае является устройство отладки, информацию о направлении передачи через интерфейс (два младших бита - АО и А1, фиг.2), информацию о переходе в режим прямого доступа к памяти и служебный бит,разрешающий выдачу сигналов ЧТЗУ и ЗПЗУ при прямом доступе к памяти.

На шину адресов (FJIA) 1 выдаются адреса из микропроцессора, которые побайтно через интерфейс 8 вводятся в блок 4 обработки данных (микроЭВМ через вход-выход данных. Данные из микропроцессора в микроЭВМ или наоброт передаются также по каналу данных микроэвм через интерфейс 8. По шине управления Ш 3 передаются в отлаживаемый модуль сигналы Готов и Захват и поступают из микропроцессора сигналы Сброс, Подтверждение захвата, а также сигналы обращения к памяти и периферии (ЧТЗУ, ЗПЗУ, ЧТВВ, ЗПВВ). По каналу управления микроэвм поступают сигналы, под действием которых формирователь 7 сигналов управления осуществляет взаимную работу блоков устройства отладки, микроэвм и отлаживаемого модуля,

Устройство (фиг.1) работает следующим образом.

После включения питания микропроцессор отлаживаемого модуля (не по- казан) вьщает на шину 1 адресов начальный адрес, сигнал СВР на вход 8,5 интерфейса, а также сигнал ЧТЗУ свидетельствующий о том, что микропроцессор должен принять первый байт команды, записанной по начальному адресу. В ответ на любой из сиг- 50 ропроцессо.ром вызывает появление сигналов обращения ЧТЗУ, ЗПЗУ, ЧТВВ, налов ЗПЗУ или ЧТВВ и ЗПВВ соответ- .ЗПВВ формирователь сигналов управле- ственно. Эти сигналы, поступая на ния снимает сигнал ГТВ, переведя микропроцессор в состояние ожидания.

входы прерывания микроЭВМ, инициируют соответствующие программы из обра- а в микроэвм 4 по каждому из сигна- 55 ботки. Программа обработки прерывания лов обращения инициализируется соот- по сигналу ЗПЗУ отличается от програм- ветствующая программа обработки прерывания. По сигналам ЧТЗУ и ЧТВВ

мы обработки сигнала ЧТЗУ тем, что байт данных по этой программе не выводится из области памяти микроЭВМ,

инициализируются программы вывода

информации из микроЗВМ 4 в микропроцессор. Эти программы отличаются только областями адресуемой памяти, где записаны выводимые данные, кро- 5 ме того, программа ЧТВВ может адресоваться к пульту ввода и отображения информации микроэвм, который в этом случае заменяет периферийное устройство ввода-вывода. Аналогич- 0 ные программы для ввода информации ,в память микроэвм или на пульт инициализируются сигналами ЗПЗУ и ЗПВВ. По сигналу ЧТЗУ, поступающему из отлаживаемого модуля микропроцессор- 5 ной системы вместе с начальным адресом, инициализируется программа вывода информации из микроэвм 4 в ми- кропроцессор, работающая следующим образом. Начальный адрес с шины 1 0 адресов побайтно вводится через блок 8 параллельного интерфейса по каналу данных в микроэвм 4. Этот адрес складывается с базовым адресом программы обработки прерывания микро- 5 ЭВМ 4, в результате получается адрес ячейки памяти, где записана команда для микропроцессора. Первый байт этой команды через канал данных и интерфейс 8 выводится на шину 2 0 данных. При этом восстанавливается уровень сигнала ГТВ и микропроцессор считывает выведенный байт с шины 2 данных. Аналогично считываются другие байты (если они есть) этой команды и микропроцессор приступает к ее выполнению. После выполнения первой команды микропроцессор инкре- ментирует адрес, вновь вьщает сигнал ЧТЗУ и считывает первый байт следу- 0 ющей команды, записанной в памяти машины следом за предьщущей. Таким образом, в микропроцессор возможно ввести некоторую тест-программу, по выполнении которой можно судить о 5 правильности функционирования отла живаемого модуля.

Тест-программа может содержать команды записи в память или обращения к периферии, выполнение которых миквходы прерывания микроЭВМ, инициируют соответствующие программы из обра- ботки. Программа обработки прерывания по сигналу ЗПЗУ отличается от програм

мы обработки сигнала ЧТЗУ тем, что байт данных по этой программе не выводится из области памяти микроЭВМ,

отведенной под тест-программу, а записывается в область памяти микроЭВМ выделенной под запись данных, выводимых из отлаживаемого модуля. Эта область определяется собственным базо- вым адресом данной программы обработки прер ьтания.

Программы обработки ЧТВВ и ЗПВВ отличаются от программ обработки ЧТЗ и ЧТВВ только базовыми адресами памя ти микроэвм, определяющими откуда выводить или куда записывать данные. Кроме того, базовым адресом этих программ может являться адрес пульта ввода и отображения информации микро ЭВМ, с которого вводятся или на который выводятся данные или команды. В этом случае пульт выполняет роль периферийного устройства. В этом случае адрес, выдаваемый микропроцессором, в определении адреса пуль- та не участвует.

Возможен также режим пошагового управления, при котором происходит задержка подачи сигнала ГТВ устройством отладки в микропроцессор.При этом после выполнения каждой команды микрогфоцессор находится в состоянии ожидания, пока оператор вручную не подает сигнал ГТВ, например, с помощью тумблера. При этом можно контролировать состояние шин и других внутренних,сигналов микропроцессора как с помощью внешних измерительных устройств, так и выводить их на пульт ввода и отображения информации микроэвм 4.

Устройство отладки также может работать в режиме прямого доступа к памяти (ПДП), В режиме ПДП шины .микропроцессора переводятся в вы- сокоимпедансное состояние и устройство отладки может обмениваться информацией с внешним запоминающим устройством. В этом случае сигналы ЗПЗУ и ЧТЗУ генерируются формирователем 7 сигналов управления устройства отладки.

Информация о переходе в режим прямого доступа к памяти содержится в адресе, вьщаваемом микроЭВМ 4 на канал адресов. При этом дешифратор 5 сигналов управления вьщает сигнал Захват (ЗХ), по которому мик;Еопроцессор после окончания выполнения очередной команды переводит свои шины в высокоимпедансное состояние и выдает сигнал Подтверждение захвата (ПЗХ). По сигналу ЗХ снима

ется сигнал выбора модуля (ВМ) интерфейса, при тфиходе сигнала ПЗХ на блок 6 захвата шин,.сигнал ВМ интерфейса 8 восстанавливается.

Предположим, что нужно записать некоторый байт данных во внешнее запоминающее устрой ство по определенному адресу. В этом случае в режиме ПДП микроэвм 4 выдает сначала старший байт шестнадцатиразрядного адреса, который записывается в первый канал ввода-вывода интерфейса 8, затем младший байт, записываемый во . второй канал, затем байт данных записывается в канал 8.6 (все эти три байта выдаются микроЭВМ 4 по каналу данных). Затем формируется сигнал ЗПЗУ и байт данных из канала 8.6 интерфейса 8 оказывается записанным в ячейку памяти внешнего запоминающего устройства по адресу, сформированному на каналах 8.7 интерфейса 8. Аналогично происходит считывание байта данных из ячейки внешнего за- поминающего устройства с адресом, формируемым на каналах 8.7, только вместо сигнала ЗПЗУ формируется сигнал ЧТЗУ и байт данных вводится с шины . данных и канала 8.6 интерфей- са 8 по каналу данных в микроЭВМ 4. Описанное устройство реализовано на основе микроЭВМ Электроника ДЗ- 28 для отладки микропроцессорных систем на основе серии ИС КР 580. В качестве параллельного интерфейса использована ИС КР 580 ИК 55. Дешифратор 5 адресов, блок 6 захвата шин, формирователь 7 сигналов управления выполнены на основе ИС серий К 155 И К 589, принципиальная схема этих блоков показана.на фиг.2.

Канал адресов микроЭВМ Электроника ДЗ-28 содержит 8 линий АО..А7. Младшими разрядами АО, А1 определяется, между какими каналами интерфейса происходит обмен информацией (входы JBK интерфейса 8) . Разряд А2 определяет переход в режим прямого доступа.к памяти. Разрядами A3..А6 осуществля- ется обращение микроЭВМ 4 к устройству сопряжения. А7 - служебный бит, . разрешающий вьщачу сигналов обращения к памяти ЧТЗУ и ЗПЗУ в режиме ПДП. . Канал Уттравления микроЭВМ- 4 состо- ит из трех линий: ВВ - стробирующий сигнал Ввода-вьгеода микроЭВМ, по которому происходит обмен информации по каналу данных (при ВВ 0); СИМ - Сигнал микроэвм, определяющий на

71285482

равление передачи информации по кая ш т я к ду ж л о го

налу данных микроЭВМ 4 (при СИМ 1 происходит ввод информации в микро- ЭВМ, при СИМ П - вывод); СИП - Сигнал периферии, подтверждающий прием информации периферийным устройством или готовность информации на выходе периферийного устройства (т, е. устройства сопряжения). Активньм уровнем является СИП 0.

Входы уровней прерывания обозначены на фиг.2 ЧТЗУ-ПР1, ЗПЗУ-ПР2, ЧТВВ- ПР4, ЗПВВ-ПР8.

Рассмотрим работу устройства в режиме обмена информации с микропроцес- сором отлаживаемого модуля, временные диаграммы которого приведены на фиг.3

При считывании 1-го байта команды микропроцессор отлаживаемого модуля выдает адрес на шину 1 адресов, а также в течение периода своей тактовой частоты слово состояния, указывающее на то, что в текущем цикле работы микропроцессора производится чтение из памяти (3). Результатом этого является выдача сигнала ЧТЗУ отлаживаемым модулем. Сигнал ЧТЗУ поступает на вход элемента ИЖ-НЕ 26, передним фронтом выходного сигнала i,KoToporo изменяется состояние D-триг- гера 25 из 1 в О. (Триггер 25 устанавливается в состояние 1 при включении питания или в конце каждого цикла передачи информации через интерфейс 8 выходным сигналом элемен- та И 21 по установочному входу). Выходным сигналом триггера 25 является сигнал ГТВ, поэтому после переключения триггера микропроцессор переходит в состояние ожидания.

Пока микропроцессор находится в состоянии ожидания, микроЭВМ 4 выпо лняет программу обработки прерывания по уровню ПР1. Первым шагом этой программы на канал адресов выдается адрес, биты АО и А1 которого определяют, что обмен информации производится между каналами 8.7 и 8.3 интерфейса 8 (фиг.1), бит А2 показывает отсутствие захвата шин (при этом А2 1), биты АЗ...А6 являются адресом устройства сопряжения (1101 по фиг.2), служебный бит А7 1, что запрещает передачу информации через шинный драйвер 28, тем самым блокирует выдачу сигналов ЧТЗУ и ЗПЗУ со стороны устройства отладки.

8.

При комбинации битов (АЗ,..А6) 1101 на выходе инвертора 11 появляется 1. Отсутствие захвата шин (А2 1) дает на выходе инвертора 16 также 1.Результатом этого является появление сигнала низкого уровня на выходе элемента И-НЕ 17, который подается на вход выбора модуля (ВМ) 8.1 интерфейса 8, а также через элемент 27 задержки, на линию СИП канала управления микро- ЭВМ 4. Появление сигнала СИП О означает, что устройство сопряжения готово к передаче информации.

Поскольку микроэвм 4 должна считать адрес, выданный микропроцессором на шину адресов, т.е. произвести ввод информации, следовательно СИМ 1. При приходе отрицательного строба ВВ на выходе элемента И-НЕ 22 появляется сигнал низкого уровня,, который поступает на вход ЧТ 8.4 интерфейса 8. При этом происходит передача старшего байта адреса,присутствующего на шине 1 адресов, с

первого канала интерфейса на канал 8.3 и чеоез канал данных он вводится в микроэвм 4.

После ввода старшего байта микро- ЭВМ 4 снимает сигналы с канала адресов и сигнал ВВ. При этом снимаются сигналы СИП ( без задержки) и сигнал ЧТ.

Вторым шагом программы обработки

прерывания вводится младший байт адреса, что происходит аналогично, с той разницей, что биты АО и А1 определяют передачу информации между каналами 8.7 и 8.3 интерфейса 8.

Третьим шагом происходит сложение введенного значения адреса с базовым адресом данной программы и получение абсолютного адреса ячейки памяти микроЭВМ 4, в которой записан первый

байт команды для микропроцессора.

Четвертым шагом производится выдача этого байта на шину 2 адресов. Это происходит следующим образом. Микроэвм 4 выдает на шину адресов адрес, отличающийся от адресов, выдаваемых на 1-м и 2-м шаге, тем, что определяет обмен информацией между каналами 8.3 и 8.6.

Поскольку на этом шаге производится вывод данных из микроЭВМ 4, то, после установления адреса на канале, СИМ 0. Сигналы ВМ интерфейса ВВ и СИП формируются аналогично описанному вьш1е. Передачу канал 8.3 - канал

8.6 определяет комбинация ЛО 1, А1 1, следовательтю, при появлении адресной комбинации ЛЗ...А6 1101 и сигнал ВВ О на выходе элемента И 21 появляется сигнал низкого уровня, который переводит триггер 25 в состояние 1, восстанавливая активный уровень сигнала ГТВ. Это выводит микропроцессор из состояния ожидания

Первый байт команды выводится на шину данных по выходному сигналу элемента И-НЕ 23, который представляет собой дизъюнкцию инверсных сигналов ВВ и СИМ и подключен к входу ЗП 8.А интерфейса В. .

Микропроцессор считывает первый байт команды и, если она однрбайто- вая, переходит.к ее выполнению Если команда содержит более одного байта, микропроцессор инкрементирует адрес и считывает второй байт, вновь инициализируя программу обработки прерывания ПР1 сигналом ЧТЗУ. Аналогично считывается третий байт (если есть) команды, затем происходит ее выполнение. Далее процессы повторяются.

Если в тест-Программе для микропроцессора отлаживаемого модуля встречаются команды записи в память это вызывает появление сигнала ЗПЗУ и инициализацию соответствующей программы обработки по уровню ПР2. Эта программа производит ввод данных в микроэвм. 4. .Временные диаграммы сигналов З ПЗУ, СИМ, ЧТ и ЗП, ШД 2 показаны в нижней части фиг.З (ввод-. информации в .микроэвм). Остальные диаграммы не отличаются от диаграмм для вывода информации из микроЭВМ при выполнении прйграммы обработки прерывания по уровню ПР1 . Сигнал ЭПЗУ также переключает триггер 25 и состояние О, снимая активный сигнал с линии ГТВ ШУ 3.

Первыми двумя шагами программы ПР

в микроэвм 4 вводятся два байта шестнадцатиричного адреса с ША 1,затем введенный код адреса складывается с базовым адресом данной программы и по полученному абсолютному адресу записывается байт, выданный микропроцессором на шину данных. На протяжении всей программы вывода информации из микроэвм 4 не происходит, поэтому сигнал СИМ остается в состоянии 1. Следовательно, сигнал ЗП также отсутствует, и с каждым из

трех адресов, выдаваемых микроЭВМ 4 на канал адресов, на выходе элемента И-НЕ 22 генерируется сигнал ЧТ. При выдаче на канал адреса третьего адреса со значением АО 1 , А1 О (передача 8.6 - 8.3) также восстанавливается уровень сигнала Готбв выходным сигналом элемента И 21.

При выполнении команд с обращением к периферийным устройствам, отлаживаемым модулем генерируются сигналы ЧТВВ и ЗПВВ, поступающие на входы уровней прерывания ПР4 и ПР8 микроЭВМ 4 соответственно. Программы обработки прерываний по этим уровням могут быть двух вариантов.

Первый вариант построения этих программ отличается от соответству

0

5

0

5

0

5

0

5

Ющих программ, вызываемых сигналами ЧТЗУ и ЗПЗУ только базовыми адресами, определяющими области памяти микроэвм 4, откуда считываются .или куда записываются данные. Временные диаграммы работы устройства по этому варианту программ ПР4 и ПРЗ аналогичны приведенным на фиг.4, только вместо сигнала ЧТЗУ присутствует сигнал ЧТВВ, а вместо ЗПЗУ - ЗПВВ.

По второму варианту построения этих программ при появлении сигналов ЗПВВ или ЧТВВ управление немедленно передается пульту ввода и отображения информации микроэвм 4, на котором отображаются данные, выведенные из микропроцессора (при- сигнале ЗПВВ) лли с которого данные вводятся в микропроцессор (при сигнале ЧТВВ). В этом случае программы обработки прерываний по уровням, соответствующим ЧТВВ или ЗПВВ (ПР4 и ПР8 по фиг.З) очень просты - они состоят лишь из одной команды, которая, при поступлении сигналов ЗПВВ или .ЧТВВ передает управление пульту ввода и отображения информации микроЭВМ.

Рассмотрим теперь работу устройства в режиме прямого доступа к ПЗ - мяти (ПДП),временные диаграммы работы в этом режиме показаны на фиг,4.

Режим ПДП используется для контроля и редактирования программ, записанных во внешнем запоминающем устройстве. В этом режиме, как и в режиме автоматического тестирования отлаживаемого модуля с микропроцессором, микроэвм 4 последовательно выдает на . канал адресов (фиг.1) три адреса.По

первому из них через канал данных вводится старший байт адреса во внешней памяти, который записывается в первый канал 8.7 ввода-вывода интерфейса 8, по второму - младший байт, который записывается во второй канал 8.7, и, наконец, по третьему - в канал 8.6 записывается байт данных (ипи-через канал 8.6 считывается байт

12Я548 12

пока на шине данных информации в ячей ку с адресом, формируемым на каналах 8.7 интерфейса 8. Лля устранения этой некорректности предназначен служебный бит А7 адреса на канале -адреса. На этом шаге А7 1, что запрещает передачу информации через шинный драйвер 28.

По сигналам ВВ О,,формируемым

15

20

данных), который нужно ввести в ячей- О микроЭВМ, и сигналу СИП О на канал ку (или считать из ячейки) внешней памяти с адресом, сформированным на каналах 8.7. При этом сигнал ЗПЗУ (или ЧТЗУ) формируется самим устройством отладки при обмене информацией между каналами 8.3 и 8.6 интерфейса 8

При переходе в режим ПДП устройство отладки осуществляет захват шин, выдавая на линию Захват ШУ 2 сигнал ЗХ. Микропроцессор в ответ на это переводит свои шины в высокоим- педансное состояние и выдает ответный сигнал ПЗХ на линию Подтверждение захвата ШУ 2, освобождая системные шины ША 1, ШД 2 и ШУ 3 для связи уст- ройства отладки с внешней памятью.

Это осуществляется следующим образом. В первом адресе, выдаваемом мик- роЭВМ 4 на канал адресов при записи старшего байта в первый канал, разряд А2 0. Это вызывает появление 1 на выходе элемента И-НЕ 7 и отключение интерфейса В (во избежание конфликта на шинах), появление 1

30

данных выводится старший байт адреса внешней памяти, который записывается в первый канал, что, достигается установкой соответствующих значений битов АО и А1 адреса на канале адреса и выдачей формирователем 7 сигнала ЗП, являющегося результатом дизъюнкции сигналов СИМ и ВВ на зле- менте И-НЕ 23.

Передним фронтом сигнала СИП с задержкой , необходимой для записи старшего байта в первый канал, в микроэвм 4 снимается сигнал ВВ,. а затем адрес с канала адреса.

Это вызывает исчезновение сигнала ЗХ, а также сигнала на входе ВМ (8.1) интерфейса 8. Микропроцессор в ответ снимает сигнал ПЗХ. Кроме того, снятие адреса вызывает обратную установку сигнала СИП (положительный фронт СИП формируется без задержки элемента И 27) в пассивное состояние (СИП .1).

Затем на канал адресов выдается

на выходе инвертора 12, т.е. на линии 35 второй адрес, определяющий запись

Захват ШУ 2, Микропроцессор после окончания выполнения очередной команды анализирует состояние линии Захват, и при наличии на ней сигнала высокого уровня переводит свои шины в высокоимпендансное состояние и выдает сигнал ПЗХ 1. Сигнал ПЗХ, поступая на вход элемента ИСКЛЮЧАЮ- ЩЕЕ ИЛИ 15, восстанавливает уровень логического О на выходе элемента ГИ-НЕ 17, включая интерфейс 8 и.формируя сигнал СИП через элемент задержки 27.

младшего байта адреса ячейки внешней памяти во второй канал 8.7 интерфейса 8. Второй адрес на канале адреса отличается от первого знане 40 ниями битов АО и А1. Процессы аналогичны.

Наконец, байт информации, который нужно записать по сформированн

45 му на каналах 8.7 адресу ячейки вн шней памяти, выводится по каналу данных в канал 8.6 интерфейса,что достигается соответствующей устано кой битов АО, А1 третьего адреса н

Кроме того, дизъюнкцией сигналов ЗХ и ПЗХ на элементе И 24 включается в работу шинный драйвер 28, через который сигналы ЧТ и ЗП с выходов элементов .22 и 23 передаются на линии ЧТЗУ и ЗПЗУ соответственно. Однако при записи старшего ба.йта адреса ячейки внешней памяти (при этом формируется сигнал ЗП) выдача сигнала ЗПЗУ вызывает запись несуществующей

пока на шине данных информации в ячейку с адресом, формируемым на каналах 8.7 интерфейса 8. Лля устранения этой некорректности предназначен служебный бит А7 адреса на канале -адреса. На этом шаге А7 1, что запрещает передачу информации через шинный драйвер 28.

По сигналам ВВ О,,формируемым

О микроЭВМ, и сигналу СИП О на канал

микроЭВМ, и сигналу СИП О на канал

данных выводится старший байт адреса внешней памяти, который записывается в первый канал, что, достигается установкой соответствующих значений битов АО и А1 адреса на канале адреса и выдачей формирователем 7 сигнала ЗП, являющегося результатом дизъюнкции сигналов СИМ и ВВ на зле- менте И-НЕ 23.

Передним фронтом сигнала СИП с задержкой , необходимой для записи старшего байта в первый канал, в микроэвм 4 снимается сигнал ВВ,. а затем адрес с канала адреса.

Это вызывает исчезновение сигнала ЗХ, а также сигнала на входе ВМ (8.1) интерфейса 8. Микропроцессор в ответ снимает сигнал ПЗХ. Кроме того, снятие адреса вызывает обратную установку сигнала СИП (положительный фронт СИП формируется без задержки элемента И 27) в пассивное состояние (СИП .1).

Затем на канал адресов выдается

младшего байта адреса ячейки внешней памяти во второй канал 8.7 интерфейса 8. Второй адрес на канале адреса отличается от первого знане- 40 ниями битов АО и А1. Процессы аналогичны.

Наконец, байт информации, который нужно записать по сформированно45 му на каналах 8.7 адресу ячейки внешней памяти, выводится по каналу данных в канал 8.6 интерфейса,что достигается соответствующей установкой битов АО, А1 третьего адреса на

5Q канале адресов. Бит А7 (служебный) в третьем адресе в отличие от первых цвух равен О. Это разрешает передачу сигнала ЗП через шинный драйвер 28 на линию ЗПЗУ ШУ 3. По

г этому сигналу байт информации с канала 8.6 интерфейса 8 по шине 2 данных записывается в ячейку внешней памяти с адресом, сформироват ным на каналах 8.7 интерфейса 8.

13

Считывание информации из ячейки внешней памяти в режиме ПЛП происходит следующим образом. Вначале аналогично расмотренному выше на каналах 8.7 формируется адрес ячейки внешней памяти. Затем при выдаче на канал адреса третьего адреса, определяющего обмен между каналами 8.6 и 8.3 интерфейса 8, микроЭВМ выдает сигнал СШ, который при его дизъюнкции с сигналом ВВ на элементе И-НЕ 22 образует сигнал ЧТ. Служабньй би А7 при этом разрешает прохождение сигнала ГТ на линию ЧТЗУ ШУ 2, по которому из ячейки внешней памяти с адресом, сформированным на каналах 8.7 интерфейса 8, считывается байт, который по каналу данных заносится в микроЗВМ 4. Временные диаграммы этого процесса показаны в нижней части фиг.4 (ввод информации в микроэвм). ,

Таким образом, предлагаемое уст- . ройство способно осуществлять проверку работоспособности микропроцессорных систем путем автоматического прогона программ, записанных в памяти микроэвм или в режиме пошагово- ,го ввода команд, который легко достигается задержкой подачи в микроЭВМ сигнала готовности периферийного устройства (в рассмотренном устройстве СИП).

Формула изобретения

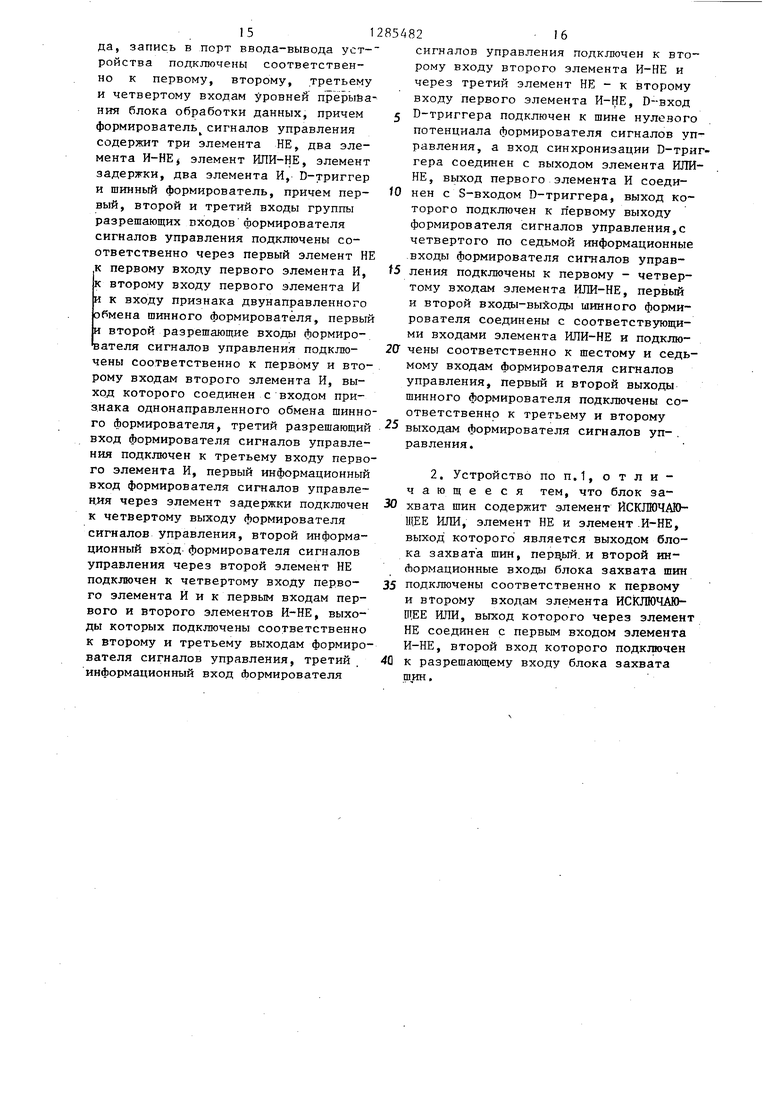

1. Устройство для отладки микропроцессорных систем, содержащее дешифратор адресов, формирователь сигналов управления и блок захвата шин, причем первый выход дешифратора адресов соединен с первым разрешающим входом формирователя сигналов управ- ленйй и является выходом сигнала Захват устройства для подключения к шине управления отлаживаемой микропроцессорной системы, первый выход формирователя управляющих сигналов является выходом сигнала Готов устройства для подлкючения к шине управления отлаживаемой микропроцессорной системы, отличающее ся тем, что, с целью упрощения устройства, содержит блок параллельного интерфейса и- блок обработки данных, входы-выходы адреса и данных блока параллельного интерфейса являются входами-выходами устройства для под14

0

5

ключения соответственно к шинам адреса и данных отлаживаемой микропроцессорной системы, выбора канала блока параллельного интерфейса, группа разрешающих входов формирователя сигналов управления и группа входов дешифратора адресов подключены к выходной шине адреса блока обработки данных, информационный вход- выход блока параллельного интерфейса подключен к двунаправленной шине данных блока обработки данных, выход блока захвата шин соединен с входом выбора модуля блока параллельного ин5 терфейса и первым информационным входом формирователя сигналов управления, второй и третий выходы формирователя сигналов управления соединены соответственно с входами чтения и записи блока параллельного интерфейса, первый информационный вход блока захвата шин и второй разрешающий вход формирователя сигналов управления подключены .к-входу сигнала Подтверждение захвата устройства для подключения к шине управления отлажива- емой микропроцессорной системы,второй выход дешифратора адресов соединен с третьим разрешающим входом формирователя сигналов управления и с разрешающим входом блока захвата шин, третий выход дешифратора адресов соединен с вторым информационным входом блока захвата шин, вход сбро5 са блока параллельного -интерфейса является входом сигнала Сброс устройства для подключения к шине управления отлаживаемой микропроцессорной системы, четвертый выход формирователя сигналов управления подключен к входу подтверждения блока обработки данных, второй и третий информационные входы формирователя сигналов управления подключены соответственно к выходам сигналов синхронизации и направления передачи блока обработки данных, четвертый, пятый, шестой и седьмой информациой- ные входы формирователя сигналов управления являются соответственно входами сигналов чтения из памяти, записи в память, чтения из порта ввода-вывода, запись в порт ввода- вывода устройства для подключения к шине управления отлаживаемой микропроцессорной системы, входы сигналов чтения из памяти, записи в память, чтения из порта ввода-выво0

0

5

0

5

да, запись в порт ввода-вывода уст- ройства подключены соответственно к первому, второму, третьему и четвертому входам уровней прерыйа- ния блока обработки данных, причем формирователь сигналов управления содержит три элемента НЕ, два элемента И-НЕ элемент ИЛИ-НЕ, элемент задержки, два элемента И, D-триггер и шинный формирователь, причем первый, второй и третий входы группы разрешающих входов формирователя сигналов управления подключены соответственно через первый элемент НЕ к первому входу первого элемента И, к второму входу первого элемента И и к входу признака двунаправленного обмена шинного формирователя, первый и второй разрешающие входы формирователя сигналов управления подключены Соответственно к первому и второму входам второго элемента И, выход которого соединен с входом признака однонаправленного обмена шинносигналов управления подключен к второму входу второго элемента И-НЕ и через третий элемент НЕ - к второму входу первого элемента И-НЕ, D-вход 5 D-триггера подключен к шине нулевого потенциала формирователя сигналов уп равления, а вход синхронизации D-три гера соединен с выходом элемента ЯПИ НЕ, выход первого элемента И соеди10 иен с S-входом D-триггера, выход которого подключен к п ервому выходу формирователя сигналов управления,с четвертого по седьмой информационные входы формирователя сигналов управt5 ления подключены к первому - четвертому входам элемента ИЛИ-НЕ, первый и второй входы-выходы шинного формирователя соединены с соответствующими входами элемента ИЛИ-НЕ и подклю20 чены соответственно к шестому и седьмому входам формирователя сигналов управления, первый и второй выходы шинного формирователя подключены соответственно к третьему и второму

го формирователя, третий разрешающий выходам формирователя сигналов уп-. вход формирователя сигналов управле- равления. ния подключен к

2. Устройство по п.1, отличающееся тем, что блок за- 30 хвата шин содержит элемент ИСКЛЮЧАЮЩЕЕ Или, элемент НЕ и элемент .И-НЕ,

третьему входу первого элемента И, первый информационный вход формирователя сигналов управления через элемент задержки подключен к четвертому выходу формирователя сигналов управления, второй информационный вход формирователя сигналов управления через второй элемент НЕ подклочен к четвертому входу первого элемента И и к первым входам первого и второго элементов И-НЕ, выходы которых подключены соответственно к второму и третьему выходам формирователя сигналов управления, третий информационный вход формирователя

выход которого является выходом блока захвата шин, первый, и второй ин- Аормационные входы блока захвата шин

35 подключены соответственно к первому и второму входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого через элемент НЕ соединен с первым входом элемента И-НЕ, второй вход которого подключен

40 к разрешающему входу блока захвата шин,

сигналов управления подключен к второму входу второго элемента И-НЕ и через третий элемент НЕ - к второму входу первого элемента И-НЕ, D-вход D-триггера подключен к шине нулевого потенциала формирователя сигналов управления, а вход синхронизации D-триггера соединен с выходом элемента ЯПИ- НЕ, выход первого элемента И соедииен с S-входом D-триггера, выход которого подключен к п ервому выходу формирователя сигналов управления,с четвертого по седьмой информационные входы формирователя сигналов управления подключены к первому - четвертому входам элемента ИЛИ-НЕ, первый и второй входы-выходы шинного формирователя соединены с соответствующими входами элемента ИЛИ-НЕ и подключены соответственно к шестому и седьмому входам формирователя сигналов управления, первый и второй выходы шинного формирователя подключены соответственно к третьему и второму

выходам формирователя сигналов уп-. равления.

выход которого является выходом блока захвата шин, первый, и второй ин- Аормационные входы блока захвата шин

35 подключены соответственно к первому и второму входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого через элемен НЕ соединен с первым входом элемента И-НЕ, второй вход которого подключен

40 к разрешающему входу блока захвата шин,

X Л

Qdpecoo

минроЭб

liaHctfl

MUflpO- J

ЭВМ

fi входам

fiSlS2) i UHmep- -| (рейса 8

li 8}(оди

BMi&f интер (рейсов I

ГГ6

ШУ(2)

M вмдап w

Pu.2

SSoff UHtpypftOffaL/ f .ам/гоЛв/ иг«

АОу Подпрограмма

11 обработка 1 сиенам ЗПЗУ

-Ж.

11 Подпрограмма П| обработки I сигнала ЗПВ8

Нет

Конец

отбавки

7

Программ1/роданиё, интврсрейсав

-Ч

oSMCH между каналами 8.7и8,3 Qmcymc/nBue захвата

Ожидание го/тюВнасти устройства сопряжение

Счить/Вание старшего байта адреса с 1 аналау

Программирование интердзейса 8

05мен между каналами 8,7и 8 }0тсутст&ие захва/па

Q)KnffaMie zo/noS/fOcmu устройства сопряжения

Считывание младшего J Sauma адреса с 1 анала 8.

CAOfKeiwe ВВеОснного адреса

С 5азо8ым адресом подпрограм ы

JL

npozpaMf i podciHue интерсрейсав

Нет

5ы8од Sou та В мккропрои(ессор чарез канал 8.6

СКонец Л

ы

Определение абсолютного адреса- Вводимых 8 микропроцессор даннь/л

Обмен между /каналами 8,3 и 8.6 Отсутствие захВата

Ожидание готовности устройства сопряжения

Восстанодление сигнала Г ТВ, снятого при вмЗе 8 под про.- paMMij.

Микропроцессор считывает оайт с WHufla 8.6 Lih fTiepcpeuca 8,

( Начало I

Программирова/н/е интерфейса 8

Счи ты Вани в старшего байта адреса с канала 7

т

Обмен между каналами

7 « .Отсутствие захВата

т

Ож14данме готоВносгтш устройства сопряжения

мшр мн нммямвип Лмпияммшмшяпшшмн

Программирование интерфейса в

Нет

Да

05мен каналами 5.7 W аз - Отсутствие зсгхВо/па

Считывание MAadufezo Saiima адреса с KaHaflaB

Сложение введенного адреса с базовым адресом подпрограммы

Програмщроданм интерфейса 8

Нет

а

Считывание Sauma Ввод1/мого из MHHpo/jpoueccopa, с канаста QS

( Конец)

Определение абсолютного адреса для размещения данныу оВодимыл из ,микропро14&:сора

-

Обмен межди 8 и вЗ Ошсутстбае захвата

Восстанд&ление сигнала Г ТВ, снятегго при Вмве о по&пао рамму. Данные J 6bt8eoeHHbte иикролроцессаром на ШИ считываются с канала 8 и Вводятся В памяпл Mui po9Bf по абсолютному адресу.

Фие.7

Г Начало

JL

Программирова ние интерфейса 8

Да

05мвн мвукди каналам HoAui ue здхоата Слу хе5ныи 5итА7 1

Ожидание готовности ycmpouicfrtBa сапрл 1 виир

Вывод старшего daUma адр9са / vei//ft/ noMflint г икропроцессора в канал 8.7

прЬграм ммроВание unmepcpei ca в

Да

Обмен между каналаии 83ti87

/fo/iwwe за)(ватс

С Аужебныы бит

Выдод младшвго Ьайтс . адреса ячейки памят(4 микропроцессора о канал 8.7

Программ1 родание интерфейса в

Да

Выводу 5аита для затеей В fi feuкu памяти микропро- и вссора в канал 8В

JT

СконвиЛ

между (аналам14 Haлt4 ife захвату Служебный 6итА7 0

Выдача сигнала ЗПЗУ устройством сопря иеныя по которому байт данные записыоается в ячей ни памяти микропроцессора из канала 8,0

Фиг. 8

(Ш)

I

Программирование антерфейсав

Обмен между каналами 53 и б№ Наличие sawama Служе5ныи ffu/n AT-J

Шыданив готовности уст- poifcmBa conpfffKEHUft

Вывод старшего Sciuma

адреса ячейки помята/ ми1{ропр014ессора в канал g7

Программирование ингперсрейса В

OifMeH межди каналани

ел W 5.7. . Наличие

J:лl/ кeбныu дитА 7 1

Вывод младмрго баи/па адреса ячейки памяти микропроцессора в канал 8,7

npozpaMni paoatiue интерсреиса 8

effod 5айта извлеченного из ячейки памяти микропроцессора через канал 8.6 с ЦД

i

(ко

Обмен каналами

аз t/ в,б

Наличие уакоата СлцжеКтт Sum

86/obrva сигнала ЧТЗУ устройством сопря ениЯу nQ которому 5айт QoHHbiX считывается из 1чейки памяти микро-- процессора через канал SJS м ШД

,У

ВНИИПИ Заказ 7526/51

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Тираж 670

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Устройство для связи микропроцессора с внешними устройствами | 1986 |

|

SU1372330A1 |

| Устройство для адресации памяти | 1990 |

|

SU1741142A1 |

| Устройство для формирования изображения | 1988 |

|

SU1575230A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Матричный распределитель | 1987 |

|

SU1580377A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для отладки программ | 1987 |

|

SU1425685A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

Устройство относится к цифровой вычислительной технике, в частности к средствам автоматизации контроля и поиска неисправностей микрсп процессорных систем, и может быть использовано для отладки аппаратных и программных средств цифровых систем управления с использованием микропроцессоров. Цель изобретения- упрощение устройства. Устройство соША О W с ю 00 СП || 00 IND

| Зеленко Г | |||

| Отладочный модул микроэвм | |||

| - Радио, 1983, № 4 | |||

| Устройство для обнаружения и локализации неисправностей цифровых блоков | 1982 |

|

SU1067507A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ,U | |||

Авторы

Даты

1987-01-23—Публикация

1985-02-13—Подача