Изобретение относится к вычислительной технике и может быть использовано для настройки отладки и проверки работы специализированных микроЭВМ, работающих в режиме реального масштаба времени и выполненных на секционированных микропроцессорных комплектах.

Цель изобретения - повышение быстродействия устройства.

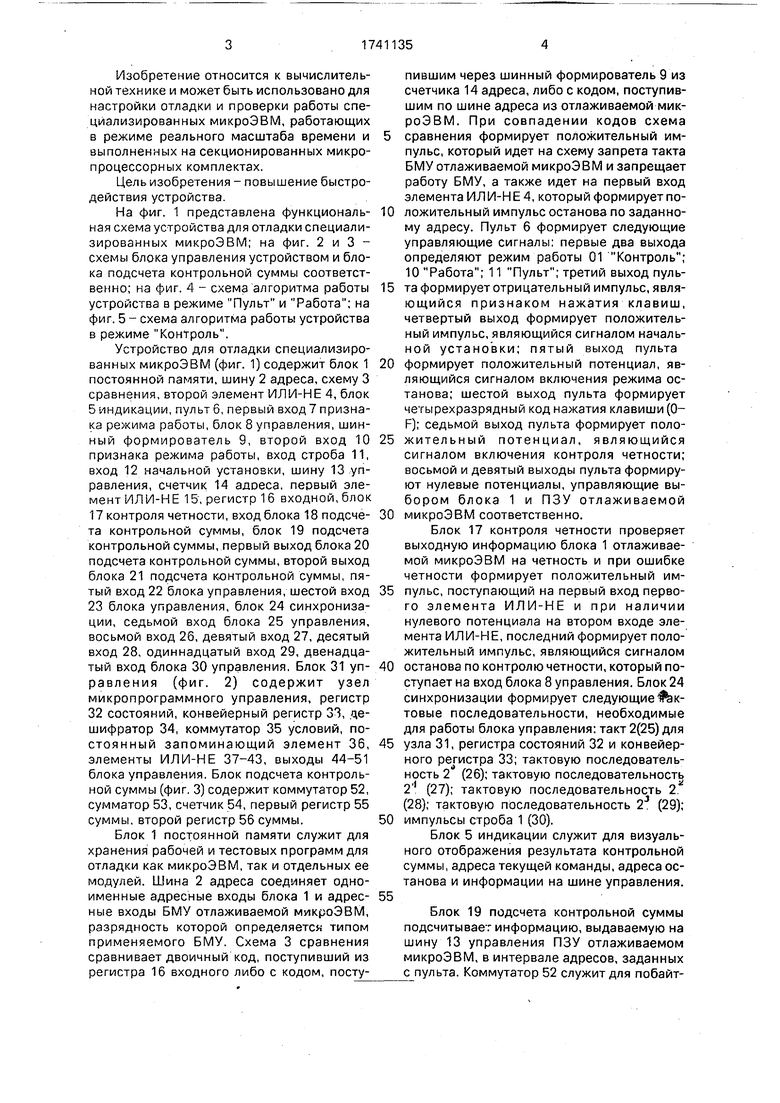

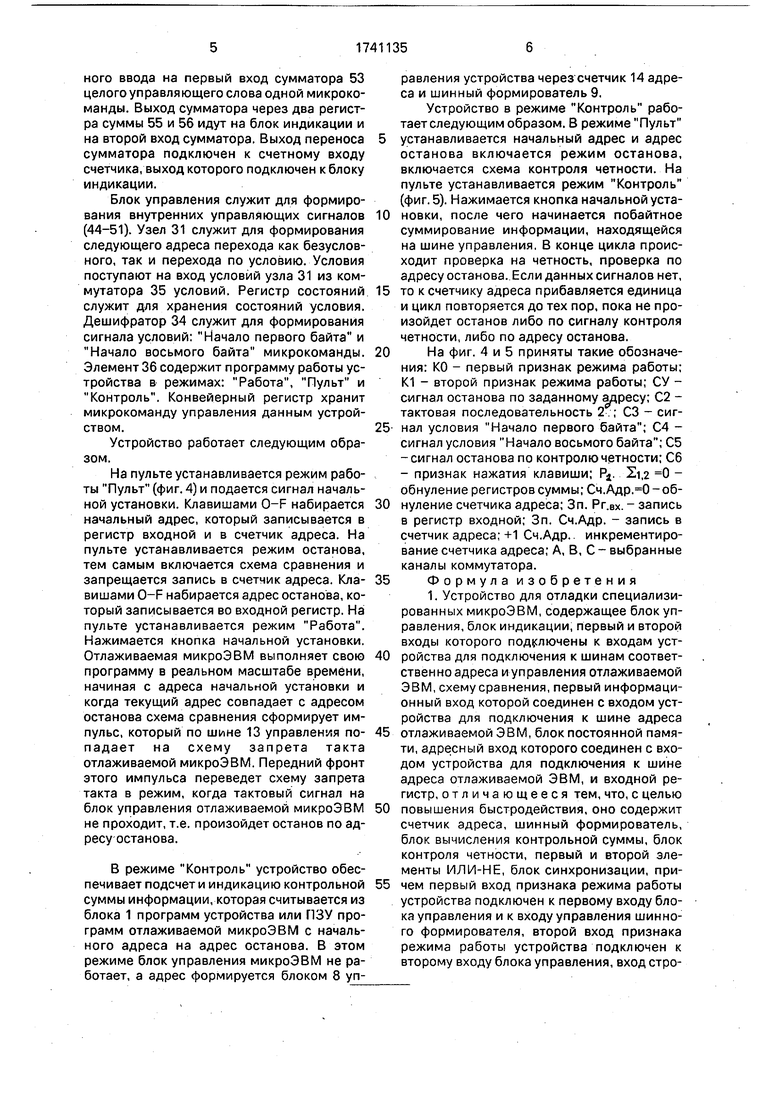

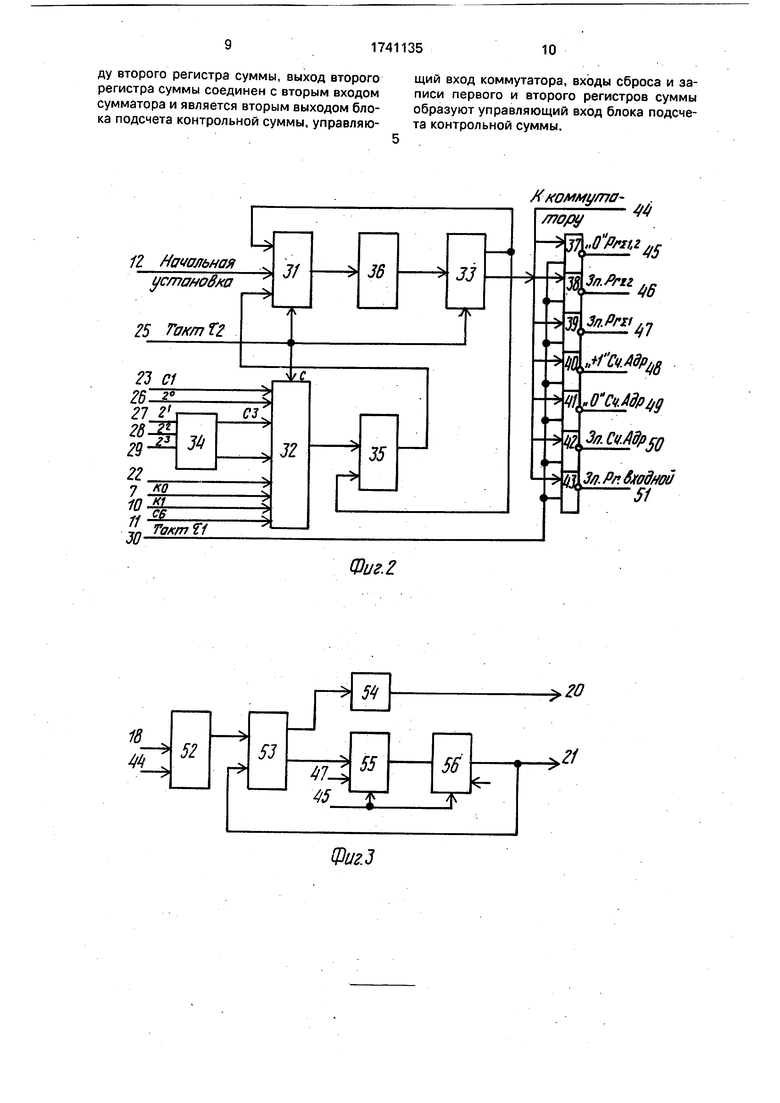

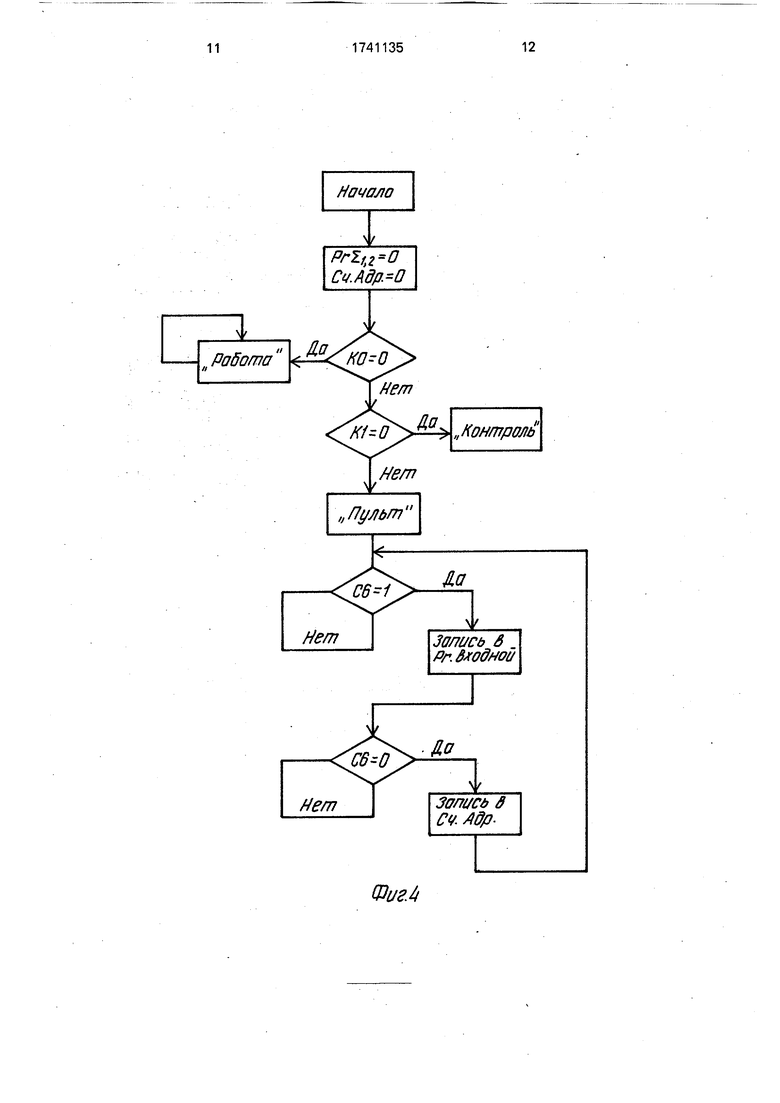

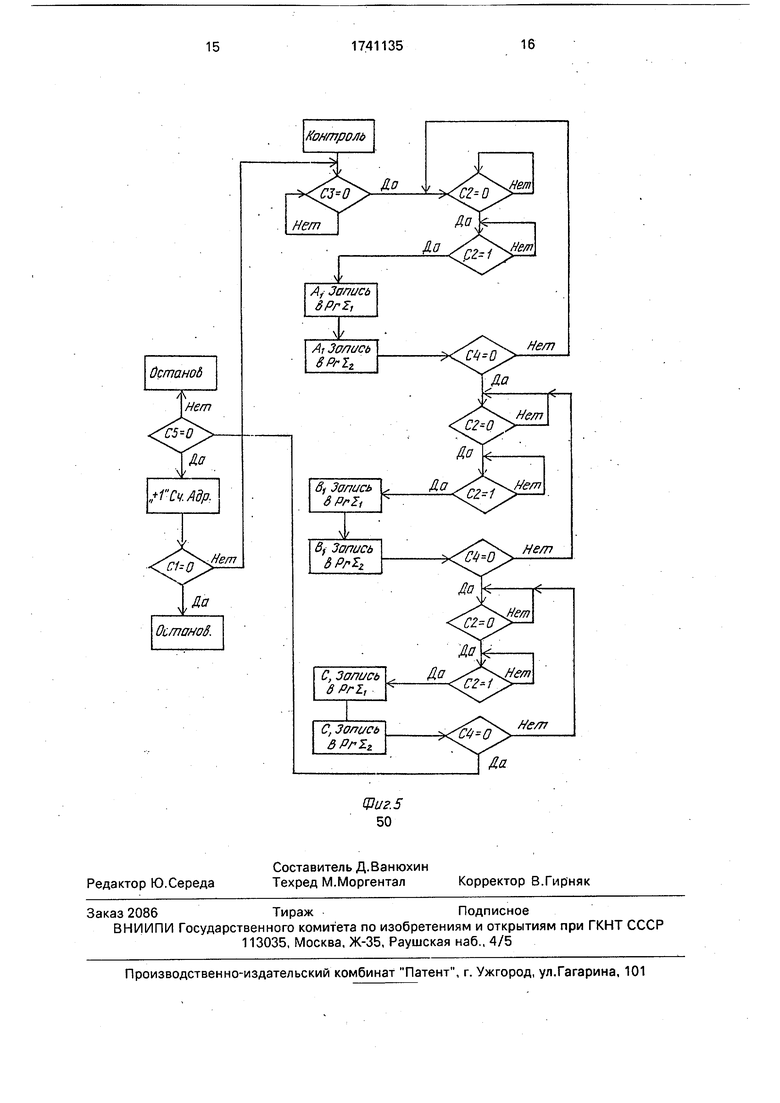

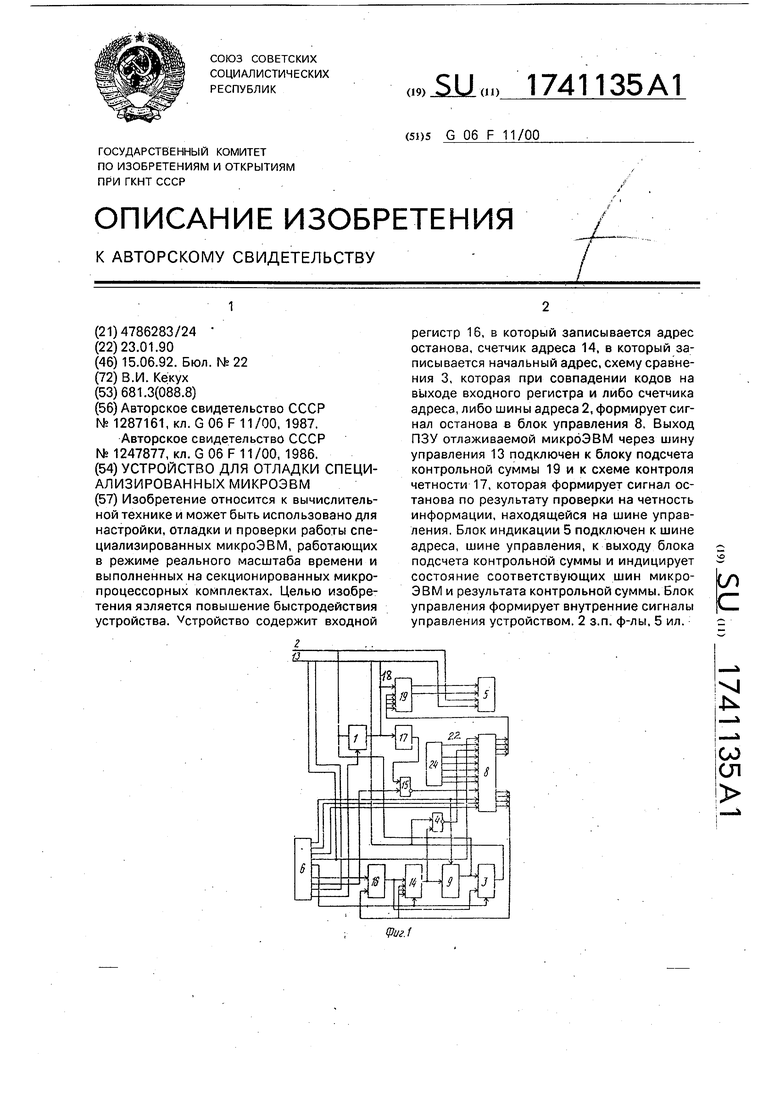

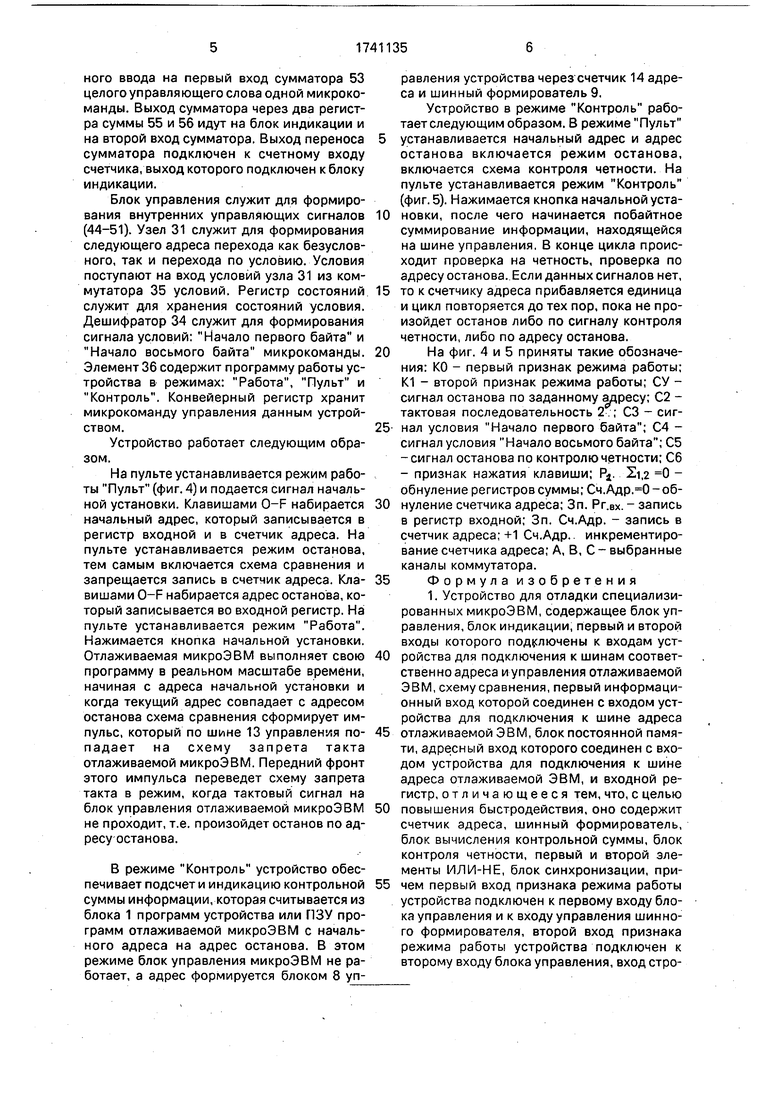

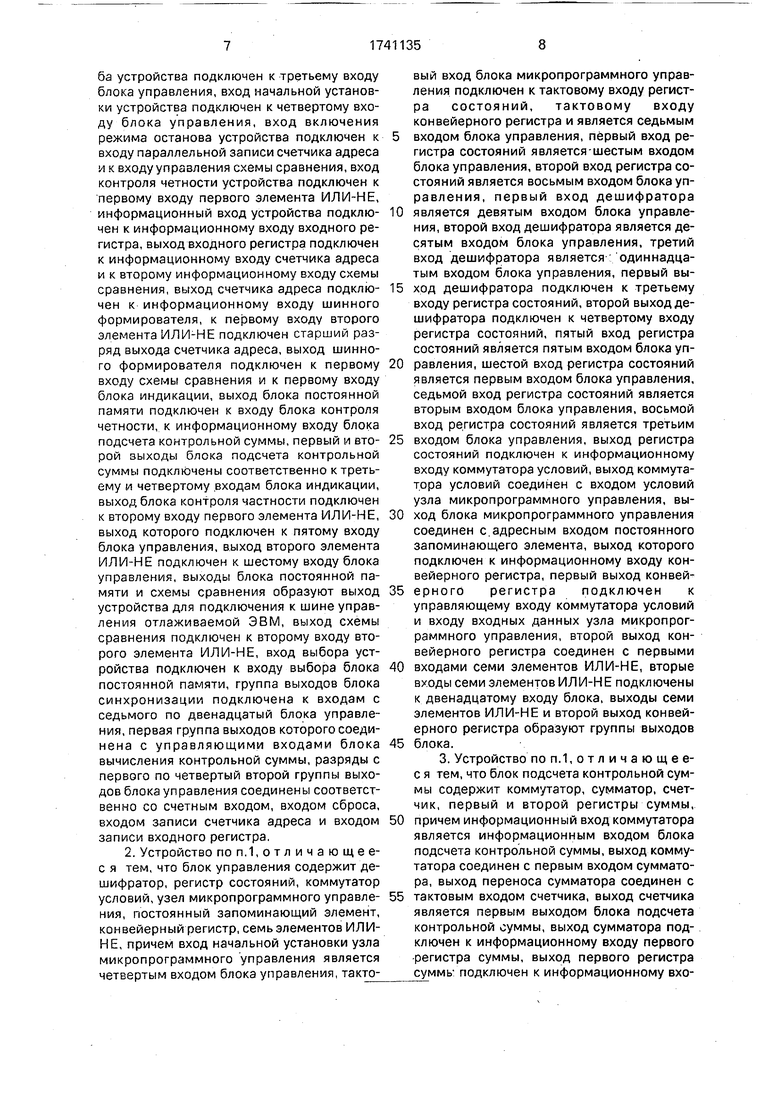

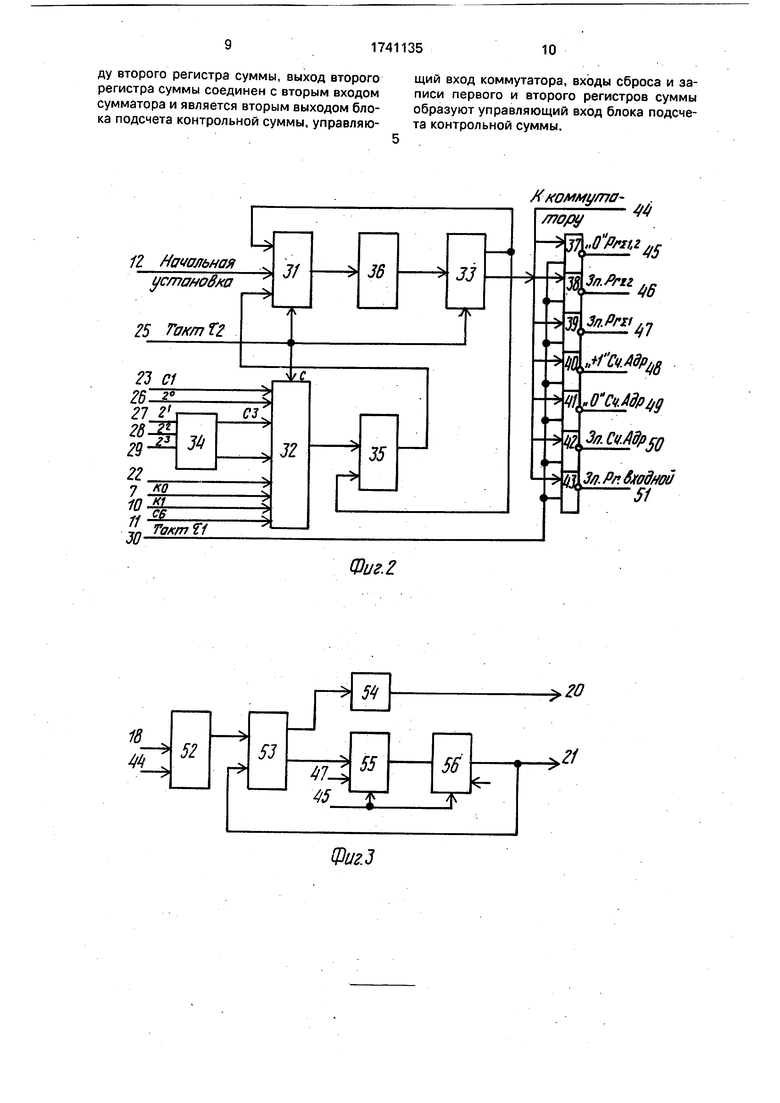

На фиг. 1 представлена функциональ- ная схема устройства для отладки специали- зированных микроЭВМ; на фиг. 2 и 3 - схемы блока управления устройством и блока подсчета контрольной суммы соответственно; на фиг. 4 - схема алгоритма работы устройства в режиме Пульт и Работа ; на фиг. 5 - схема алгоритма работы устройства в режиме Контроль.

Устройство для отладки специализированных микроЭВМ (фиг. 1) содержит блок 1 постоянной памяти, шину 2 адреса, схему 3 сравнения, второй элемент ИЛИ-НЕ 4, блок 5 индикации, пульт 6, первый вход 7 признака режима работы, блок 8 управления, шинный формирователь 9, второй вход 10 признака режима работы, вход строба 11, вход 12 начальной установки, шину 13 управления, счетчик 14 адоеса, первый элемент ИЛИ-НЕ 15,регистр 16 входной,блок 17 контроля четности, вход блока 18 подсче- та контрольной суммы, блок 19 подсчета контрольной суммы, первый выход блока 20 подсчета контрольной суммы, второй выход блока 21 подсчета контрольной суммы, пятый вход 22 блока управления, шестой вход 23 блока управления, блок 24 синхронизации, седьмой вход блока 25 управления, восьмой вход 26, девятый вход 27, десятый вход 28, одиннадцатый вход 29, двенадцатый вход блока 30 управления. Блок 31 уп- равления (фиг. 2) содержит узел микропрограммного управления, регистр 32 состояний, конвейерный регистр 33, дешифратор 34, коммутатор 35 условий, постоянный запоминающий элемент 36, элементы ИЛИ-НЕ 37-43, выходы 44-51 блока управления. Блок подсчета контрольной суммы (фиг. 3) содержит коммутатор 52, сумматор 53, счетчик 54, первый регистр 55 суммы, второй регистр 56 суммы.

Блок 1 постоянной памяти служит для хранения рабочей и тестовых программ для отладки как микроЭВМ, так и отдельных ее модулей. Шина 2 адреса соединяет одноименные адресные входы блока 1 и адрес- ные входы БМУ отлаживаемой микроЭВМ, разрядность которой определяется типом применяемого БМУ. Схема 3 сравнения сравнивает двоичный код, поступивший из регистра 16 входного либо с кодом, поступившим через шинный формирователь 9 из счетчика 14 адреса, либо с кодом, поступившим по шине адреса из отлаживаемой микроэвм. При совпадении кодов схема сравнения формирует положительный импульс, который идет на схему запрета такта БМУ отлаживаемой микроЭВМ и запрещает работу БМУ, а также идет на первый вход элемента ИЛ И-Н Е 4, который формирует положительный импульс останова по заданному адресу. Пульт 6 формирует следующие управляющие сигналы: первые два выхода определяют режим работы 01 Контроль ; 10 Работа ; 11 Пульт ; третий выход пульта формирует отрицательный импульс, явля- ющийся признаком нажатия клавиш, четвертый выход формирует положительный импульс, являющийся сигналом начальной установки; пятый выход пульта формирует положительный потенциал, являющийся сигналом включения режима останова; шестой выход пульта формирует четырехразрядный код нажатия клавиши (0- F); седьмой выход пульта формирует положительный потенциал, являющийся сигналом включения контроля четности; восьмой и девятый выходы пульта формируют нулевые потенциалы, управляющие выбором блока 1 и ПЗУ отлаживаемой микроЭВМ соответственно.

Блок 17 контроля четности проверяет выходную информацию блока 1 отлаживаемой микроЭВМ на четность и при ошибке четности формирует положительный импульс, поступающий на первый вход первого элемента ИЛИ-НЕ и при наличии нулевого потенциала на втором входе элемента ИЛИ-НЕ, последний формирует положительный импульс, являющийся сигналом останова по контролю четности, который поступает на вход блока 8 управления. Блок 24 синхронизации формирует следующие Актовые последовательности, необходимые для работы блока управления: такт 2(25) для узла 31, регистра состояний 32 и конвейерного регистра 33; тактовую последовательность 2 (26); тактовую последовательность 21 (27); тактовую последовательность 2 (28); тактовую последовательность 23 (29); импульсы строба 1 (30).

Блок 5 индикации служит для визуального отображения результата контрольной суммы, адреса текущей команды, адреса останова и информации на шине управления.

Блок 19 подсчета контрольной суммы подсчитывает информацию, выдаваемую на шину 13 управления ПЗУ отлаживаемом микроЭВМ, в интервале адресов, заданных с пульта. Коммутатор 52 служит для побайтного ввода на первый вход сумматора 53 целого управляющего слова одной микрокоманды. Выход сумматора через два регистра суммы 55 и 56 идут на блок индикации и на второй вход сумматора. Выход переноса сумматора подключен к счетному входу счетчика, выход которого подключен к блоку индикации.

Блок управления служит для формирования внутренних управляющих сигналов (44-51). Узел 31 служит для формирования следующего адреса перехода как безусловного, так и перехода по условию. Условия поступают на вход условий узла 31 из коммутатора 35 условий. Регистр состояний служит для хранения состояний условия. Дешифратор 34 служит для формирования сигнала условий: Начало первого байта и Начало восьмого байта микрокоманды. Элемент 36 содержит программу работы устройства в режимах: Работа, Пульт и Контроль. Конвейерный регистр хранит микрокоманду управления данным устройством.

Устройство работает следующим образом.

На пульте устанавливается режим работы Пульт (фиг. 4) и подается сигнал начальной установки. Клавишами 0-F набирается начальный адрес, который записывается в регистр входной и в счетчик адреса. На пульте устанавливается режим останова, тем самым включается схема сравнения и запрещается запись в счетчик адреса. Кла- вишами 0-F набирается адрес останова, который записывается во входной регистр. На пульте устанавливается режим Работа. Нажимается кнопка начальной установки. Отлаживаемая микроЭВМ выполняет свою программу в реальном масштабе времени, начиная с адреса начальной установки и когда текущий адрес совпадает с адресом останова схема сравнения сформирует импульс, который по шине 13 управления по- падает на схему запрета такта отлаживаемой микроЭВМ. Передний фронт этого импульса переведет схему запрета такта в режим, когда тактовый сигнал на блок управления отлаживаемой микроЭВМ не проходит, т.е. произойдет останов по адресу останова.

В режиме Контроль устройство обеспечивает подсчет и индикацию контрольной суммы информации, которая считывается из блока 1 программ устройства или ПЗУ программ отлаживаемой микроЭВМ с начального адреса на адрес останова. В этом режиме блок управления микроЭВМ не работает, а адрес формируется блоком 8 управления устройства через счетчик 14 адреса и шинный формирователь 9.

Устройство в режиме Контроль работает следующим образом. В режиме Пульт устанавливается начальный адрес и адрес останова включается режим останова, включается схема контроля четности. На пульте устанавливается режим Контроль (фиг. 5). Нажимается кнопка начальной установки, после чего начинается побайтное суммирование информации, находящейся на шине управления. В конце цикла происходит проверка на четность, проверка по адресу останова. Если данных сигналов нет, то к счетчику адреса прибавляется единица и цикл повторяется до тех пор, пока не произойдет останов либо по сигналу контроля четности, либо по адресу останова.

На фиг. 4 и 5 приняты такие обозначения: КО - первый признак режима работы; К1 - второй признак режима работы; СУ - сигнал останова по заданному адресу; С2 - тактовая последовательность 2 ; СЗ - сигнал условия Начало первого байта ; С4 - сигнал условия Начало восьмото байта ; С5 -сигнал останова по контролю четности; С6 - признак нажатия клавиши; Р4. Zi,2 0 - обнуление регистров суммы; Сч,Адр.0-обнуление счетчика адреса; Зп. Рг.вх. - запись в регистр входной; Зп. Сч.Адр. - запись в счетчик адреса; +1 Сч.Адр. инкрементиро- вание счетчика адреса; А, В, С - выбранные каналы коммутатора.

Формула изобретения

1. Устройство для отладки специализированных микроЭВМ, содержащее блок управления, блок индикации, первый и второй входы которого подключены к входам устройства для подключения к шинам соответственно адреса и управления отлаживаемой ЭВМ, схему сравнения, первый информационный вход которой соединен с входом устройства для подключения к шине адреса отлаживаемой ЭВМ, блок постоянной памяти, адресный вход которого соединен с входом устройства для подключения к шине адреса отлаживаемой ЭВМ, и входной регистр, отличающееся тем, что, с целью повышения быстродействия, оно содержит счетчик адреса, шинный формирователь, блок вычисления контрольной суммы, блок контроля четности, первый и второй элементы ИЛИ-НЕ, блок синхронизации, причем первый вход признака режима работы устройства подключен к первому входу блока управления и к входу управления шинного формирователя, второй вход признака режима работы устройства подключен к второму входу блока управления, вход строба устройства подключен к третьему входу блока управления, вход начальной установки устройства подключен к четвертому входу блока управления, вход включения режима останова устройства подключен к входу параллельной записи счетчика адреса и к входу управления схемы сравнения, вход контроля четности устройства подключен к первому входу первого элемента ИЛИ-НЕ, информационный вход устройства подклю- чен к информационному входу входного регистра, выход входного регистра подключен к информационному входу счетчика адреса и к второму информационному входу схемы сравнения, выход счетчика адреса подклю- чен к информационному входу шинного формирователя, к первому входу второго элемента ИЛИ-НЕ подключен старший разряд выхода счетчика адреса, выход шинного формирователя подключен к первому входу схемы сравнения и к первому входу блока индикации, выход блока постоянной памяти подключен к входу блока контроля четности, к информационному входу блока подсчета контрольной суммы, первый и вто- рой выходы блока подсчета контрольной суммы подключены соответственно к третьему и четвертому входам блока индикации, выход блока контроля частности подключен к второму входу первого элемента ИЛИ-НЕ, выход которого подключен к пятому входу блока управления, выход второго элемента ИЛИ-НЕ подключен к шестому входу блока управления, выходы блока постоянной памяти и схемы сравнения образуют выход устройства для подключения к шине управления отлаживаемой ЭВМ, выход схемы сравнения подключен к второму входу второго элемента ИЛИ-НЕ, вход выбора устройства подключен к входу выбора блока постоянной памяти, группа выходов блока синхронизации подключена к входам с седьмого по двенадцатый блока управления, первая группа выходов которого соединена с управляющими входами блока вычисления контрольной суммы, разряды с первого по четвертый второй группы выходов блока управления соединены соответственно со счетным входом, входом сброса, входом записи счетчика адреса и входом записи входного регистра.

2. Устройство поп.Ч.отличающее- с я тем, что блок управления содержит дешифратор, регистр состояний, коммутатор условий, узел микропрограммного управле- ния, постоянный запоминающий элемент, конвейерный регистр, семь элементов ИЛИ- НЕ, причем вход начальной установки узла микропрограммного управления является четвертым входом блока управления, та кто-

вый вход блока микропрограммного управления подключен к тактовому входу регистра состояний, тактовому входу конвейерного регистра и является седьмым входом блока управления, первый вход регистра состояний является-шестым входом блока управления, второй вход регистра состояний является восьмым входом блока управления, первый вход дешифратора является девятым входом блока управления, второй вход дешифратора является десятым входом блока управления, третий вход дешифратора является одиннадцатым входом блока управления, первый выход дешифратора подключен к третьему входу регистра состояний, второй выход дешифратора подключен к четвертому входу регистра состояний, пятый вход регистра состояний является пятым входом блока управления, шестой вход регистра состояний является первым входом блока управления, седьмой вход регистра состояний является вторым входом блока управления, восьмой вход регистра состояний является третьим входом блока управления, выход регистра состояний подключен к информационному входу коммутатора условий, выход коммутатора условий соединен с входом условий узла микропрограммного управления, выход блока микропрограммного управления соединен с адресным входом постоянного запоминающего элемента, выход которого подключен к информационному входу конвейерного регистра, первый выход конвейерного регистра подключен к управляющему входу коммутатора условий и входу входных данных узла микропрограммного управления, второй выход конвейерного регистра соединен с первыми входами семи элементов ИЛИ-НЕ, вторые входы семи элементов ИЛИ-НЕ подключены к двенадцатому входу блока, выходы семи элементов ИЛИ-НЕ и второй выход конвейерного регистра образуют группы выходов блока.

3. Устройство поп.1,отличающее- с я тем, что блок подсчета контрольной суммы содержит коммутатор, сумматор, счетчик, первый и второй регистры суммы, причем информационный вход коммутатора является информационным входом блока подсчета контрольной суммы, выход коммутатора соединен с первым входом сумматора, выход переноса сумматора соединен с тактовым входом счетчика, выход счетчика является первым выходом блока подсчета контрольной суммы, выход сумматора подключен к информационному входу первого регистра суммы, выход первого регистра суммь- подключен к информационному входу второго регистра суммы, выход второго регистра суммы соединен с вторым входом сумматора и является вторым выходом блока подсчета контрольной суммы, управляющий вход коммутатора, входы сброса и записи первого и второго регистров суммы образуют управляющий вход блока подсчета контрольной суммы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1996 |

|

RU2110833C1 |

| Устройство для отладки микроЭВМ | 1989 |

|

SU1677708A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1587514A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Имитатор канала | 1991 |

|

SU1839250A2 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

Фиг.З

ХкоммутаФиг.2

Залась 6 РГ. Входной

№

Фм.4

Нет

Авторы

Даты

1992-06-15—Публикация

1990-01-23—Подача