Игобретение относится к вычисли- телы ой технике и может быть исполь- о для проверки микропрограммных устрсйств управления и их отладки.

Целью изобретения является повышение достоверности контроля.

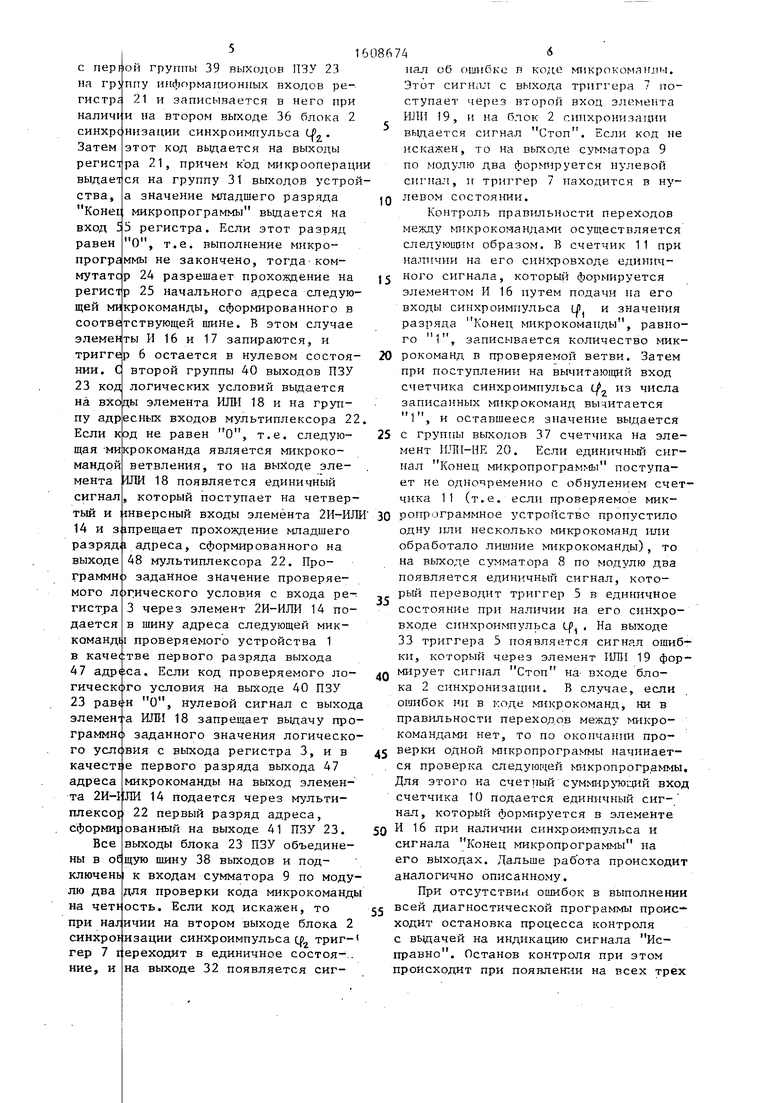

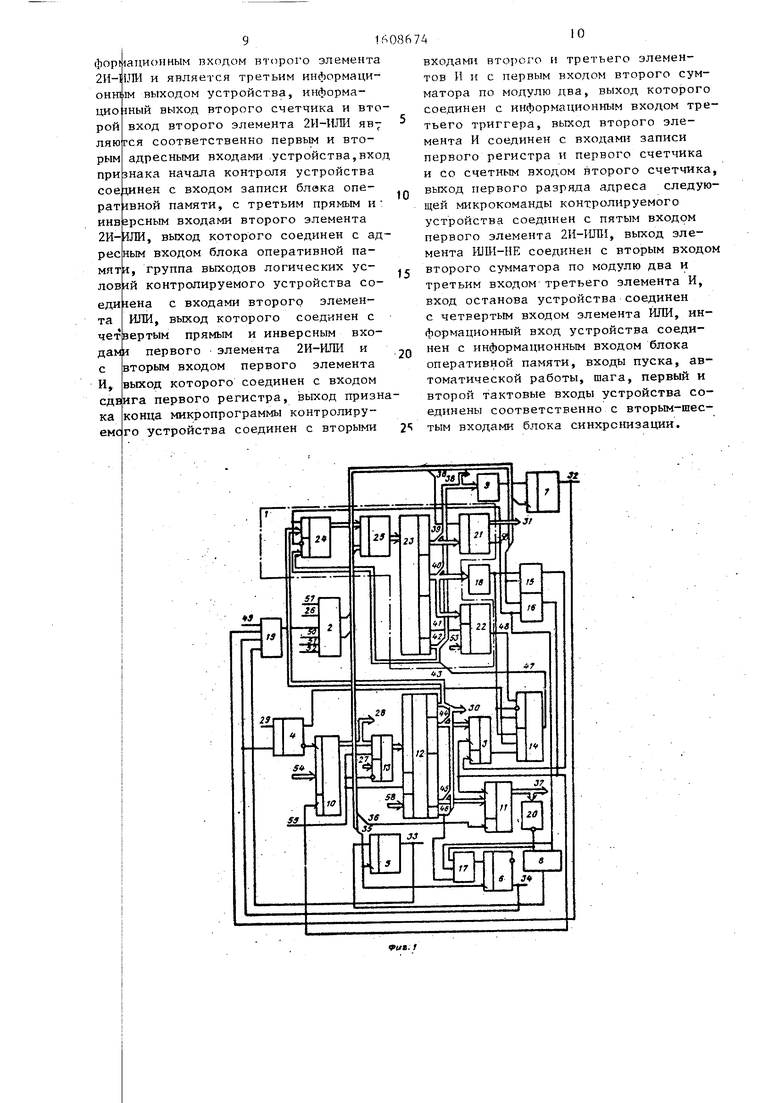

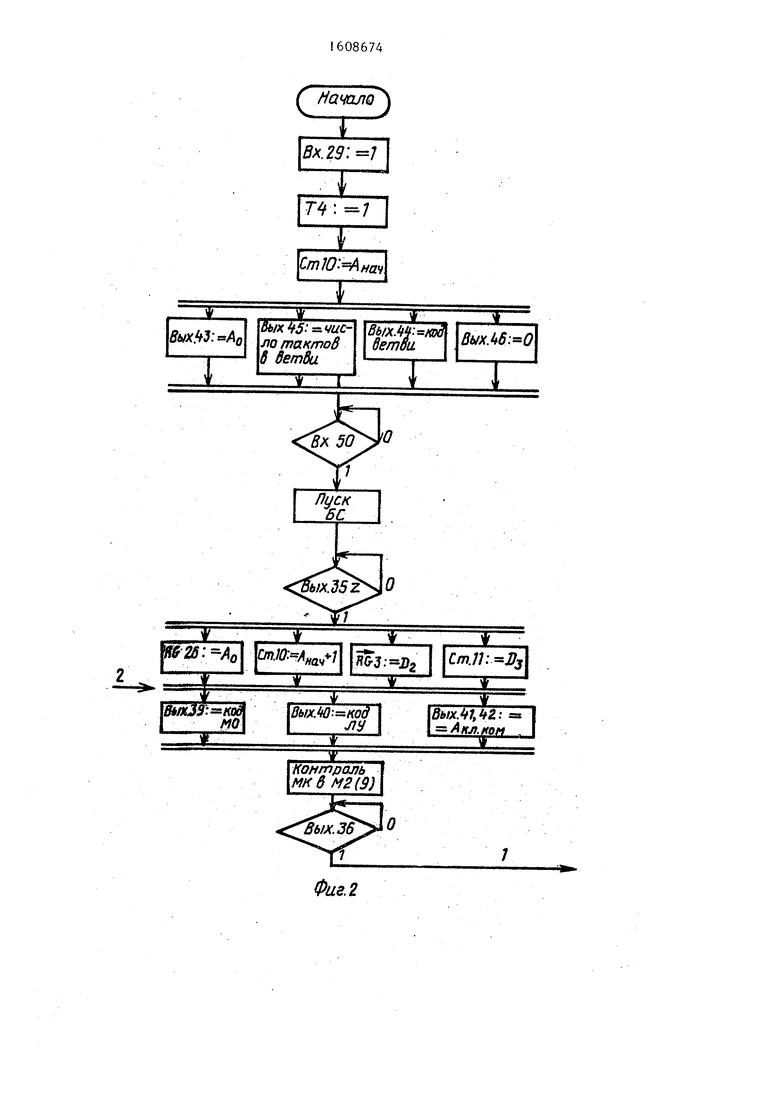

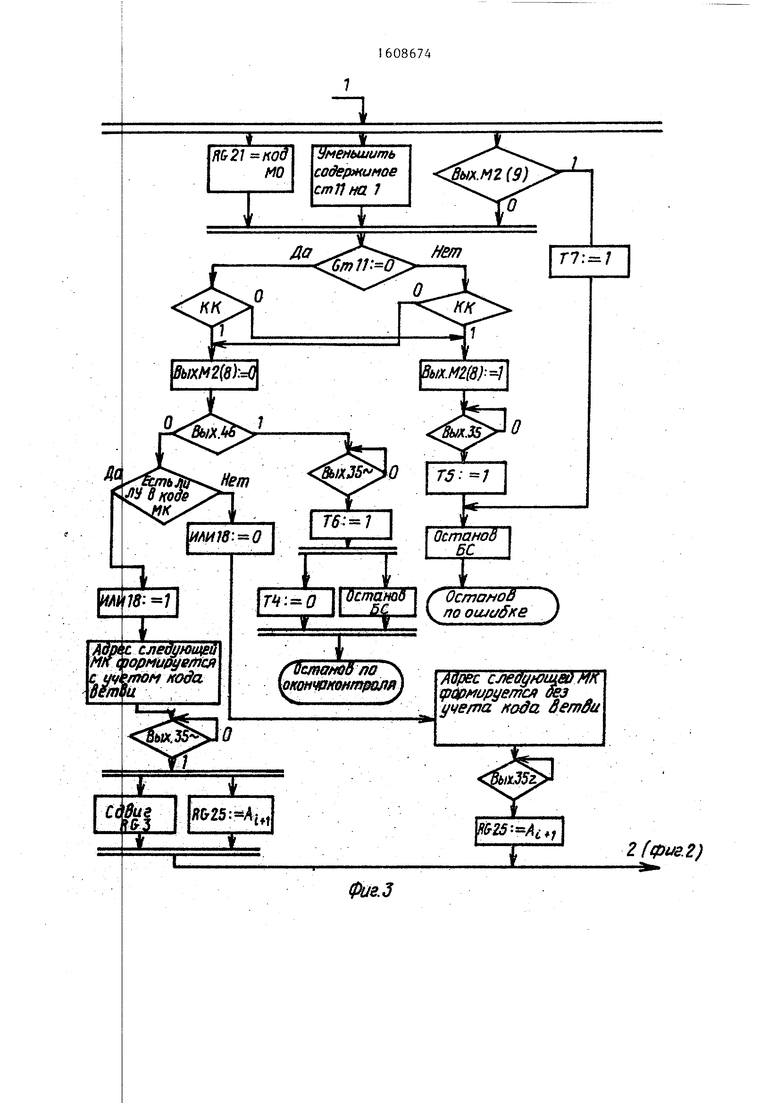

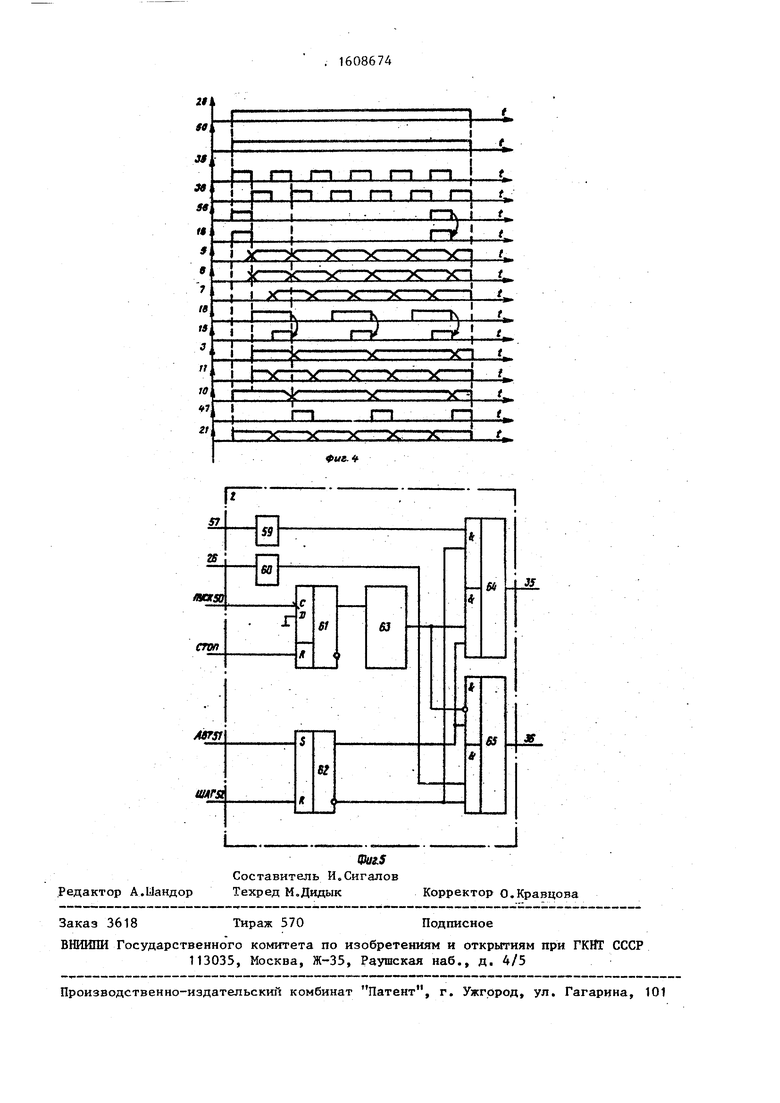

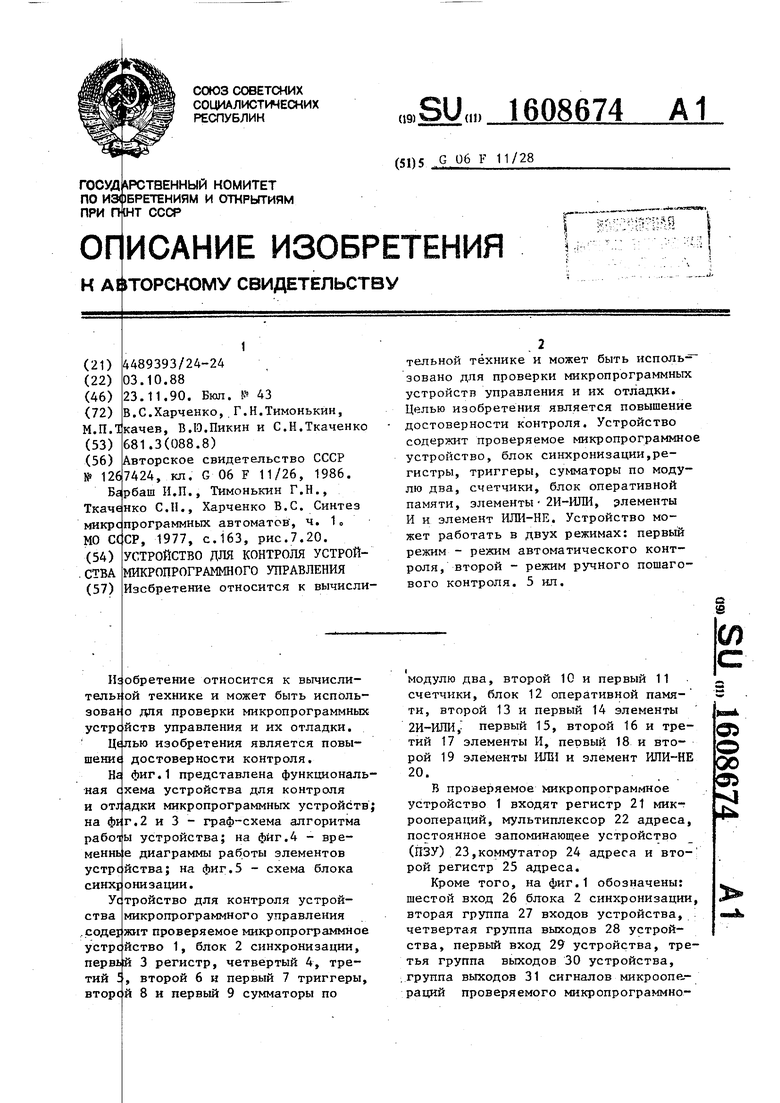

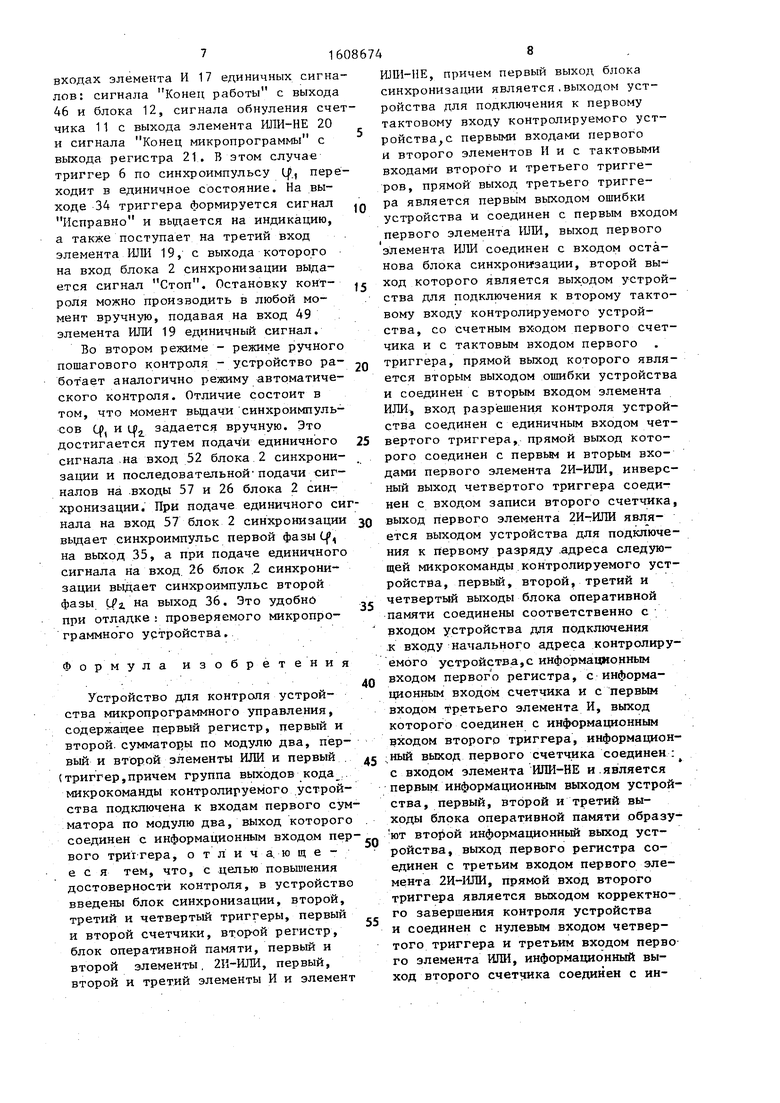

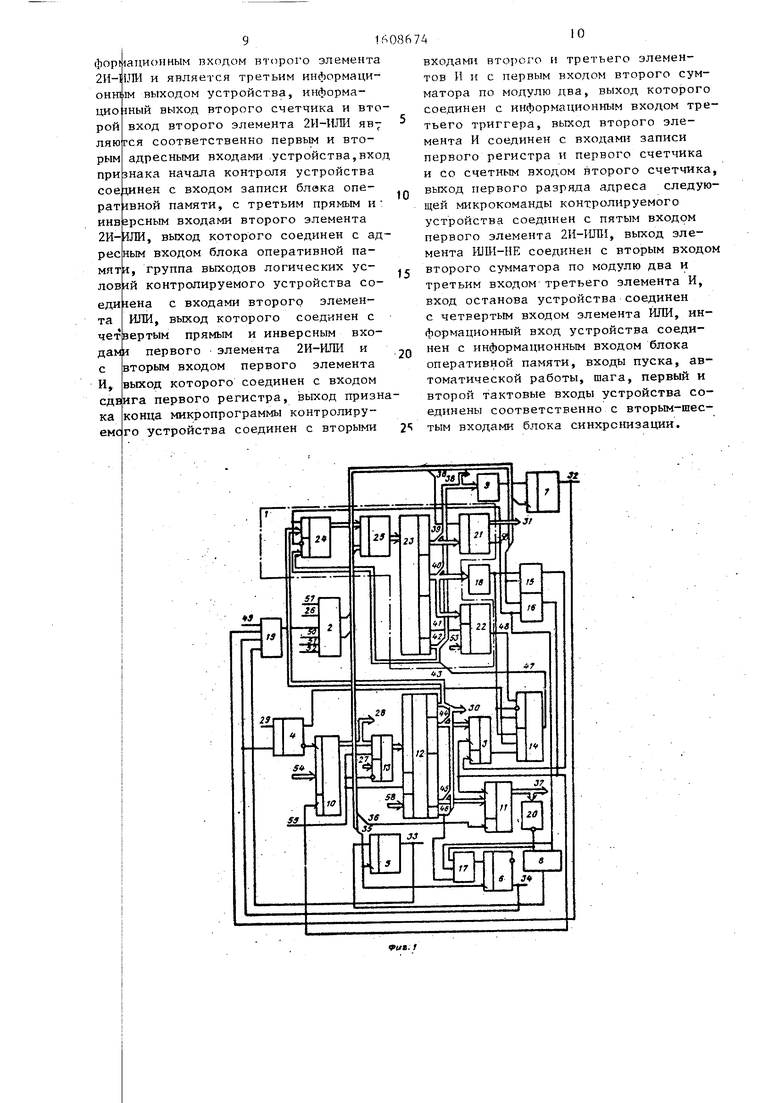

Иг фиг.1 представлена функциональ- ная схема устройства для контроля и отладки микропрограммных устройств; на ф1:г.2 и 3 - граф-схема алгоритма работы устройства; на фиг.4 - вре- меннь е диаграммы работы элементов устройства; на фиг.5 - схема блока cHHXj онизации.

Ус тройство для контроля устройства микропрограммного управления .содержит проверяемое микропрограммное устройство 1, блок 2 синхронизации, первьй 3 регистр, четвертый 4, третий , второй 6 и первый 7 триггеры, вторе и 8 и первый 9 сумматоры по

модулю два, второй 10 и первый 11 счетчики, блок 12 оперативной памяти, второй 13 и первый 14 элементы 2И-ИЛИ,- первый 15, второй 16 и третий 17 элементы И, первый 18 и второй 19 элементы ИЛИ и элемент ИЛИ-НЕ 20.

В проверяемое микропрограммное устройство 1 входят регистр 21 мик-г роопераций, мультиплексор 22 адреса, постоянное запоминающее устройство (ПЗУ) 23,коммутатор 24 адреса и вто- рой регистр 25 адреса.

Кроме того, на фиг.1 обозначены: шестой вход 26 блока 2 синхронизации, вторая группа 27 входов устройства, четвертая группа выходов 28 устройства, первый вход 29 устройства, третья группа выходов 30 устройства, .группа выходов 31 сигналов микроопе.- раций проверяемого микропрограммно

о

00

о hf

10

с нулями во всех разрядах, кроме разряда Конец микропрограммы, который равен 1. Кроме того, 1 равен разряд проверки на четность микрокоманды.

На вход 54 счетчика 10 подается начальный адрес диагностической программы.

На вход 29 подается единичный сигнал, что соответствует разрешению контроля. Вследствие этого триггер 4 переходит в единичное состояние и в счетчике 10 записывается начальный адрес диагностической программы, так как на синхровход счетчика подается единичный сигнал. Начальный адрес со счетчика 10 через элемент 2И-ИЛИ 13 подается на адресные входы блока 12. С первой группы 43 выходов блока 12 считывается начальный адрес проверяемой микропрограммы, который поступает на проверяемое устройство. По второй группе проверяемого устройства 1, седь-25 44 выходов блока 12 вьщается набор

J5

20

31608674

го устройства, второй 32 и первый 33 выходы ошибки устройства, выход 34 нормального завершения контроля устройства, первый 35 и второй 36 выходы блока 2 синхронизации, вторая 37 и первая 38 группы выходов устройства, выходы 39 и 40 соответственно поля микроопераций и поля логических условий ПЗУ, выходы 41 и 42 соответственно первого и последующих разрядов поля адреса ПЗУ, первая 43, вторая 44 и третья 45 группы выходоэ блока 12, управляющий выход 46, выход 47 первого элемента И-ИЛИ 14, выход 48 мультиплексора 22 адреса, второй вход 49 устройства, четвертый 50, пятый 51 и шестой 52 входы устройства, группа входов 53 сигналов логических условий провёряемо- .го микропрограммного устройства, первая группа восьми входов 54 устройства, третий вход 55 устройства, выход 56 сигнала Конец микропрограммы

мой вход 57 устройства, третья группа входов 58 устройства.

Блок 2 синхронизации (фиг.5) содержит .первый 59 и второй 60 одно- вибраторы, первый 61 и второй 62 триггеры, генератор 63, первый 64 и второй 65 элементы И-ИЛИ.

Устройство может работать в двух режимах: первый - режим автоматического контроля, второй - режим ручного пошагового контроля. Режимы работы задаются е помощью подачи единичного сигнала на входы 51 «ли 52 соответственно (Авт. или Шаг). Перед началом контроля в блок 12 через вход 58 элемент 2И-ИЛИ 13 загружают тестовую программу. Адреса ее команд формируются на группе 27 входов элемента И-ИЛИ 13,oднoвpe- вpeмeнкo на вход 55 режима работы блока 12 подается нулевой сигнал, который переводит блок 12 в режим Запись. После загрузки тестовой программы, на вход 55 подается единичный сигнал, и устройство оказьгоает- ся готовым к проведению контроля.

Работа устройства в первом режиме автоматического контроля.

В исходном состоянии генератор синхроимпульсов в блоке 2 синхронизации отключен, первый 7, второй 6, третий 5 и четвертый 4 триггеры находятся в нулевом состоянии, в регистре 21 записан код микроопераций

30

35

40

45

50

55

значений логических условий в виде кода для проверяемой ветви микропрограммы. По третьей группе 45 выходов блока 12 вьщается код числа микрокоманд ветви. Значение сигнала на выходе 46 зависит от того, заканчивается на проверке этой ветви контроль микропрограммного устройства или нет. Если контроль закончен, значение выхода 46 равно 1, если нет - О.

Далее на входы 50 и 51 блока 2 синхронизации подаются сигналы Пус к и Авт.. По э ТИМ сигналам запускается генератор 63 блока 2 синхронизации, который ввдает двух- фазную последовательность синхроимпульсов. На первый выход 35 блока 2 синхронизации вьщается последовательность синхроимпульсов первой фазы (С,, а на второй выход - последовательность синхроимпульсов второй фазы - Рз атывание элементов схемы происходит по заднему фронту (спаду) синхроимпульсов. При наличии на первом выходе 35 блока 2 синхро- 1шзации синзсроимпульса Cf. в регистр 25 через группу информационных входов записывается код начального адреса проверяемой микропрограммы. Он .передается на входы ПЗУ 23, которое по данному адресу схштывает первую микрокоманду и вцдает ее на-свои выходы. Код микроопераций поступает

0

5

0

5

0

5

значений логических условий в виде кода для проверяемой ветви микропрограммы. По третьей группе 45 выходов блока 12 вьщается код числа микрокоманд ветви. Значение сигнала на выходе 46 зависит от того, заканчивается на проверке этой ветви контроль микропрограммного устройства или нет. Если контроль закончен, значение выхода 46 равно 1, если нет - О.

Далее на входы 50 и 51 блока 2 синхронизации подаются сигналы Пус к и Авт.. По э ТИМ сигналам запускается генератор 63 блока 2 синхронизации, который ввдает двух- фазную последовательность синхроимпульсов. На первый выход 35 блока 2 синхронизации вьщается последовательность синхроимпульсов первой фазы (С,, а на второй выход - последовательность синхроимпульсов второй фазы - Рз атывание элементов схемы происходит по заднему фронту (спаду) синхроимпульсов. При наличии на первом выходе 35 блока 2 синхро- 1шзации синзсроимпульса Cf. в регистр 25 через группу информационных входов записывается код начального адреса проверяемой микропрограммы. Он .передается на входы ПЗУ 23, которое по данному адресу схштывает первую микрокоманду и вцдает ее на-свои выходы. Код микроопераций поступает

с перпой группы 39 выходов ПЗУ 23 на rpjnny информационных входов ре- гистр 21 и записывается в него при налич - и на втором выходе 36 блока 2 синхрс низации синхроимпульса (J .

Затем

этот код вьщается на выходы

регистра 21, причем код микрооперадии выдается на группу 31 выходов устройства, Конег вход 5

равен О, т.е. выполнение микропрограммы не закончено, тогда ком- мутатср 24 разрешает прохождение на регистр 25 начального адреса следующей микрокоманды, сформированного в соответствующей шине. В этом случае элементы И 16 и 17 запираются, и триггер 6 остается в нулевом состоянии. С второй группы 40 выходов ПЗУ 23 код логических условий выдается на вхоцы элемента ИЛИ 18 и на группу адресных входов мультиплексора 22, Если код не равен О, т.е. следующая Микрокоманда является микроко- ветвления, то на выХоде элеВсе

ние, и

а значение мдадшего разряда

микропрограммы выдается на 5 регистра. Если этот разряд

ШИ 18 появляется единичный

, который поступает на четвершвероный входы элемента 2И-ИЛИ 30 ропрограммное устройство пропустило

шрещает прохождение младшего

мандой мента сигнал тый и 14 и 3

разряд. 1 адреса, сформированного на выходе 48 мультиплексора 22. Программно заданное значение проверяемого лог.ического условия с входа регистра 3 через элемент 2И-ИЛИ 14 подается в шину адреса следующей мик- командп проверяемого устройства 1 в качестве первого разряда выхода 47 адреса. Если код проверяемого логического условия на выходе 40 ПЗУ 23 О, нулевой сигнал с выхода элемен а Р1П11 18 запрещает выдачу программно заданного значения логического УСЛС1ВИЯ с вькода регистра 3, и в качест е первого разряда выхода 47 адреса микрокоманды на выход элемента 2И-ГЛИ 14 подается через мультиплексор 22 первый разряд адреса, сформированный на выходе 41 ПЗУ 23.

jQ левом состоянии.

Контроль правильности переходов между микрокомандам осуществляется следуюиогм образом. В счетчик 1 1 при наличии на его синхровходе единичj ного сигнала, которьв формируется элементом И 16 путем подачи на его входы синхроимпульса Ц) и значения разряда Конед микрокоманды, равно го 1, записывается количество мик20 рокоманд в проверяемой ветви. Затем при поступлении на вычитающий вход счетчика синхроимпульса t/, из числа записанных микрокоманд вычитается 1, и оставшееся значение выдается

25 с группы выходов 37 счетчика на элемент ИЛИ-НЕ 20. Если единичньй сигнал Конед микропрограммы поступает не одновременно с обнулением счет чика 11 (т.е. если проверяемое мик35

40

выходы блока 23 ПЗУ объединены в оещую шину 38 выходов и под- ключень к входам сумматора 9 по модулю два для проверки кода микрокоманды на четюсть. Если код искажен, то при нахичии на втором выходе блока 2 синхронизации синхроимпульса ср триг- гер 7 гереходит в единичное состоя--.

на выходе 32 появляется сигодну или несколько микрокоманд юти обработало лишние микрокоманды), то на выходе сумматора 8 по модулю два появляется единичньвт сигнал, который переводит триггер 5 в единичное состояние при наличии на его спнхро- входе синхроимпульса Cf, . На выходе 33 триггера 5 появляется сигнал ошиб ки, который через элемент ИЛИ 19 фор мирует сигнал Стоп на входе блока 2 синхронизации. В случае, если ошибок ни в коде микрокоманд, ни в правильности переходов между микрокомандами нет, то по окончании проверки одной микропрограммы начинается проверка следующей №-1кропрограммы Для этого на счетный сум шр1тоций вхо счетчика 10 подается единичный сиг- нал, который формируется в элементе 50 И 16 при наличии синхроимпульса и сигнала Конец микропрограммы на его выходах. Дальше работа происходит аналогично описанному.

При отсутствии ошибок в выполнении 2 всей диагностической программы происходит остановка процесса контроля с выдачей на индикацию сигнала Исправно. Останов контроля при этом происходит при появлеш и на всех трех

45

нал об ошибке в коде микрокоманлы. Этот сигнпл с выхода триггера 7 поступает через второй вход элемента ИЛИ 9, и на блок 2 синхронизации выдается сигнал Стоп. Если код не искажен, то на выходе сумматора 9 по модулю два формируется нулевой сигнал, и триггер 7 находится в нуQ левом состоянии.

Контроль правильности переходов между микрокомандам осуществляется следуюиогм образом. В счетчик 1 1 при наличии на его синхровходе единич ного сигнала, которьв формируется элементом И 16 путем подачи на его входы синхроимпульса Ц) и значения разряда Конед микрокоманды, равного 1, записывается количество мик0 рокоманд в проверяемой ветви. Затем при поступлении на вычитающий вход счетчика синхроимпульса t/, из числа записанных микрокоманд вычитается 1, и оставшееся значение выдается

5 с группы выходов 37 счетчика на элемент ИЛИ-НЕ 20. Если единичньй сигнал Конед микропрограммы поступает не одновременно с обнулением счетчика 11 (т.е. если проверяемое мик35

40

одну или несколько микрокоманд юти обработало лишние микрокоманды), то на выходе сумматора 8 по модулю два появляется единичньвт сигнал, который переводит триггер 5 в единичное состояние при наличии на его спнхро- входе синхроимпульса Cf, . На выходе 33 триггера 5 появляется сигнал ошибки, который через элемент ИЛИ 19 формирует сигнал Стоп на входе блока 2 синхронизации. В случае, если ошибок ни в коде микрокоманд, ни в правильности переходов между микрокомандами нет, то по окончании проверки одной микропрограммы начинается проверка следующей №-1кропрограммы. Для этого на счетный сум шр1тоций вход счетчика 10 подается единичный сиг- нал, который формируется в элементе 0 И 16 при наличии синхроимпульса и сигнала Конец микропрограммы на его выходах. Дальше работа происходит аналогично описанному.

При отсутствии ошибок в выполнении 2 всей диагностической программы происходит остановка процесса контроля с выдачей на индикацию сигнала Исправно. Останов контроля при этом происходит при появлеш и на всех трех

45

входах элемента И 17 единичных сигналов: сигнала Конец работы с выхода 46 и блока 12, сигнала обнуления счетчика 11 с выхода элемента ЮШ-НЕ 20 и сигнала Конец микропрограммы с выхода регистра 21. В этом случае триггер 6 цо синхроимцульсу Lj,, переходит в единичное состояние. На выходе 34 триггера формируется сигнал Исправно и вьщается на индикацию, а также поступает на третий вход элемента ШШ 19, с выхода которого на вход блока 2 синхронизации выдается сигнал Стоп. Остановку конт- роля можно производить в любой момент вручную, подавая на вход 49 элемента ИЛИ 19 единичный сигнал.

Во втором режиме - режиме ручного пошагового контроля - устройство ра- бот ает аналогично режиму автоматического контроля. Отличие состоит в том, что момент выдачи синхроимпульсов q, и tp2. задается вручную. Это достигается путем подачи единичного сигнала-на вход 52 блока 2 синхрони- зации и последовательной подачи сигналов на .входы 57 и 26 блока 2 синхронизации. При подаче единичного синала на вход 57 блок 2 синхронизации выдает синхроимпульс первой фазы С}, на выход 35, а при подаче единичного сигнала на вход. 26 блок ,2 синхронизации выдает синхроимпульс второй фазы CCi на выход 36. Это удобно при отладке ; проверяемого микропрограммного устройства.

Формула

изобретения

Устройство для контроля устройства микропрограммного управления, содержащее первый регистр, первый и второй, сумматоры по модулю два, первый и второй элементы ИЛИ и первый (триггер,причем группа выходов кода. микрокоманды контролируемого .устройства подключена к входам первого сумматора по модулю два, выход которого

ШШ-НЕ, причем первый выход блока синхронизации является.выходом устройства для подключения к первому тактовому входу контролируемого уст- ройства с первыми входами первого и второго элементов И и с тактовыми входами второго и третьего триггеров, прямой выход третьего триггера является первым вьтодом ошибки устройства и соединен с первым входо первого элемента ШШ, выход первого элемента ИЛИ соединен с входом останова блока синхрони зации, второй выход которого является выходом устрой ства для подключения к второму такто вому входу контролируемого устройства, со счетным входом первого счет чика и с тактовым входом первого триггера, прямой выход которого явля ется вторым выходом ошибки устройств и соединен с вторым входом элемента ИЛИ, вход разрешения контроля устрой ства соединен с единичным входом чет вертого триггера, прямой выход которого соединен с первьм и вторым входами первого элемента 2И-ИЛИ, инверс ный выход четвертого триггера соединен с входом записи второго счетчика выход первого элемента 2И-:ШШ ется выходом устройства для подключе ния к первому разряду .адреса следующей микрокоманды контролируемого уст ройства, первый, второй, третий и четвертый выходы блока оперативной памяти соединены соответственно с входом устройства для подключения .к входу начального адреса контролиру емого устройства, с информационным входом первог о регистра, с информационным входом счетчика и с первым входом третьего элемента И, выход которого соединен с информационным входом второго триггера, информацион д5 ,ный выход первого счетчика соединен с входом элемента Ш1И-НЕ и.является первым информационным выходом устрой ства, первый, второй и третий выходы блока оперативной памяти образу

40

МсП, Upd ни , М ., ..- - f, ,

соединен с информационным входом пер- ют информационный выход уст- „ ,, .. ,„ m о - ппйгтвя- выхоп пеового регистра сового триггера, о т л и ч а, ю щ е - е с я тем, что, с .целью повышения достоверности контроля, в устройство введены блок синхронизации, второй, третий и четвертый триггеры, первый и второй счетчики, втор-ой регистр, блок оперативной памяти, первый и второй элементы, 2И-Ш1И, первый, второй и третий элементы И и элемент

55

ройства, выход первого регистра соединен с третьим входом первого элемента 2И-ИЛИ, прямой вход второго триггера является выходом корректно го завершения контроля устройства и соединен с нулевым входом четвертого триггера и третьим входом перв го элемента ШК, информационный выход второго счетчика соединен с ин

Q 5 о

ШШ-НЕ, причем первый выход блока синхронизации является.выходом устройства для подключения к первому тактовому входу контролируемого уст- ройства с первыми входами первого и второго элементов И и с тактовыми входами второго и третьего триггеров, прямой выход третьего триггера является первым вьтодом ошибки устройства и соединен с первым входом первого элемента ШШ, выход первого элемента ИЛИ соединен с входом останова блока синхрони зации, второй выход которого является выходом устройства для подключения к второму тактовому входу контролируемого устройства, со счетным входом первого счетчика и с тактовым входом первого триггера, прямой выход которого является вторым выходом ошибки устройства и соединен с вторым входом элемента ИЛИ, вход разрешения контроля устройства соединен с единичным входом четвертого триггера, прямой выход которого соединен с первьм и вторым входами первого элемента 2И-ИЛИ, инверсный выход четвертого триггера соединен с входом записи второго счетчика, выход первого элемента 2И-:ШШ ется выходом устройства для подключения к первому разряду .адреса следующей микрокоманды контролируемого устройства, первый, второй, третий и четвертый выходы блока оперативной памяти соединены соответственно с входом устройства для подключения .к входу начального адреса контролируемого устройства, с информационным входом первог о регистра, с информационным входом счетчика и с первым входом третьего элемента И, выход которого соединен с информационным входом второго триггера, информацион- д5 ,ный выход первого счетчика соединен : с входом элемента Ш1И-НЕ и.является первым информационным выходом устройства, первый, второй и третий выходы блока оперативной памяти образу5

40

, ,

ют информационный выход уст- ппйгтвя- выхоп пеового регистра со

ройства, выход первого регистра соединен с третьим входом первого элемента 2И-ИЛИ, прямой вход второго триггера является выходом корректного завершения контроля устройства и соединен с нулевым входом четвертого триггера и третьим входом перво го элемента ШК, информационный выход второго счетчика соединен с инфор2Нтционным входом второго элемента 1ЛИ и является третьим ииформаци

OHHI.IM выходом устройства, информашый выход второго счетчика и вто вход второго элемента 2И-ИЛИ яв7

цио рой ляю|гся соответственно первь1м и втоарсным входами второго элемента гШИ, выход которого соединен с адта

адресными входами устройства,вхо

рым

признака начала контроля устройства соединен с входом записи блэка оперативной памяти, с третьим прямым и инв 2Иресным входом блока оперативной памяти, группа выходов логических ус- ловяй контролируемого устройства соединена с входами второго элемен- ИЛИ, выход которого соединен с

четвертым

дам{и

с

И,

прямым и инверсным

вхопервого элемента 2И-ИЛИ и вторым входом первого элемента выход которого соединен с входом сдвига первого регистра, выход призка конца микропрограммы контролируемого устройства соединен с вторыми

0

5

0

Z-i

входами второго и третьего элементов И н с первым входом второго сумматора по модулю два, выход которого соединен с информационным входом третьего триггера, выход второго элемента И соединен с входами записи первого регистра и первого счетчика и со счетным входом второго счетчика, выход первого разряда адреса следующей микрокоманды контролируемого устройства соединен с пятым входом первого элемента 2И-1ШН, выход элемента ШШ-НЕ соединен с вторым входом второго сумматора по модулю два и третьим входом третьего элемента И, вход останова устройства соединен с четвертым входом элемента ИЛИ, информационный вход устройства соединен с информационным входом блока оперативной памяти, входы пуска, автоматической работы, шага, первый и второй тактовые входы устройства соединены соответственно с вторым-шестым входами блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1495789A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

Изобретение относится к вычислительной технике и может быть использовано для проверки микропрограммных устройств управления и их отладки. Целью изобретения является повышение достоверности контроля. Устройство содержит проверяемое микропрограммное устройство, блок синхронизации, регистры, триггеры, сумматоры по модулю два, счетчики, блок оперативной памяти, элементы 2И-ИЛИ, элементы И и элемент ИЛИ-НЕ. Устройство может работать в двух режимах : первый режим - режим автоматического контроля, второй - режим ручного пошагового контроля. 5 ил.

Г Начало Llr

Bx.

контроль мне M219)

Фие.2

т

I

/W (topMupye/ffca cut/tynofi

I

CiBu Ш

Я&25: 1,1

Фиг.З

2(фие.2)

Ш1а5

Составитель И.Сигалов Редактор А.Ыандор Техред М.Дидык Корректор О.Кравцова

Заказ 3618

Тираж 570

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКЙТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Устройство для контроля микропроцессорных программных блоков | 1983 |

|

SU1267424A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Барбаш И.П., Тимонькин Г.Н., Ткаченко С.II., Харченко B.C | |||

| Синтез микрспрограммных автоматов, ч | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-11-23—Публикация

1988-10-03—Подача