Изобретение относится к вычислительной технике и может быть использовано для отладки программ и тестирования микропроцессорньге систем (МПС).

Цель изобретения - повьшение быстродействия процесса отладки программ за счет ускорения исполнения отладочных процедур.

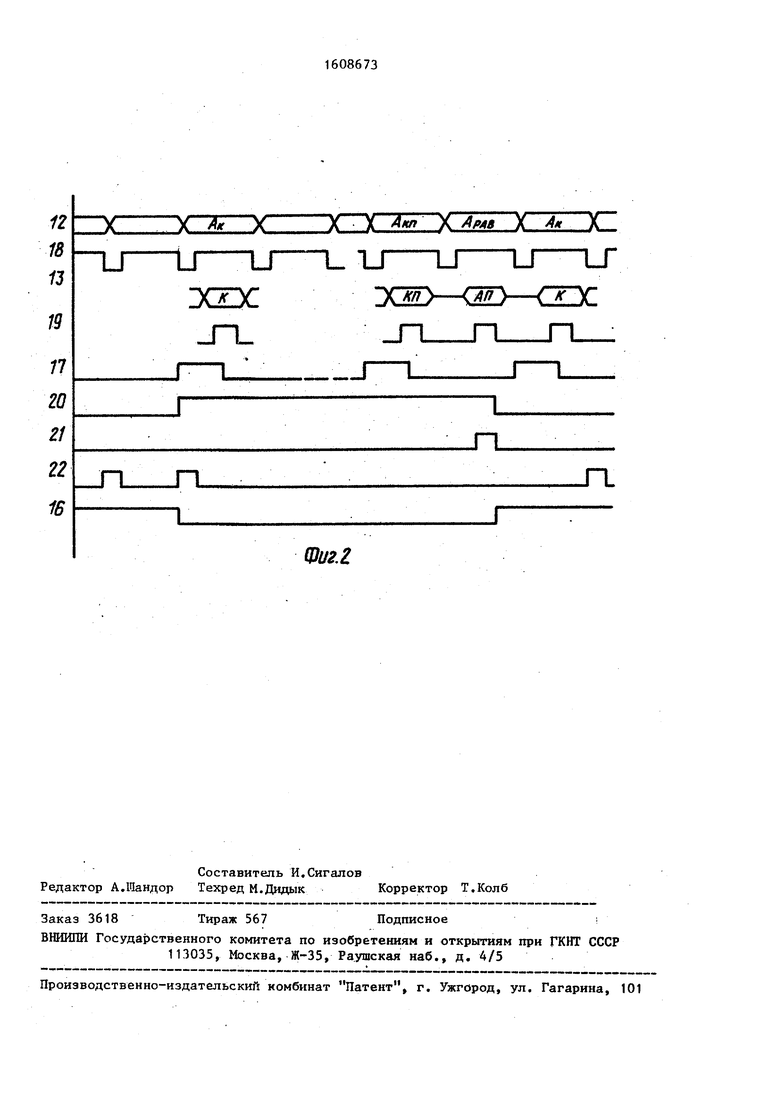

На фиг.1 приведена функциональная схема устройства; на фиг.2 - временные диаграммы.

Устройство содержит наладочный блок 1 памяти, регистр 2 адреса воз- врата, блок 3 элементов И,блок 4 вычитания, селектор 5 адреса, первый 6 и второй 7 триггеры, первый 8, второй 9 и третий 10 элементы И, элемент НЕ 11, входную шину 12 адреса, входную и выходную шины 13 данных, входную шину 14 управления, вход 15 запуска устройства, выход 16 разрешения выборки основной памяти, вход 17 признака команды, вход 18 синхроим- пульса, вход 19 призна:ка чтения, вход

20разрешения выборки блока 1, вход

21записи регистра 2.

Через шины 12-14 устройство под- ключается к соответствующим шинам отлаживаемой МПС,

В наладочном блоке 1 памяти хранятся коды команд и данных отладочной процедуры. В кйнал отлаживаемой МПС блок 1 памяти подключается толь- ко на время исполнения отладочной процедуры сигналом на входе 20. ,

. Гт

1

Регистр 2 адреса возврата предназначен для запоминания адреса из ка- нала МПС по сигналу на входе 21.

Блок 4 вычитания служит для преобразования текущих адресов Aj в канале МПС в адрес А V наладочного блока 1 памяти, вычисленный относитель-

но адреса А. возврата по формуле о

А;- А.

Устройство работает в одном из

двух режимов: ожидания и отладки.

В режиме ожидания триггеры 6 и 7 обнулены (цепи начальной установки не показаны), первый элемент И 8 заперт нулевым уровнем сигнала на входе 15.

Каждый синхроимпульс на входе 18 адресного цикла МПС, проходя через ; элемент НЕ 11 и третий элемент И 10, . своим передним фронтом фиксирует те

5

о

5

0

5

кущий адрес МПС в регистре 2 адреса возврата. На оба входа блока 4 вычитания при этом поступает один и тот же адресный код, поэтому с его выхода на адресный вход наладочного блока 1 памяти в каждом машинном цикле поступает код адреса, равный О, однако выборка этого блока в режиме ожидания запрещена нулевым уровнем сигнала на прямом выходе 20 первого триггера 6.

Для перевода в режим отладки на вход 15 запуска устройства подается разрешающий сигнал. Очередным признаком на входе 17 команды, поступаюш им по первому разряду шины управления из МПС, устанавливается первый триггер 6. Сигнал с прямого выхода 20 этого триггера разрешает выборку наладочного блока 1 памяти, а сигнал с инверсного выхода 16 запрещает выборку основной памяти МПС. Очередной адрес, сформированный процессором МПС на шине 12, преобразуется в нулевой физический адрес на адресном входе наладочного блока 1 памяти.

По переднему фронту синхроимпульса на входе 18 адресного цикла (второй разряд шины 14 управления) проис г ходит установка второго триггера 7, . сигнал с инверсного выхода которого запирает третий элемент И 10, в ре- : зультате чего блокируется изменение j адреса, принятого в регистр 2. Этот адрес возврата А хранится в регистре 2 все время, пока Устройство находится в режиме отладки. .

Так как выборка наладочного блока, 1 памяти .разрешена, содержимое его нулевой ячейки вьщается в шину 13 данных МПС и воспринимается процессором как код очередной команды. ,С этого момента управление МПС осуществляется программой, хранищейоя в наладочном блоке памяти, которая и организует исполнение отладочных процедур. При этом в процессоре МПС сохраняется естественный порядо из- i менения счетчика команд, т.е. адресации, так как преобразование текущих адресов на шине 12 в адреса наладочного блока 1 памяти выполняется автсжатически блоком 4 вычитания.

Следовательно, переход на-отладочную программу не требует специальной команды передачи управления. Каких- либо ограничений на команды, используемые дпя отладки, в том числе и, ;

на тип первой команды, при этом не на шадывается.

Выход из режима- отладки осуществляется в результате исполнения комады передачи управления по адресу во вр1та, которой должна заканчиваться оттадочная программа.В качестве источника адреса возврата в этой команде указывается адрес регистра 2, приев эенный последнему в адресном пространстве МПС. При обращении процессора МПС по этому адресу срабатывает селектор 5, его выходной сигнал раз- ре иает прохождение сигнала - признака на входе 19 чтения (3-й разряд шиЩ) 14 управления) через второй эле меiT И 9 на вход блока 3 элементов И

Блок 3 открывается, содержимое рег-истра 2 (код адреса возврата) пост щает на шину 13 данных и считывается процессором МПС.

Задним фронтом сигнала с выхода втэрого элемента И 9 сбрасывается пеэвый триггер 6, отключая наладочный блок 1 памяти и включая основную память МПС.

Процессор обращается по адресу возврата за командой, продолжая исполнение отлаживаемой программы.

Фзрмула изо-бретения

Устройство для отладки программ, содержащее наладочный блок памяти, регистр адреса возврата, блок эле- MeiTOB И, первый и второй триггеры, первый и второй элементы И, причем выход блока элементов И через шину цдлиых. соединен с входом-выходом наладочного блока памяти и с входом-вы хоцом устройства, входы запуска и 1ризнака команды устройства соединены соответственно с первым и вторы ч входами первого элемента И, вы- хоц которого соединен с единичным

5

0

5

0

5

0

5

входом первого , информа- циорплш вход первого триггера соединен с огиной нулевого потенциала устройства, прямой выход первого триггера соединен с входом разрешения выборки наладочного блока памяти, с первым входом второго элемента И и с информационным входом второго триггера, информационный выход регистра адреса соединен с информационным входом блока элементов И, вход признака чтения устройства соединен с вторым входом второго элемента И, выход которого соединен с управляющим входом блока элементов И и с тактовым входом первого триггера,инверсный выход которого является выходом разрешения выборки основной памяти устройства, отличающееся тем, что, с целью повышения быстродействия, в устройство введены блок вычитания, третий элемент И, элемент НЕ и селектор адреса, причем вход синхронизации устройства соединен с тактовым входом селектора адреса и через элемент НЕ - с тактовым входом второго триггера и с первым входом третьего эле-, мента И, выход которого соединен с входом записи регистра адреса возврата, выход которого соединен с входом вычитаемого блока вычитания, адресный вход устройства соединен с входом уменьшаемого блока вычитания, выход которого соединен с адресным входом наладочного блока памяти, вход признака записи устройства соединен с входом записи наладочного блока памяти, адресный вход устройства соединен с информационным входом селектора адреса, выход которого соединен с третьим входом второго элемента И, , инверсный выход второго триггера со-; единен с вторым входом третьего элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1982 |

|

SU1100627A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Устройство для отладки программ | 1987 |

|

SU1425687A1 |

| Устройство для отладки программ | 1986 |

|

SU1383372A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Устройство для отладки программ | 1979 |

|

SU849218A1 |

Изобретение относится к вычислительной технике и может использоваться для отладки программ и тестирования микропроцессорных систем. Цель изобретения - повышение быстродействия процесса отладки за счет использования синтаксической информации и ускорения исполнения отладочных процедур. Устройство содержит наладочный блок 1 памяти, регистр 2 адреса возврата, блок 3 элементов И, блок вычитания 4, триггеры 6 и 7, три элемента И 8 - 10, элемент НЕ 11 с соответствующими связями, которые обеспечивают подстановку команд отладочной процедуры в заданном месте вычислительного процесса. 2 ил.

| Зепенко Г.В | |||

| и др | |||

| Проектирование и отладка микропроцессорных -М.: Машиностроение, 1982 | |||

| систем | |||

| Устройство для отладки программ | 1982 |

|

SU1100627A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-23—Публикация

1988-06-08—Подача