ВХ.ЛНУ .. Вх7ТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дешифратора | 1987 |

|

SU1479934A1 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

| Устройство для деления чисел на константу 2 @ + 1 | 1990 |

|

SU1746379A1 |

| Устройство для регистрации неустойчивых сбоев | 1986 |

|

SU1397916A1 |

| Устройство для приема цифровой информации | 1986 |

|

SU1332357A1 |

| Устройство предварительной выборки команд | 1987 |

|

SU1561073A1 |

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

| Устройство для вычисления порядковых статистик последовательности двоичных чисел | 1984 |

|

SU1239708A1 |

| Устройство для вычисления контрольного элемента и обнаружения ошибок | 1986 |

|

SU1325483A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

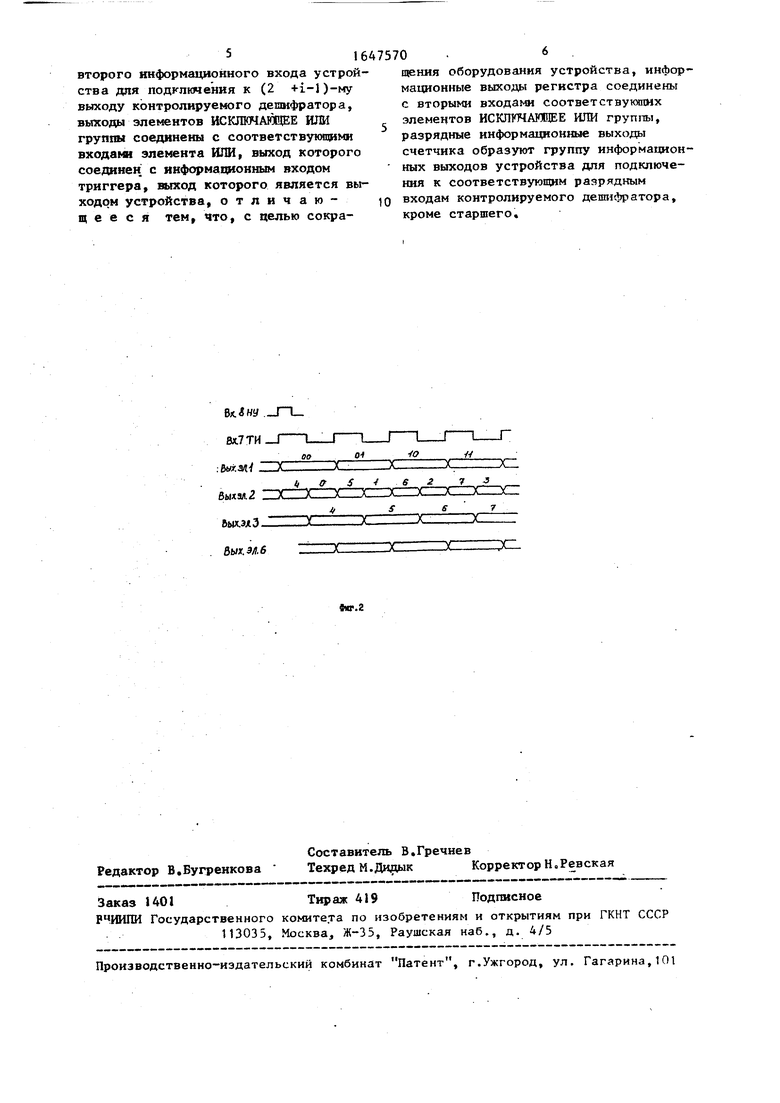

Изобретение относится к автоматике и вычислительной технике и может быть использовано в диагностической аппаратуре,. Цель изобретения - сокращенна оборудования устройства Устройство соде ржит счетчик it регистр 3, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4, элемент ИЛИ 5 и триггер 6. На установочный вход 8 устройства в начале работы поступает сигнал, устанавливающий триггер 6 и регистр 3 в нулевое состояние. Счетчик } под воздействием меандров, поступающих на тактовый вход 7 устройства, формирует последовательность сигналов, поступающую на младшие разряды информационного входа контролируемого дешифратора 2. На старший разряд информационного входа дешифратора 2 поступает меандр с тактового входа 7 устройства. Сигналы, формируемые дешифратором 2, в первых полутактах тактов задерживаются на один такт на регистре 3 и сравниваются на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 4 группы с сигналами, формируемыми во вторых полутактах этих тактов.Элемент ИЛИ 5 объединяет результаты сравнения в сигнал контроля, записываемый в триггер 6. 2 ил. о S (О

01

н

:BW.SlY

« о S v в г 7 J

выхм2 ZDCUXZZXдX х л-DCZ)d

&ЫХ.Э/1.6

01

10

н

ЭС1

Авторы

Даты

1991-05-07—Публикация

1989-04-04—Подача