(21)4310456/24-24

(22)28.09.87

(46) 15.05.89. Бюл. № 18 (72) П.И.Плиц и А.В.Дрозд

(53)681.3 (088.8)

(56)Авторское свидетельство СССР № 896001, кл. С 06 F 11/00, 1980.

Авторское свидетельство СССР № 1283770, кл. G 06 F 11/00, 1985.

(54)УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДЕШИФРАТОРА

(57)Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении тестовой аппаратуры. Цель изобретения - сокращение оборудования устройства. Устройство для контроля дешифратора содержит счетчик 1, первую группу 5 и вторую группу 2 элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ, регистр 4, элемент ИЛИ 6 и триггер 7. С помощью тактовых импульсов с установочного входа 8 устройства и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 2 инвертируется код счетчика 1, поступающий на информационные входы контролируемого дешифратора 3. При правильной работе контролируемого дешифратора 3 единичные сигналы на его выходах будут

появляться по определенному закону.

., Ф ,

На регистре 4 запоминаются выходы

дешифратора 3, соответствующие инверсному коду счетчика 1. С помощью соответствующего подключения выходов контролируемого дешифратора 3 и регистра 4 к входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 5 определяется неправильная работа дешифратора 3. 2 ил.

С S

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дешифратора | 1989 |

|

SU1647570A1 |

| Устройство для регистрации неустойчивых сбоев | 1986 |

|

SU1397916A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Устройство для приема цифровой информации | 1986 |

|

SU1332357A1 |

| Устройство для программируемой задержки информации | 1986 |

|

SU1394213A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Устройство для телеконтроля промежуточных станций системы связи | 1989 |

|

SU1674385A1 |

| Устройство для контроля цифровых систем | 1980 |

|

SU900286A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении тестовой аппаратуры. Цель изобретения - сокращение оборудования устройства. Устройство для контроля дешифратора содержит счетчик 1, первую группу 5 и вторую группу 2 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, регистр 4, элемент ИЛИ 6 и триггер 7. С помощью тактовых импульсов с установочного входа 8 устройства и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 2 инвертируется код счетчика 1, поступающий на информационные входы контролируемого дешифратора 3. При правильной работе контролируемого дешифратора 3 единичные сигналы на его выходах будут появляться по определенному закону. На регистре 4 запоминаются выходы дешифратора 3, соответствующие инверсному коду счетчика 1. С помощью соответствующего подключения выходов контролируемого дешифратора 3 и регистра 4 к входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 5 определяется неправильная работа дешифратора 3. 2 ил.

О 1 2 3

J 5-Jz

2 6 Тп-I/

2

1

8

1 2 J

4

54 53 5,2 5Л

Я

4

СО СО ОЭ Ј

фи$Л

С

МММ

/

.ю

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении тестовой аппаратуры,

Целью изобретения является сокращение оборудования устройства.

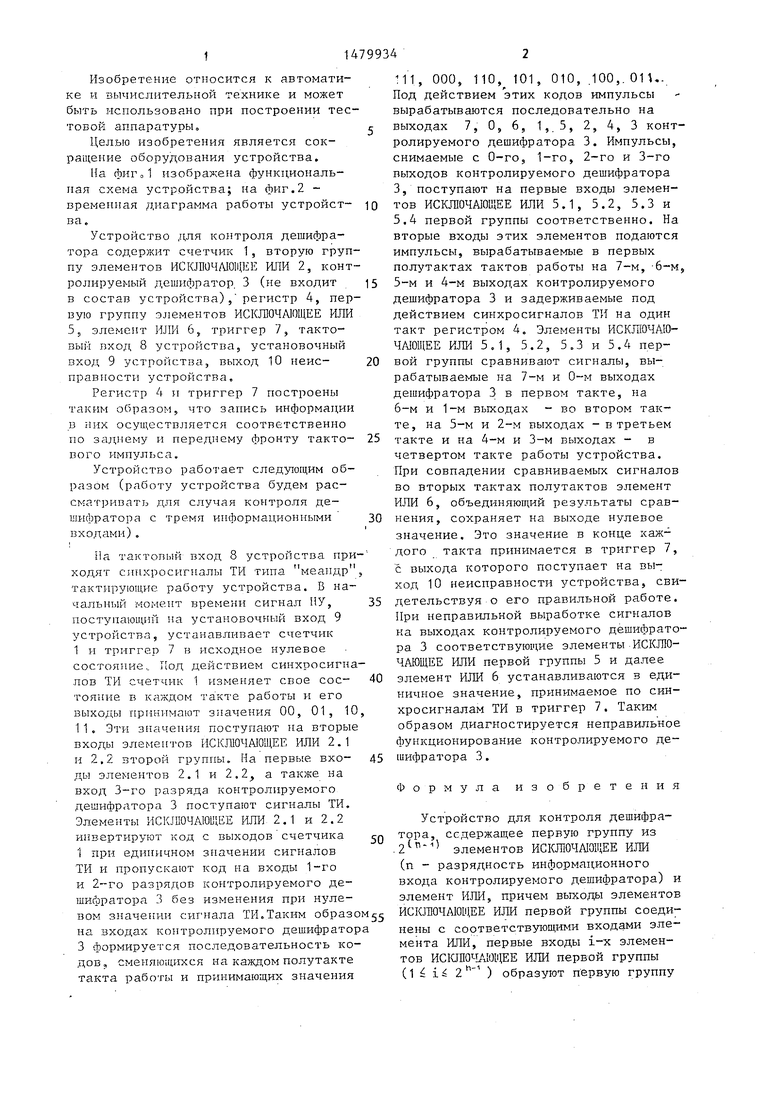

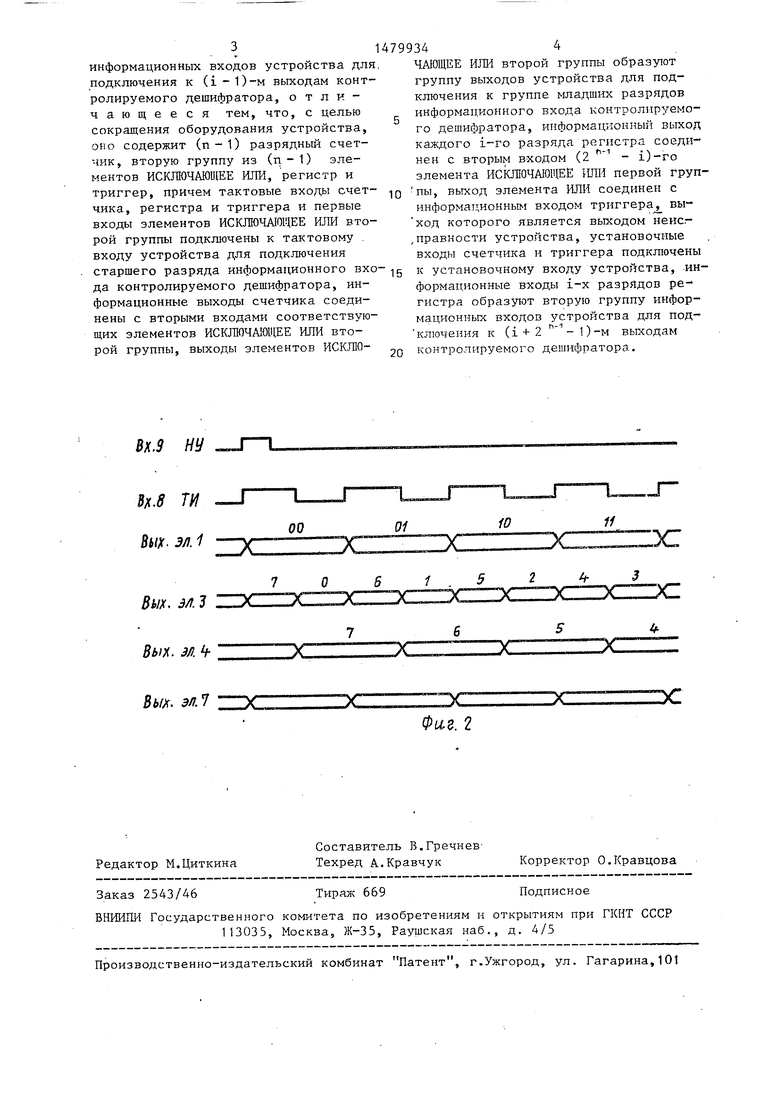

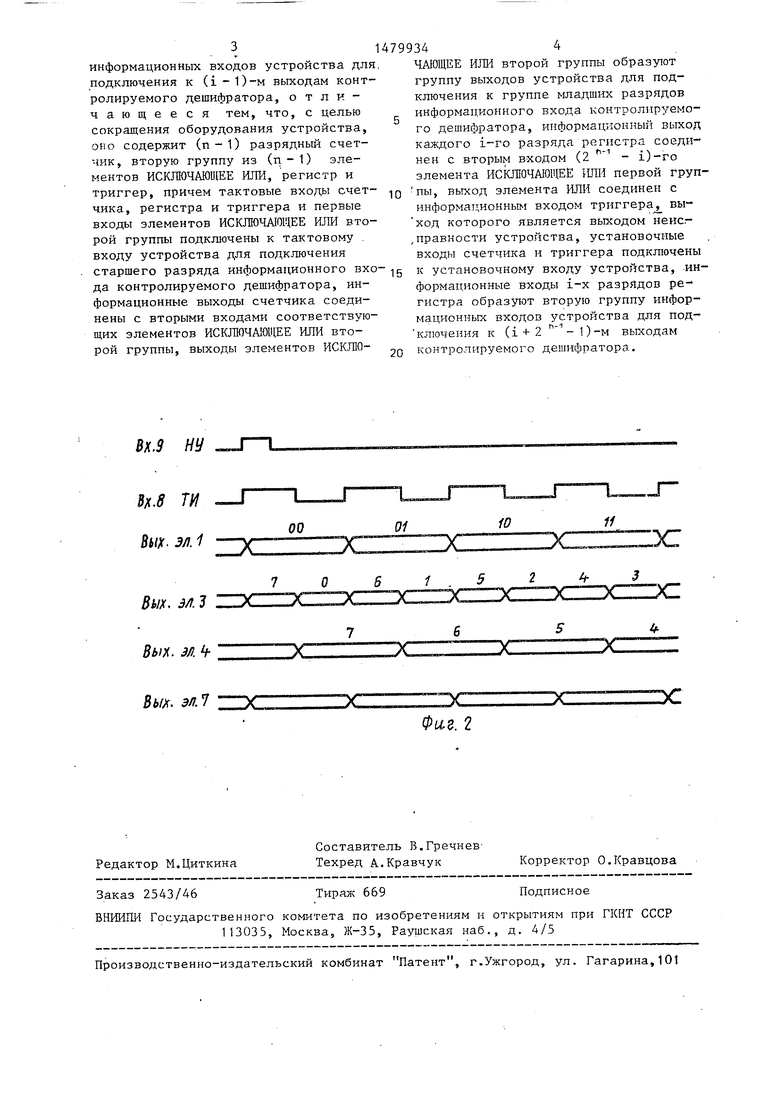

На фиго1 изображена функциональная схема устройства; на фиг.2 - временная диаграмма работы устройст- ва.

Устройство для контроля дешифратора содержит счетчик 1, вторую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2, контролируемый дешифратор 3 (не входит в состав устройства), регистр 4, первую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5, элемент ИЛИ 6, триггер 7, тактовый вход 8 устройства, установочный вход 9 устройства, выход 10 неис- правности устройства.

Регистр 4 и триггер 7 построены таким образом, что запись информации в них осуществляется соответственно по заднему и переднему фронту такто- вого импульса.

Устройство работает следующим образом (работу устройства будем рассматривать для случая контропя дешифратора с тремя информационными входами).

Па тактовый вход 8 устройства приходят синхросигналы ТИ типа меандр, гактирующио работу устройства. В начальный момент времени сигнал НУ, поступающий на установочный вход 9 устройства, устанавливает счетчик 1 и триггер 7 в исходное нулевое состояние,. Под действием синхросигналов ТИ счетчик 1 изменяет свое сое- тоянне в каждом такте работы и его выходы принимают значения 00, 01, 10, 11. Эти значения поступают на вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2.1 и 2,2 второй группы. На первые вхо- ды элементов 2.1 и 2.2 а также на вход 3-го разряда контролируемого дешифратора 3 поступают сигналы ТИ. Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 2.1 и 2.2 инвертируют код с выходов счетчика 1 при единичном значении сигналов ТИ и пропускают код па входы 1-го и 2-го разрядов контролируемого дешифратора 3 без изменения при нулевом значении сигнала ТИ.Таким образом на входах контролируемого дешифратора 3 формируется последовательность ко- цов, сменяющихся на каждом полутакте такта работы и принимающих значения

М1, 000, 110, 101, 010, 100, 01U. Под действием этих кодов импульсы вырабатываются последовательно на выходах 7, 0, 6, 1, 5, 2, 4, 3 контролируемого дешифратора 3. Импульсы, снимаемые с 0-го, 1-го, 2-го и 3-го выходов контролируемого дешифратора 3, поступают на первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5.1, 5.2, 5.3 и 5.4 первой группы соответственно. На вторые входы этих элементов подаются импульсы, вырабатываемые в первых полутактах тактов работы на 7-м, 6-м 5-м и 4-м выходах контролируемого дешифратора 3 и задерживаемые под действием синхросигналов ТИ на один такт регистром 4. Элементы ИСКЛЮЧАЮ- ЧАЮЩЕЕ ИЛИ 5.1, 5.2, 5.3 и 5.4 первой группы сравнивают сигналы, вырабатываемые на 7-м и 0-м выходах дешифратора 3 в первом такте, на 6-м и 1-м выходах - во втором такте, на 5-м и 2-м выходах - в третьем такте и на 4-м и 3-м выходах - в четвертом такте работы устройства. При совпадении сравниваемых сигналов во вторых тактах полутактов элемент ИЛИ 6, объединяющий результаты сравнения, сохраняет на выходе нулевое значение. Это значение в конце каждого такта принимается в триггер 7, с выхода которого поступает на выход 10 неисправности устройства, свидетельствуя о его правильной работе. При неправильной выработке сигналов на выходах контролируемого дешифратора 3 соответствующие элементы ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы 5 и далее элемент ИЛИ 6 устанавливаются в единичное значение, принимаемое по синхросигналам ТИ в триггер 7. Таким образом диагностируется неправильное функционирование контролируемого дешифратора 3.

Формула изобретения

Устройство для контроля дешифратора, содержащее первую группу из 2( элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (п - разрядность информационного входа контролируемого дешифратора) и элемент ИЛИ, причем выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединены с соответствующими входами элемента ИЛИ, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы (1 i i 2 ) образуют первую группу

информационных входов устройства для подключения к (1-1)-м выходам контролируемого дешифратора, отличающееся тем, что, с целью сокращения оборудования устройства, оно содержит (п-1) разрядный счетчик, вторую группу из (п-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, регистр и триггер, причем тактовые входы счетчика, регистра и триггера и первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы подключены к тактовому входу устройства для подключения

старшего разряда информационного вхо- 15 к установочному входу устройства, информационные входы 1-х разрядов регистра образуют вторую группу информационных входов устройства для под- ключения к (i+ 2 - 1)-м выходам 2о контролируемого дешифратора,

да контролируемого дешифратора, информационные выходы счетчика соединены с вторыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, выходы элементов ИСКЛЮВх.9 НУ

Ъ.8 ТИ

Вых. эл. 1

Зш, м 3 Вых. м 1+

Вш. эл.Ч

ЧАЮЩЕЕ ИЛИ второй группы образуют группу выходов устройства для подключения к группе младших разрядов информационного входа контролируемого дешифратора, информационный выход каждого 1-го разряда регистра соединен с вторым входом (2 1 - i)-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой груп- пы, выход элемента ИЛИ соединен с информационным входом триггера, вы- ход которого является выходом ненс- ,правности устройства, установочные входы счетчика и триггера подключены

Фиг. 2

Авторы

Даты

1989-05-15—Публикация

1987-09-28—Подача