Изобретение относится к вычислительной технике и может быть использовано для сопряжения между собой ЭВМ и абонентов, входящих в состав вычислительного комплекса (В К), работающего в реальном масштабе времени.

Цель изобретения - расширение области применения устройства за счет использования его в ВК реального времени и повышение производительности.

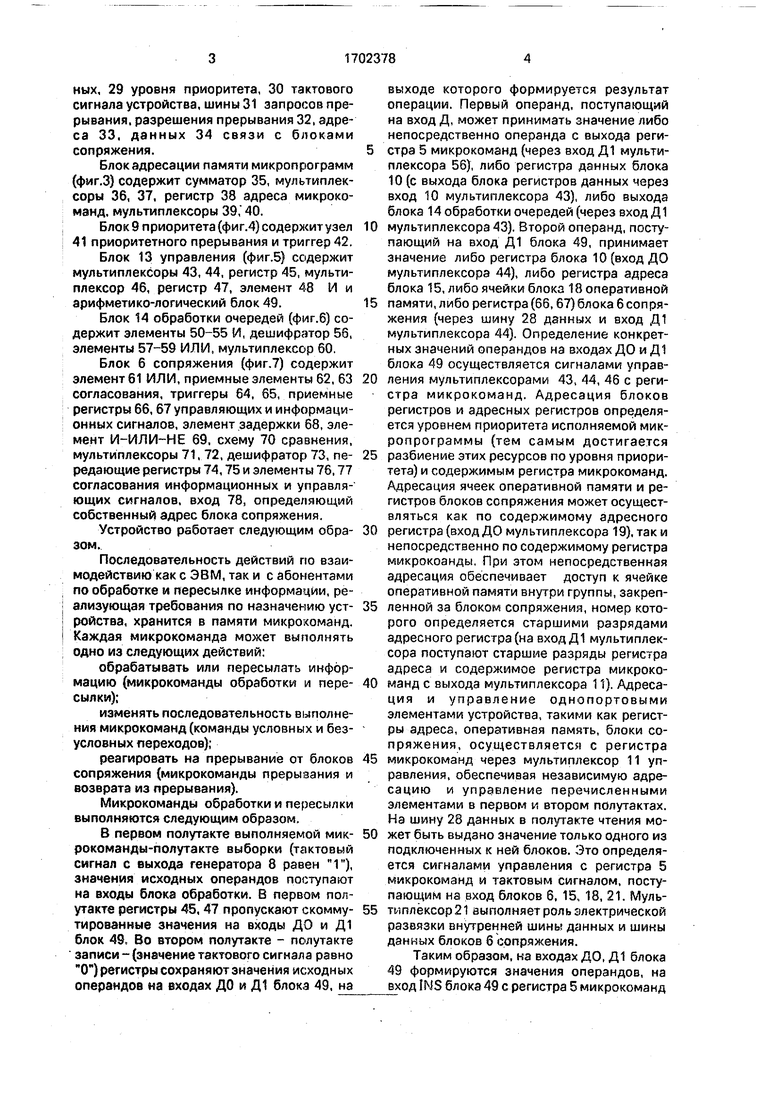

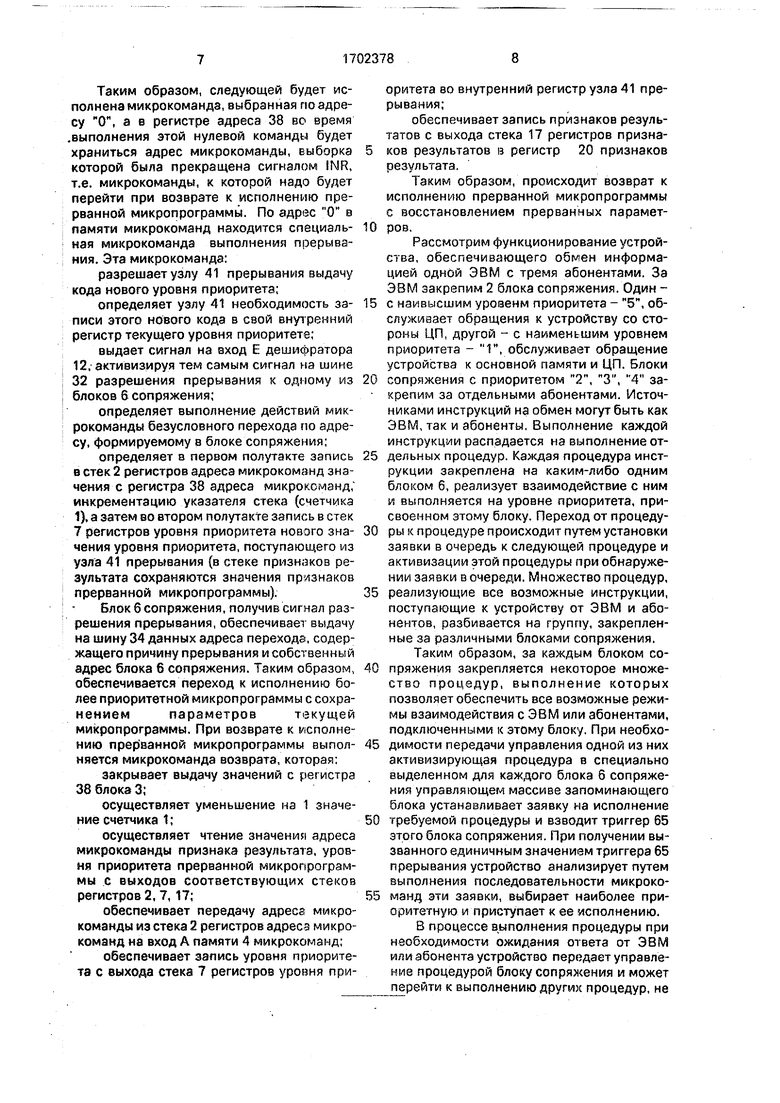

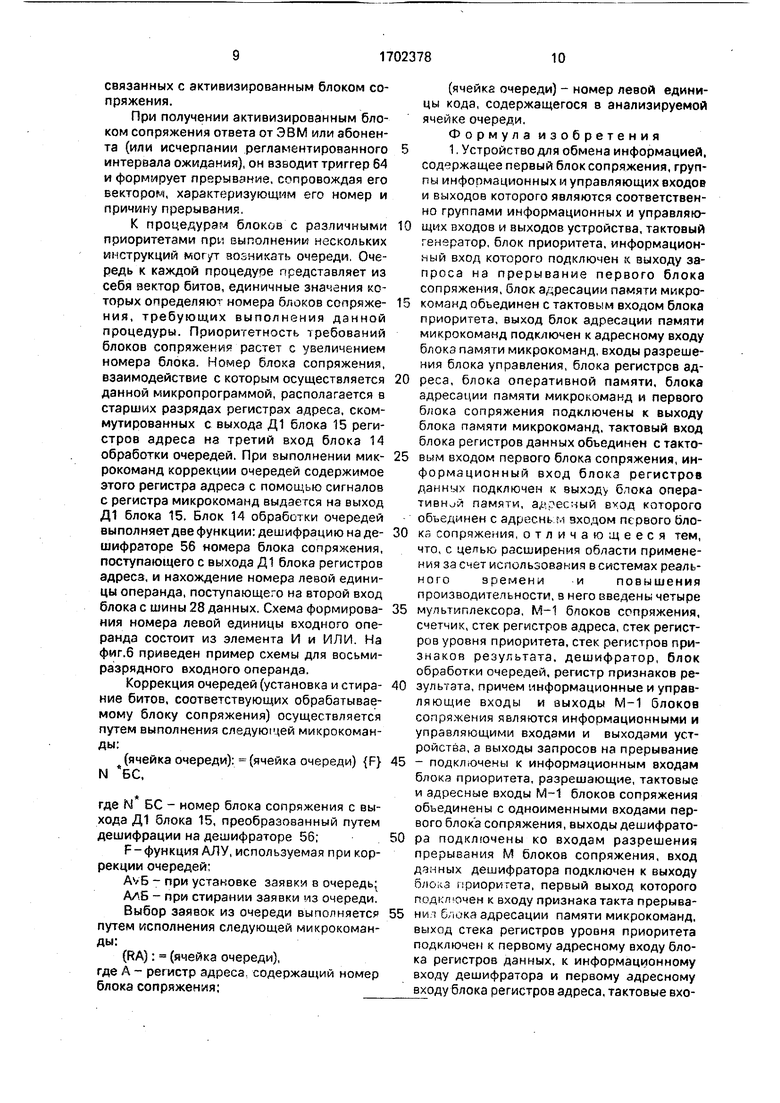

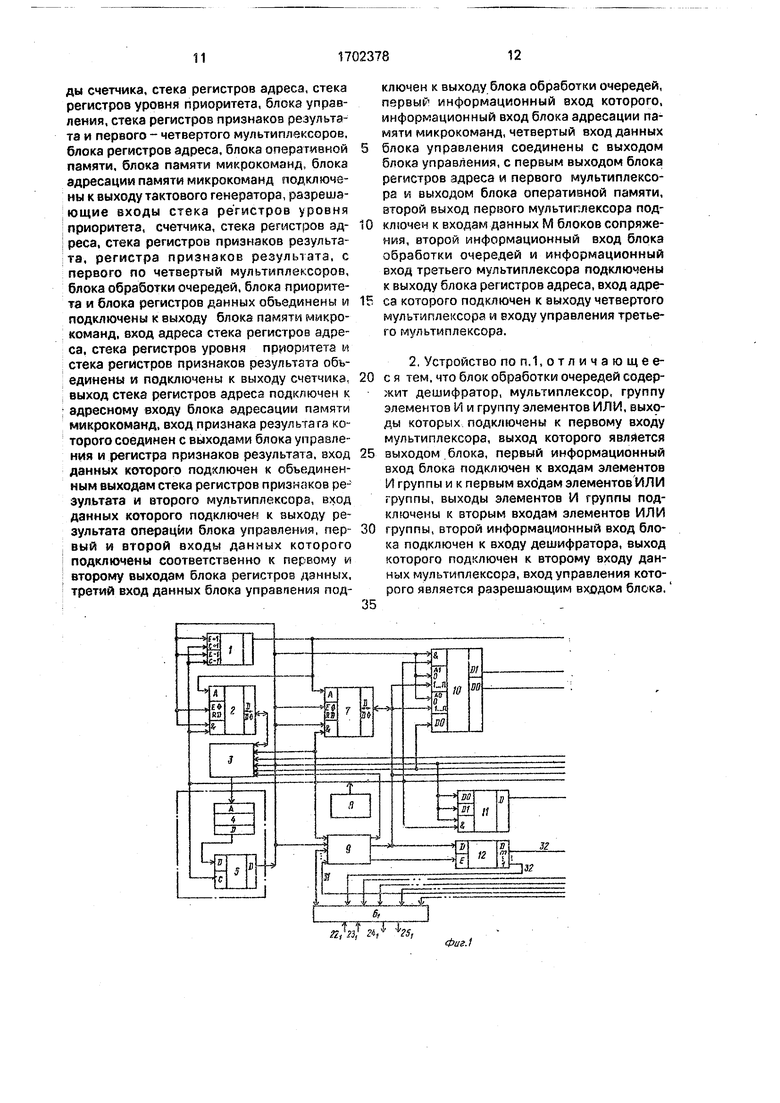

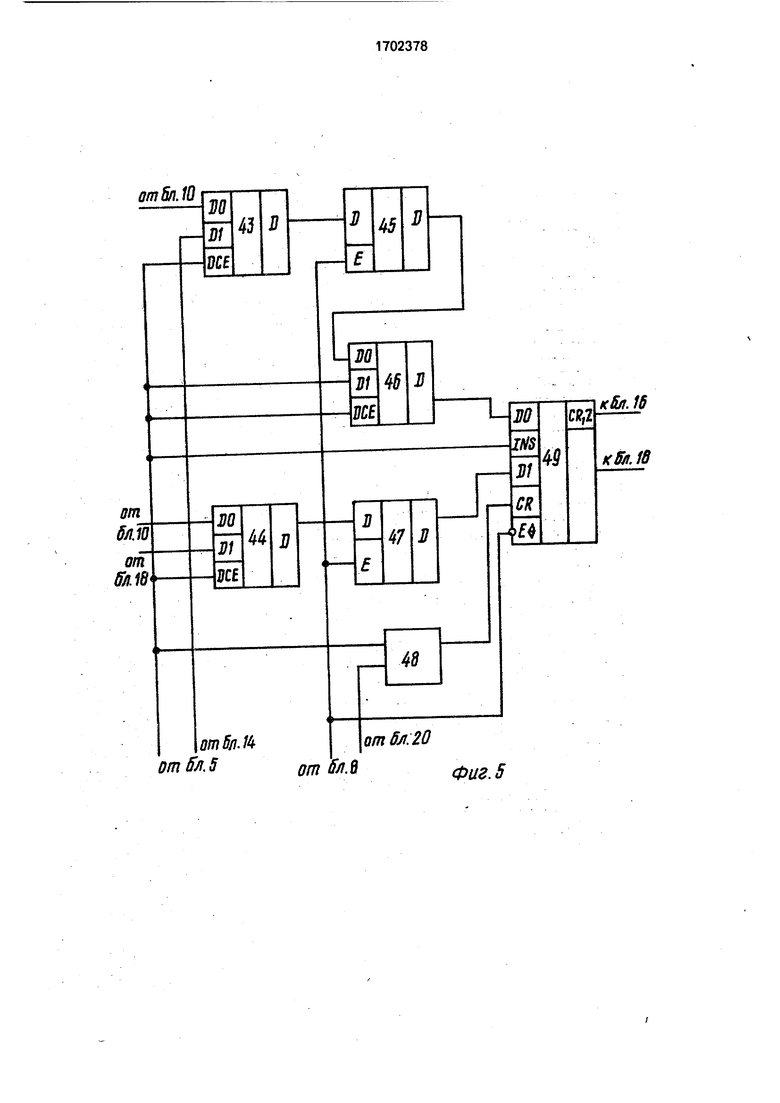

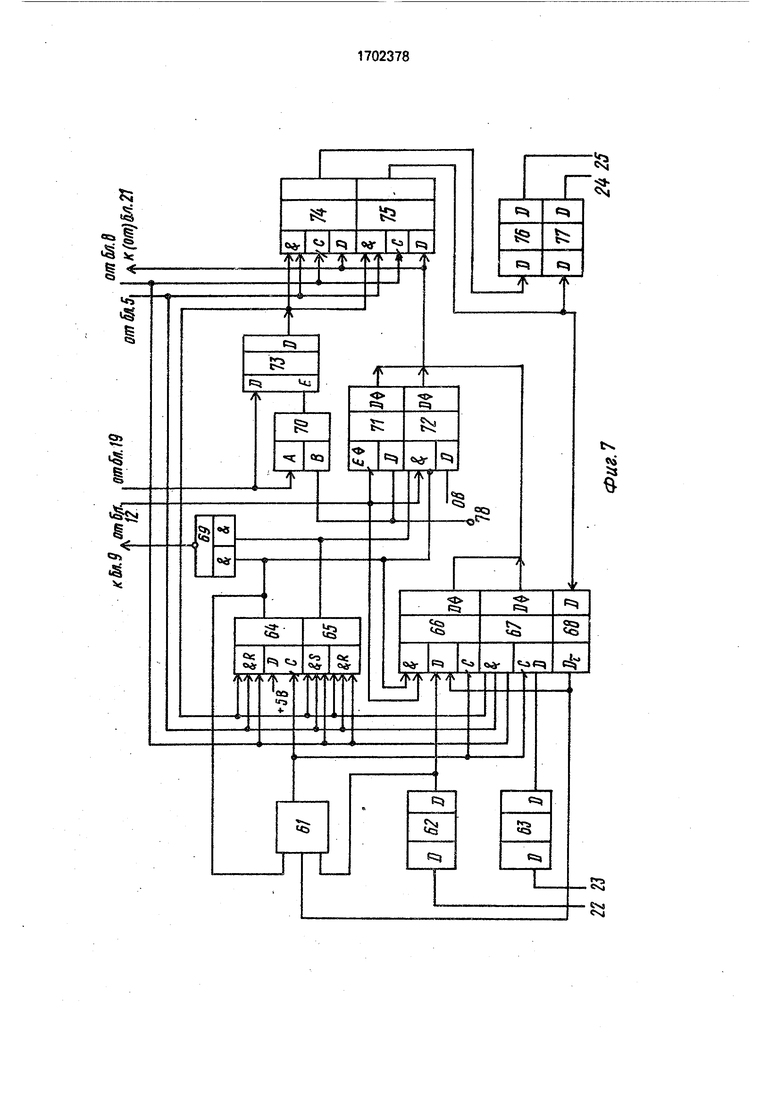

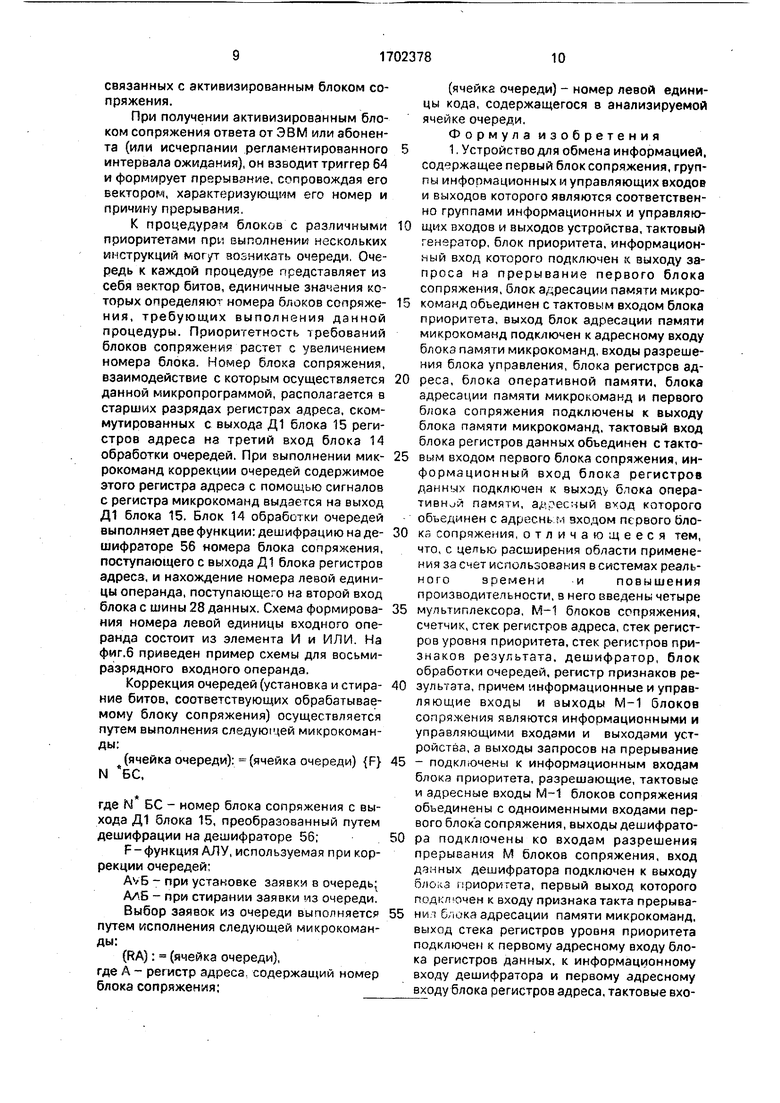

На фиг.1, 2 приведена функциональная схема устройства; на фиг.З - блок адресации памяти микропрограмм; на фиг.4 - блок приоритета; на фиг.5 - блок управления; на фиг.6 - блок обработки очередей; на фиг.7 - блок сопряжения.

Устройство содержит счетчик 1, стек 2 регистров адреса (микрокоманд), блок 3 адресации памяти микрокоманд, блок 4 памяти микрокоманд, регистр 5 микрокоманд, блоки 6i - 6м сопряжения, стек 7 регистров уровня приоритета, тактовый генератор 8, блок 9 приоритета, блок 10 регистров данных, мультиплексор 11 управления, дешифратор 12, блок 13 управления блок 14 обработки очередей, блок 15 регистров адреса, мультиплексор 16 признаков результата, стек 17 регистров признаков результата, блок 18 оперативной памяти, мультиплексор 19 адреса, регистр 20 признаков результата, мультиплексор 21 данных, входные шины 22i - 22М, 23i - 23 м, выходные шины 24i - 24М, 25i - 25м управляющих и информационных сигналов, внутренние шины 26 признаков результата, 27 микропрограммного управления, 28 данVJ

О

КЗ

ы

X 00

них, 29 уровня приоритета, 30 тактового сигнала устройства, шины 31 запросов прерывания, разрешения прерывания 32, адреса 33, данных 34 связи с блоками сопряжения.

Блок адресации памяти микропрограмм (фиг.З) содержит сумматор 35, мультиплексоры 36, 37, регистр 38 адреса микрокоманд, мультиплексоры 39, 40.

Блок 9 приоритета (фиг.4) содержит узел 41 приоритетного прерывания и триггер 42,

Блок 13 управления (фиг.5) содержит мультиплексоры 43, 44, регистр 45, мультиплексор 46, регистр 47, элемент 48 И и арифметико-логический блок 49.

Блок 14 обработки очередей (фмг.6) содержит элементы 50-55 И, дешифратор 56, элементы 57-59 ИЛИ, мультиплексор 60.

Блок 6 сопряжения (фиг.7) содержит элемент 61 ИЛИ, приемные элементы 62, 63 согласования, триггеры 64, 65, приемные регистры 66,67 управляющих и информационных сигналов, элемент задержки 68, элемент И-ИЛИ-НЕ 69, схему 70 сравнения, мультиплексоры 71, 72, дешифратор 73, передающие регистры 74,75 и элементы 76,77 согласования информационных и управляющих сигналов, вход 78, определяющий собственный адрес блока сопряжения.

Устройство работает следующим образом.

Последовательность действий по взаимодействию как с ЭВМ, так и с абонентами по обработке и пересылке информации, реализующая требования по назначению устройства, хранится в памяти микрокоманд. Каждая микрокоманда может выполнять одно из следующих действий:

обрабатывать или пересылать информацию (микрокоманды обработки и пересылки);

изменять последовательность выполнения микрокоманд (команды условных и безусловных переходов);

реагировать на прерывание от блоков сопряжения (микрокоманды прерывания и возврата из прерывания).

Микрокоманды обработки и пересылки выполняются следующим образом,

В первом полутакте выполняемой мик- рокоманды-полутакте выборки (тактовый сигнал с выхода генератора 8 равен 1), значения исходных операндов поступают на входы блока обработки. В первом полутакте регистры 45, 47 пропускают скомму- тирозанные значения на входы ДО и Д1 блок 49, Во втором полутакте - полутакте записи - (значение тактового сигнала равно О) регистры сохраняют значения исходных операндов на входах ДО и Д1 блока 49, на

выходе которого формируется результат операции. Первый операнд, поступающий на вход Д, может принимать значение либо непосредственно операнда с выхода регистра 5 микрокоманд (через вход Д1 мультиплексора 56), либо регистра данных блока 10 (с выхода блока регистров данных через вход 10 мультиплексора 43), либо выхода блока 14 обработки очередей (через вход Д1

0 мультиплексора 43). Второй операнд, поступающий на вход Д1 блока 49, принимает значение либо регистра блока 10 (вход ДО мультиплексора 44), либо регистра адреса блока 15, либо ячейки блока 18 оперативной

5 памяти, либо регистра (66,67) блока 6 сопряжения (через шину 28 данных и вход Д1 мультиплексора 44). Определение конкретных значений операндов на входах ДО и Д1 блока 49 осуществляется сигналами управ0 ления мультиплексорами 43, 44, 46 с регистра микрокоманд. Адресация блоков регистров и адресных регистров определяется уровнем приоритета исполняемой микропрограммы (тем самым достигается

5 разбиение этих ресурсов по уровня приоритета) и содержимым регистра микрокоманд. Адресация ячеек оперативной памяти и регистров блоков сопряжения может осуществляться как по содержимому адресного

0 регистра (вход ДО мультиплексора 19), так и непосредственно по содержимому регистра ммкрокоанды, При этом непосредственная адресация обеспечивает доступ к ячейке оперативной памяти внутри группы, закреп5 ленной за блоком сопряжения, номер которого определяется старшими разрядами адресного регистра (на вход Д1 мультиплексора поступают старшие разряды регистра адреса и содержимое регистра микроко0 манд с выхода мультиплексора 11). Адресация и управление однопортовыми элементами устройства, такими как регистры адреса, оперативная память, блоки сопряжения, осуществляется с регистра

5 микрокоманд через мультиплексор 11 управления, обеспечивая независимую адресацию и управление перечисленными элементами в первом и втором полутактах. На шину 28 данных в полутакте чтения мо0 жет быть выдано значение только одного из подключенных к ней блоков. Это определяется сигналами управления с регистра 5 микрокоманд и тактовым сигналом, поступающим на вход блоков 6, 15, 18, 21. Муль5 таплексор 21 выполняет роль электрической развязки внутренней шины данных и шины данных блоков 6 сопряжения.

Таким образом, на входах ДО, Д1 блока 49 формируются значения операндов, на вход INS блока 49 с регистра 5 микрокоманд

поступает значение инструкции, а на вход CR поступает значение входного переноса. Инструкции, выполняемые блоком 49, аналогичны инструкциям интегральной микро- схемы 133ЙПЗ. Значение входного переноса поступает на вход CR блока 49 с регистра 20 признаков результата под управлением сигналов с регистра 5 микроко- манд(на элементе 48 И). На выходе блока 49 формируется результат операции (выход Д) и призна и результата (выход CR, Z). Результат операции всегда в полутакте записи выдается на шину 28 данных и записывается либо в регистр данных блока 10, либо в регистр адреса блока 15, либо в ячейку памяти блока 18, либо з регистр 74 или 75 блока сопряжения. Запись в один из указанных элементов осуществляется под управлением сигналов с выхода регистра 5 микрокоманд. Формируемые на выходе блока 49 признаки результата через мультиплексор 16 признаков результата поступают на регистр 20 признаков и на стек 17 регистров признаков результата и запоми- наются в них. Занесение в регистр 20 осуществляется по положительном/ перепаду тактового сигнала, а в стек 17 регистров - по отрицательному значению тактового сигнала. Управление мультиплексором 16 при- знаков результата и занесение в регистры 17 и 20 признаков результата осуществляется сигналами с регистра 5 микрокоманд.

Путем выполнения микрокоманд обработки и пересылки информации, таким об- разом, можно осуществить пересылку информации между регистром 5 микрокоманд (только источник), регистром 10 данных, регистром 15 адреса, ячейками оперативной памяти 18 и регистрами 66,67, 74,75 блоков 6 сопряжения, а также произвести обработку информации в указанных регистрах и ячейках с записью результата операции в них и в регистры 17 и 20 признаков результата.

Микрокоманды условных и безусловных переходов изменяют последовательность выполняемых микрокоманд. Это происходит следующим образом. При выполнении микрокоманд обработки и пересылки информации адрес следующей микрокоманды получаются инкремента- цией (на сумматоре 35) адреса текущей мик- рокоманды, затем запоминается по положительному перепаду тактового сигнала на регистре 38 и через мультиплексоры 39 и 40 поступает на адресный вход блока 4 памяти микрокоманд. Содержимое блока 4, соответствующее адресу микрокоманды по положительному перепаду тактового сигнала, запоминается на регистре 5 микрокоманд и определяет значение выполняемой

микрокоманды.

Пои выполнении микрокоманд обработки значение сигнала на входе ДСЕ мультиплексора 39 равно нулю и определяет прохождение кода с входа ДО на его выход. Это достигается тем, что сигналы управление с выхода регистра 5 микрокоманд на входе ДСЕ мультиплексора 37 определяют прохождение значения 0В со входа на его ВИУОД. При выполнении микрокоманды перехода сигналы управления на входе ДСЕ мультиплексора 37 определяют прохождение значений одного из признаков результата либо значения 5В на его выход. При этом s случае появления на выходе мультиплексора 37 значения логической единицы мультиплексор 39 переключается и пропускает со входа Д1 (с шины 38 данных) на его выход. Это состояние мультиплексора 39 определяет выполнение микрокоманды перехода. Состояние мультиплексоров 36 и 40 при этом соответственно закрыт и открыт. Адрес перехода формируется на шине 38 данных в полутакте записи так же, как и в микрокомандах обработки и пересылки информации. При прохождении на выход мультиплексора 37 значения 5В выполняются микрокоманды безусловного перехода, а при прохождении на выход мультиплексора признаки результата с выхода регистра 20 признаков выполняются микрокоманды условного перехода по этому признаку.

Микрокоманды прерывания и возврата из прерывания предназначены для перехода к исполнению более приоритетной микропрограммы с сохранением параметров текущей и для возврата к исполнению прерванной микропрограммы с восстановлением параметров. Прерывание происходит при выдаче блоком сопряжения по шине 31 запроса большего приоритета, чем приоритет исполняемой микропрограммы. При зтом на выходе INR узла 41 прерывания (имеется в виду микросхема типа 589ИК14) синхронно с тактом выполнения микрокоманд формируется отрицательный сигнал. Этот сигнал возникает на фоне выполнения последней (перед прерыванием) микрокоманды прерываемой микропрограммы и воздействует на блок 3 адресации памяти микрокоманд следующим образом:

запрещает инкрементацию адреса следую дей микрокоманды (вход Е + 1 сумматора 35),

закрывает мультиплексор 40 и открывает мультиплексор 36, определяя код О на входе адреса памяти микрокоманд.

Таким образом, следующей будет исполнена микрокоманда, выбранная поадресу О, а в регистре адреса 38 во время .выполнения этой нулевой команды будет храниться адрес микрокоманды, выборка которой была прекращена сигналом INR, т.е. микрокоманды, к которой надо будет перейти при возврате к исполнению прерванной микропрограммы. По адрес О в памяти микрокоманд находится специальная микрокоманда выполнения прерывания. Эта микрокоманда:

разрешает узлу 41 прерывания выдачу кода нового уровня приоритета;

определяет узлу 41 необходимость записи этого нового кода в свой внутренний регистр текущего уровня приоритете;

выдает сигнал на вход Е дешифратора 12, активизируя тем самым сигнал на шине 32 разрешения прерывания к одному из блоков 6 сопряжения;

определяет выполнение действий микрокоманды безусловного перехода по адресу, формируемому в блоке сопряжения;

определяет в первом полутакте запись в стек 2 регистров адреса микрокоманд значения с регистра 38 адреса микрокоманд; инкрементацию указателя стека (счетчика 1), а затем во втором полутакте запись в стек 7 регистров уровня приоритета новэго значения уровня приоритета, поступающего из узла 41 прерывания (в стеке признаков результата сохраняются значения признаков прерванной микропрограммы).

Блок б сопряжения, получив сигнал разрешения прерывания, обеспечивает выдачу на шину 34 данных адреса переходе, содержащего причину прерывания и собственный адрес блока 6 сопряжения. Таким образом, обеспечивается переход к исполнению более приоритетной микропрограммы с сохра- нениемпараметров текущей

микропрограммы. При возврате к исполнению прерванной микропрограммы выполняется микрокоманда возврата, которая;

закрывает выдачу значений с регистра 38 блока 3;

осуществляет уменьшение на 1 значение счетчика 1;

осуществляет чтение значения адреса микрокоманды признака результата, уровня приоритета прерванной микропрограммы с выходов соответствующих стеков регистров 2,7, 17;

обеспечивает передачу адресе микрокоманды из стека 2 регистров адреса микрокоманд на вход А памяти 4 микрокоманд;

обеспечивает запись уровня приоритета с выхода стека 7 регистров уровня приоритета во внутренний регистр узла 41 прерывания;

обеспечивает запись признаков результатов с выхода стека 17 регистров признаков результатов в регистр 20 признаков результата.

Таким образом, происходит возврат к исполнению прерванной микропрограммы с восстановлением прерванных парамет0 ров.

Рассмотрим функционирование устройства, обеспечивающего обмен информацией одной ЭВМ с тремя абонентами. За ЭВМ закрепим 2 блока сопряжения. Один 5 с наивысшим уроаенм приоритета - 5, обслуживает обращения к устройству со стороны ЦП, другой - с наименьшим уровнем приоритета - 1, обслуживает обращение устройства к основной памяти и ЦП. Блоки

0 сопряжения с приоритетом 2, 3, 4 за- крепим за отдельными абонентами. Источниками инструкций на обмен могут быть как ЭВМ, так и абоненты, Выполнение каждой инструкции распадается на выполнение от5 дельных процедур. Каждая процедура инструкции закреплена на каким-либо одним блоком 6, реализует взаимодействие с ним и выполняется на уровне приоритета, присвоенном этому блоку. Переход от процеду0 ры к процедуре происходит путем установки заявки в очередь к следующей процедуре и активизации этой процедуры при обнаружении заявки в очереди. Множество процедур,

5 реализующие все возможные инструкции, поступающие к устройству от ЭВМ и абонентов, разбивается на группу, закрепленные за различными блоками сопряжения. Таким образом, за каждым блоком со0 пряжения закрепляется некоторое множество процедур, выполнение которых позволяет обеспечить все возможные режимы взаимодействия с ЭВМ или абонентами, подключенными к этому блоку. При необхо5 димости передачи управления одной из них активизирующая процедура в специально выделенном для каждого блока б сопряжения управляющем массиве запоминающего блока устанавливает заявку на исполнение

0 требуемой процедуры и взводит триггер 65 этого блока сопряжения. При получении вызванного единичным значением триггера 65 прерывания устройство анализирует путем выполнения последовательности микроко55 манд эти заявки, выбирает наиболее приоритетную и приступает к ее исполнению.

В процессе выполнения процедуры при необходимости ожидания ответа от ЭВМ или абонента устройство передает управление процедурой блоку сопряжения и может

гкэрейти к выполнению других процедур, не

связанных с активизированным блоком сопряжения.

При получении активизированным блоком сопряжения ответа от ЭВМ или абонента (или исчерпании регламентированного интервала ожидания), он взводит триггер 64 и формирует прерывание, сопровождая его вектором, характеризующим его номер и причину прерывания.

К процедурам блоков с различными приоритетами при выполнении нескольких инструкций мог/т возникать очереди, Очередь к каждой процедуое представляет из себя вектор битов, единичные значения которых определяют номера блоков сопряжения, требующих выполнения данной процедуры. Приоритетность требований блоков сопряжения растет с увеличением номера блока. Номер блока сопряжения, взаимодействие с которым осуществляется данной микропрограммой, располагается в старших разрядах регистрах адреса, ском- мутированных с выхода Д1 блока 15 регистров адреса на третий вход блока 14 обработки очередей. При выполнении микрокоманд коррекции очередей содержимое этого регистра адреса с помощью сигналов с регистра микрокоманд выдается на выход Д1 блока 15. Блок 14 обработки очередей выполняет две функции: дешифрацию на дешифраторе 56 номера блока сопряжения, поступающего с выхода Д1 блока регистров адреса, и нахождение номера левой единицы операнда, поступающего на второй вход блока с шины 28 данных. Схема формирования номера левой единицы входного операнда состоит из элемента И и ИЛИ. На фмг.б приведен пример схемы для восьмиразрядного входного операнда.

Коррекция очередей (установка и стирание битов, соответствующих обрабатываемому блоку сопряжения) осуществляется путем выполнения следующей микрокоманды:

(ячейка очереди): (ячейка очереди) {F} N БС,

где N БС - номер блока сопряжения с выхода Д1 блока 15, преобразованный путем дешифрации на дешифраторе 56;

F-функция АЛУ, используемая при коррекции очередей;

Av5 - при установке заявки в очередь

МБ - при стирании заявки из очереди.

Выбор заявок из очереди выполняется путем исполнения следующей микрокоманды:

(RA): (ячейка очереди), где А - регистр адреса содержащий номер блока сопряжения;

(ячейка очереди) - номер левой единицы кода, содержащегося в анализируемой ячейке очереди.

Формула изобретения 1. Устройство для обмена информацией.

содержащее первый блок сопряжения, группы информационных и управляющих входов и выходов которого являются соответственно группами информационных и управляю0 щмх входов и выходов устройства, тактовый генератор, блок приоритета, информационный вход которого подключен к выходу запроса на прерывание первого блока сопряжения, блок адресации памяти микро5 команд объединен с тактовым входом блока приоритета, выход блок адресации памяти микрокоманд подключен к адресному входу блокз памяти микрокоманд, входы разрешения блока управления, блока регистров ад0 реса, блока оперативной памяти, блока адресации памяти микрокоманд и первого блока сопряжения подключены к выходу блока памяти микрокоманд, тактовый вход блока регистров данных объединен с такто5 вым входом первого блока сопряжения, ин- формзционный вход блокз регистров даннчх подключен к выходу блока оперативна памяти, алоесный которого объединен с адресно м входом первого бло0 кз сопряжения, отличающееся тем, что, с целью расширения области применения за счет использования в системах реаль- ного зоемени и повышения производитетьности, в него введены четыре

5 мультиплексора, М-1 блоков сопряжения, счетчик, стек регистров адреса, стек регистров уровня приоритета, стек регистров признаков результата, дешифратор, блок обработки очередей, регистр признаков ре0 зультата, причем информационные и управ- ляющие входы и аыходы М-1 блоков сопряжения являются информационными и управляющими входами и выходами устройства, а выходы запросов на прерывание

5 - подключены к информационным входам блока приоритета, разрешающие, тактовые и адресные входы М-1 блоков сопряжения объединены с одноименными входами первого блока сопряжения, выходы дешифрато0 ра подключены ко входам разрешения прерывания № блоков сопряжения, вход данных дешифратора подключен к выходу бло.чз приоритета, первый выход которого подключен к входу признака такта прерыва5 ни т блика адресации памяти микрокоманд. выход стека регистров уровня приоритета подключен к первому адресному входу блока регистров данных, к информационному входу дешифратора и первому адресному входу блока регистров адреса, тактовые входы счетчика, стека регистров адреса, стека регистров уровня приоритета, блока управления, стека регистров признаков результата и первого - четвертого мультиплексоров, блока регистров адреса, блока оперативной памяти, блока памяти микрокоманд, блока адресации памяти микрокоманд подключены к выходу тактового генератора, разрешающие входы стека ре гистров уровня приоритета, счетчика, стека регистров адреса, стека регистров признаков результата, регистра признаков результата, с первого по четвертый мультиплексоров, блока обработки очередей, блока приоритета и блока регистров данных объединены и подключены к выходу блокз памяти микрокоманд, вход адреса стека регистров адреса, стека регистров уровня приоритета и стека регистров признаков результата объединены и подключены к выходу счетчика. выход стека регистров адреса подключен к адресному входу блока адресации памяти микрокоманд, вход признака результата которого соединен с выходами блока упраале- ния и регистра признаков результата, вход данных которого подключен к объединенным выходам стека регистров признаков результата и второго мультиплексора, вход данных которого подключен к выходу результата операции блока управления, пер вый и второй входы данных которого подключены соответственно к первому w второму выходам блока регистров данных, третий вход данных блока управпения под|-

ключен к выходу блока обработки очередей, первый информационный вход которого, информационный вход блока адресации памяти микрокоманд, четвертый вход данных

блока управления соединены с выходом блока управления, с первым выходом блока регистров адреса и первого мультиплексора и выходом блока оперативной памяти, второй выход первого мультиплексора подключей к входам данных М блоков сопряжения, второй информационный вход блока обработки очередей и информационный вход третьего мультиплексора подключены к выходу блока регистров адреса, вход адреса которого подключен к аыходу четвертого мультиплексора и входу управления третьего мультиплексора.

20

25

30

35

2, Устройство поп,1,отличающее- с я тем, что блок обработки очередей содержит дешифратор, мультиплексор, группу элементов И и группу элементов ИЛИ, выходы которых подключены к первому входу мультиплексора, выход которого явлйется выходом блока, первый информационный вход блока подключен к входам элементов А группы и к первым входам элементов ИЛИ группы, выходы элементов И группы подключены к вторым входам элементов ИЛИ группы, второй информационный вход блока подключен к входу дешифратора, выход которого подключен к второму входу данных мультиплексора, вход управления которого является разрешающим входом блока.

N

I

omSa.10

6л.®

от fa 18

omf/t.5

от 6п.%

от 6Л20

Фиг. 5

52

V

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство для обмена информацией | 1982 |

|

SU1059561A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1278846A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1397908A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения между собой абонентов и ЭВМ, входящих в состав вычислительного комплекса, работающего в реальном масштабе времени. Целью изобретения является расширение области применения и увеличение производительности. Устройство содержит счетчик, стек регистров адреса, блок адресации памяти микрокоманд, блок памяти микрокоманд, регистр микрокоманд, блоки сопряжения, стек регистров уровня приоритета, тактовый генератор, блок приоритета, блок регистров данных, мультиплексор управления, дешифратор, блок управления, блок обработки очс эе.ей, блок регистров адреса, мультиплексор признаков результата, стек регистров признаков результата, блок оперативной памяти, мультиплексор адреса, регистр признаков результата, мультиплексор данных. 1 з.п. ф-лы, 7 ил.

| Процессор ввода-вывода | 1980 |

|

SU934465A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена информацией | 1982 |

|

SU1059561A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-30—Публикация

1989-05-22—Подача