О 4 ЧЭ

VI

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано для анализа формы детерминированных и спучайных импульсных и частотных сигналов.

Цель изобретения - расширение функциональных возможностей устройства за счет динамического отображения сигнала или его огибающей, длительность которых превышает время отображения на экране средства отображения осциллографического типа.

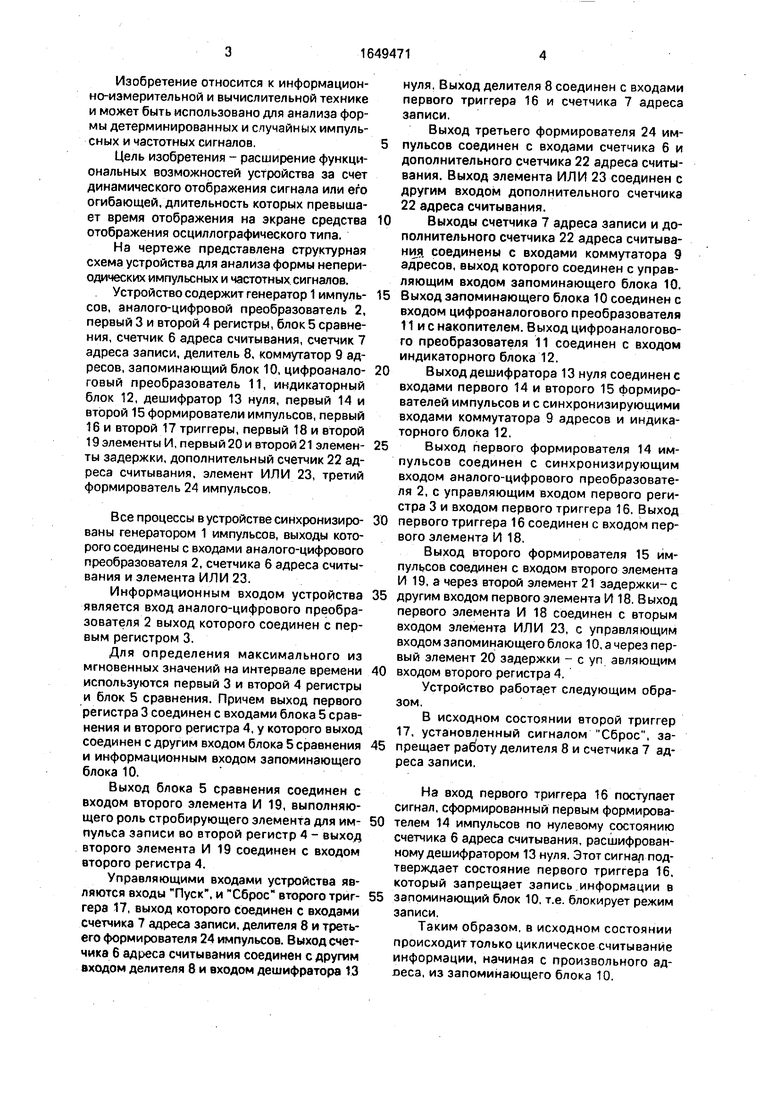

На чертеже представлена структурная схема устройства для анализа формы непериодических импульсных и частотных сигналов.

Устройство содержит генератор 1 импуль- сов, аналого-цифровой преобразователь 2, первый 3 и второй 4 регистры, блок 5 сравнения, счетчик 6 адреса считывания, счетчик 7 адреса записи, делитель 8, коммутатор 9 адресов, запоминающий блок 10, цифроанало- говый преобразователь 11, индикаторный блок 12, дешифратор 13 нуля, первый 14 и второй 15 формирователи импульсов, первый 16 и второй 17 триггеры, первый 18 и второй 19 элементы И, первый 20 и второй 21 элемен- ты задержки, дополнительный счетчик 22 адреса считывания, элемент ИЛИ 23, третий формирователь 24 импульсов.

Все процессы в устройстве синхронизиро- ваны генератором 1 импульсов, выходы которого соединены с входами аналого-цифрового преобразователя 2, счетчика 6 адреса считывания и элемента ИЛИ 23.

Информационным входом устройства является вход аналого-цифрового преобразователя 2 выход которого соединен с первым регистром 3.

Для определения максимального из мгновенных значений на интервале времени используются первый 3 и второй 4 регистры и блок 5 сравнения. Причем выход первого регистра 3 соединен с входами блока 5 сравнения и второго регистра 4, у которого выход соединен с другим входом блока 5 сравнения и информационным входом запоминающего блока 10.

Выход блока 5 сравнения соединен с входом второго элемента И 19, выполняющего роль стробирующего элемента для им- пульса записи во второй регистр 4 - выход второго элемента И 19 соединен с входом второго регистра 4.

Управляющими входами устройства являются входы Пуск, и Сброс второго триг- гера 17, выход которого соединен с входами счетчика 7 адреса записи, делителя 8 и третьего формирователя 24 импульсов. Выход счетчика 6 адреса считывания соединен с другим входом делителя 8 и входом дешифратора 13

нуля. Выход делителя 8 соединен с входами первого триггера 16 и счетчика 7 адреса записи.

Выход третьего формирователя 24 импульсов соединен с входами счетчика 6 и дополнительного счетчика 22 адреса считывания. Выход элемента ИЛИ 23 соединен с другим входом дополнительного счетчика 22 адреса считывания.

Выходы счетчика 7 адреса записи и дополнительного счетчика 22 адреса считывания соединены с входами коммутатора 9 адресов, выход которого соединен с управляющим входом запоминающего блока 10. Выход запоминающего блока 10 соединен с входом цифроаналогового преобразователя 11 и с накопителем. Выход цифроаналогового преобразователя 11 соединен с входом индикаторного блока 12.

Выход дешифратора 13 нуля соединен с входами первого 14 и второго 15 Формирователей импульсов и с синхронизирующими входами коммутатора 9 адресов и индикаторного блока 12.

Выход первого формирователя 14 импульсов соединен с синхронизирующим входом аналого-цифрового преобразователя 2, с управляющим входом первого регистра 3 и входом первого триггера 16. Выход первого триггера 16 соединен с входом первого элемента И 18,

Выход второго формирователя 15 импульсов соединен с входом второго элемента И 19, а через второй элемент 21 задержки- с другим входом первого элемента И 18. Выход первого элемента И 18 соединен с вторым входом элемента ИЛИ 23, с управляющим входом запоминающего блока 10, а через первый элемент 20 задержки - с уп авляющим входом второго регистра 4.

Устройство работает следующим образом.

В исходном состоянии второй триггер 17, установленный сигналом Сброс, запрещает раЕюту делителя 8 и счетчика 7 адреса записи.

На вход первого триггера 16 поступает сигнал, сформированный первым формирователем 14 импульсов по нулевому состоянию счетчика б адреса считывания, расшифрованному дешифратором 13 нуля. Этот сигнал подтверждает состояние первого триггера 16, который запрещает запись информации в запоминающий блок 10. т.е. блокирует режим записи.

Таким образом, в исходном состоянии

происходит только циклическое считывание информации, начиная с произвольного ад- веса, из запоминающего блока 10.

При переключении второго триггера 17 разрешается счет делителю 8 и счетчику 7 адреса записи, что, в свою очередь, разрешает последовательную запись в ячейки запоминающего блока 10 вычисленных дискретных значений огибающей частотно-модулированного или непериодического импульсного входного сигнала. Вычисление дискретных значений входного сигнала осуществляется при помощи аналого-цифрового преобразо- вателя 2, первого 3 и второго 4 регистров, блока 5 сравнения и второго элемента И 19. Частотно-модулированный сигнал обрабатывается по алгоритму нахождения максимального из мгновенных значений входного сигнала за интервал времени Лт.Мп. Полученные с выхода аналого-цифрового преобразователя 2 кодовые эквиваленты мгновенных значений амплитуд входного сигнала записываются в первый регитср 3, после чего произво- дится сравнение его содержимого с содержимым второго регистра 4 в блоке 5 сравнения.

Если код, записанный в первом регистре 3, больше, чем код во втором регистре 4. он переписывается во второй регистр 4. В противном случае во втором регистре 4 остается предыдущее значение. Таким образом, к концу интервала Дт.зап во втором регистре 4 будет находиться максимальное мгновенное значение. Второй элемент И 19 выполняет роль стробирующего элемента для импульса записи во второй регистр 4 с выхода второго формирователя 15 импульсов. Перед началом вычисления очередного максимального значения второй регистр 4 приводится в нулевое состояние.

Все процессы в устройстве синхронизированы частотой генератора 1 импульсов. Для получения управляющих сигналов используются первый 14 и второй 15 формирователи коротких импульсов, работающие соответственно по заднему и переднему фронтам выходного сигнала дешифратора 13 ну- ля. Процессы управления и синхронизации распределены в устройстве так, что в момент установки нулевого такта счетчика 6 адреса считывания на выходе второго формирователя 15 коротких импульсов форми- руется импульс для стробирования второго элемента И 19, который обеспечивает в случае необходимости запись большего мгновенного значения во второй регистр 4. Он же, задержанный на втором элементе 21 задержки, поступает на вход первого элемента И 18, и в случае, если первый триггер 16 будет находиться в единичном состоянии, происходит перезапись вычисленного

максимального значения из второго регистра 4 в запоминающий блок 10, а после некоторой задержки сбрасывается в нулевое состояние второй регистр 4.

По команде Пуск третий формирователь 24 коротких импульсов устанавливает в нулевое состояние счетчики б и 22 адресов считывания. При этом счетчики работают синхронно до момента записи информации в запоминающий блок 10. Одновременно с управляющим сигналом на запись информации в запоминающий блок 10 на вход дополнительного счетчика 22 адреса считывания с выхода первого элемента 18 поступает дополнительный импульс. Таким образом, считывание информации из запоминающего блока 10 производится со сдвигом на один такт после каждой записи по отношению к синхронизирующему сигналу на индикаторный блок 12, снимаемому с выхода дешифратора 13 нуля при нулевом состоянии счетчика 6 адреса считывания.

Первый триггер 16 устанавливается в единичное состояние при смене адреса записи, так как его счетный вход объединен со счетным входом счетчика 7 адреса записи. Сброс первого триггера 16, запись преобразованной входной информации в первый регистр 3 и синхронизация аналого-цифрового преобразователя 2 производится в момент окончания нулевого такта счетчика 6 адреса считывания по импульсу с выхода первого формирователя 14 коротких импульсов.

Режим записи информации в ячейки запоминающего блока 10 и циклического опроса ячеек (в режиме считывания) осуществляется с помощью счетчика 6 адреса считывания, дополнительного счетчика 22 адреса считывания, делителя 8, счетчика 7 адреса записи и коммутатора 9 адресов.

Коммутатор 9 адресов подключает к адресным шинам запоминающего блока 10 коды адресов считывания и записи соответственно с выходов дополнительного счетчика 22 адреса считывания и счетчика 7 адреса записи.

Делитель 8 обеспечивает требуемую частоту записи информации в запоминающий блок 10.

Подключение адреса записи к адресной шине запоминающего блока 10 производится на нулевом адресе счетчика 6 адреса считывания, расшифровываемом при помощи дешифратора 13 нуля, что позволяет упростить формирование управляющих сигналов и не сказывется на качестве отображения, так как индикаторный блок 12 в это время может находиться в режиме обратного хода луча (гашение луча).

По мере записи информации в запоминающий блок 10 разность содержимого счетчиков 6 и 22 адреса считывания увеличивается. Это позволяет обеспечивать динамический характер отображения информации. Изображение записанной информации визуально продвигается по экрану справа налево, при этом записанное значение отображается в крайней левой части экрана индикаторного блока 12.

Необходимый аналоговый сигнал для индикаторного блока 12 формируется при помощи цифроаналогового преобразователя 11, подключенного к информационному выходу запоминающего блока 10.

После заполнения всех ячеек запоминающего блока 10 информация будет продолжать записываться с нулевой ячейки, стирая ранее записанные значения.

Режим записи блокируется при подаче управляющего сигнала Сброс на второй триггер 17. Циклическое считывание информации будет продолжаться, но из-за того, что формирование и установка адреса сдвига будут прекращены (так как они взаимосвязаны с процессом записи), на индикаторном блоке 12 отображение записанной информации примет статический характер.

Формула изобретения

Устройство для анализа формы непериодических импульсных и частотных сигналов, содержащее генератор импульсов, аналого- цифровой преобразователь, первый и второй регистры, блок сравнения, счетчики адресов считывания и записи, делитель, коммутатор адресов, запоминающий блок, цифроанало- говый преобразователь, индикаторный блок, дешифратор нуля, первый и второй формирователи импульсов, первый и второй триггеры, первый и второй элементы И, первый и второй элементы задержки, при этом выход генератора импульсов соединен с первыми входами счетчика адреса считывания и аналого-цифрового преобразователя, второй вход которого соединен с информационным входом устройства, а выход соединен с первым входом первого регистра, выход первого регистра соединен с первыми входами второго регистра и блока сравнения, выход блока сравнения соединен с первым входом второго элемента И, выход которого соединен с вторым входом второго регистра, выход которого соединен с вторым входом блока

сравнения и первым входом запоминающего блока, второй вход запоминающего блока соединен с выходом коммутатора адресов, первый вход коммутатора адресов соединен

с выходом счетчика адреса записи, первый вход которого соединен с первым входом первого триггера и с выходом делителя,первый вход делителя соединен с входом дешифратора нуля и с выходом счетчика

адреса считывания, выход дешифратора нуля соединен с вторым входом коммутатора адресов, с первым входом индикаторного блока, входами первого и второго формирователей импульсов, выход первого формирователя импульсов соединен с третьим входом аналого-цифрового преобразователя и вторыми входами первого регистра и первого триггера, выход первого триггера соединен с первым входом первого элемента И,

выход первого элемента И соединен с третьим входом запоминающего блока и через первый элемент задержки с третьим входом второго регистра, а второй вход первого элемента И соединен с выходом второго элемента задержки, вход которого соединен с вторым входом второго элемента И и выходом второго формирователя импульсов, кроме этого выход запоминающего блока соединен с накопителем и соединен с входом цифроаналогового преобразователя, выход которого соединен с вторым входом индикаторного блока, а первый управляющий вход Пуск устройства соединен с входом второго триггера,выход которого

соединен с вторыми входами делителя и счетчика адреса записи, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены дополнительный счетчик адреса считывания, э. .амент ИЛИ

и третий формирователь импульсов, при этом выход генератора импульсов соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И. а выход - с первым входом дополнительногосчетчика адреса считывания, у которого выход соединен с третьим входом коммутатора адресов, вторые входы счетчика и дополнительного счетчика адреса считывания соединены с выходом третьего формирователя импульсов, вход которого соединен с выходом второго триггера, второй вход которого соединен с вторым управляющим входом Сброс устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для анализа формы непериодических импульсных и частотных сигналов | 1982 |

|

SU1075196A1 |

| Устройство для анализа формы огибающей частотного сигнала | 1987 |

|

SU1524013A1 |

| Устройство для анализа формы непериодических импульсных и частотных сигналов | 1984 |

|

SU1187103A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Информационно-измерительное устройство | 1985 |

|

SU1256074A1 |

| Устройство для отображения формы регистрируемого процесса | 1978 |

|

SU746188A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Измерительный прибор | 1989 |

|

SU1661653A1 |

Устройство относится к информационно-измерительной и вычислительной технике и может быть использовано для анализа формы детерминированных и случайных импульсных и ЧМ-сигналов. Цель изобретения- расширение функциональных возможностей устройства. Устройство отличается наличием дополнительного счетчика 6 адреса считывания, элемента ИЛИ 23 и третьего формирователя 24 импульсов, что позволяет расширить функциональные возможности путем организации режима динамического отображения в реальном масштабе времени. Организация режима динамического отображения позволяет осуществлять визуальный контроль сигнала или его огибающей, длительность которых превышает время отображения сигнала на экране осциллографического типа. Кроме того устройство содержит генератор 1 импульсов, аналого-цифровой преобразователь 2, регистры 3 и 4, блок 5 сравнения, счетчик 7 адреса записи, делитель 8, коммутатор 9 адреса, запоминающий блок 10, цифроа- налоговый преобразователь 11, индикаторный блок 12, дешифратор 13 нуля, формирователи 14 и 15 импульсов, триггеры 16 и 17, элементы И 18 и 19, элементы 20 и 21 задержки, счетчик 22 адреса считывания. 1 ил. Ё

| Устройство для анализа формы непереодических импульсных сигналов | 1980 |

|

SU890272A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для анализа формы непериодических импульсных и частотных сигналов | 1982 |

|

SU1075196A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-05-15—Публикация

1988-12-26—Подача