Изобретение относится к вычислительной технике и может быть использовано для ввода экспериментальных данных в ЭВМ, а также в различных информационно-измерительных системах.

Цель изобретения - упрощение устройства.

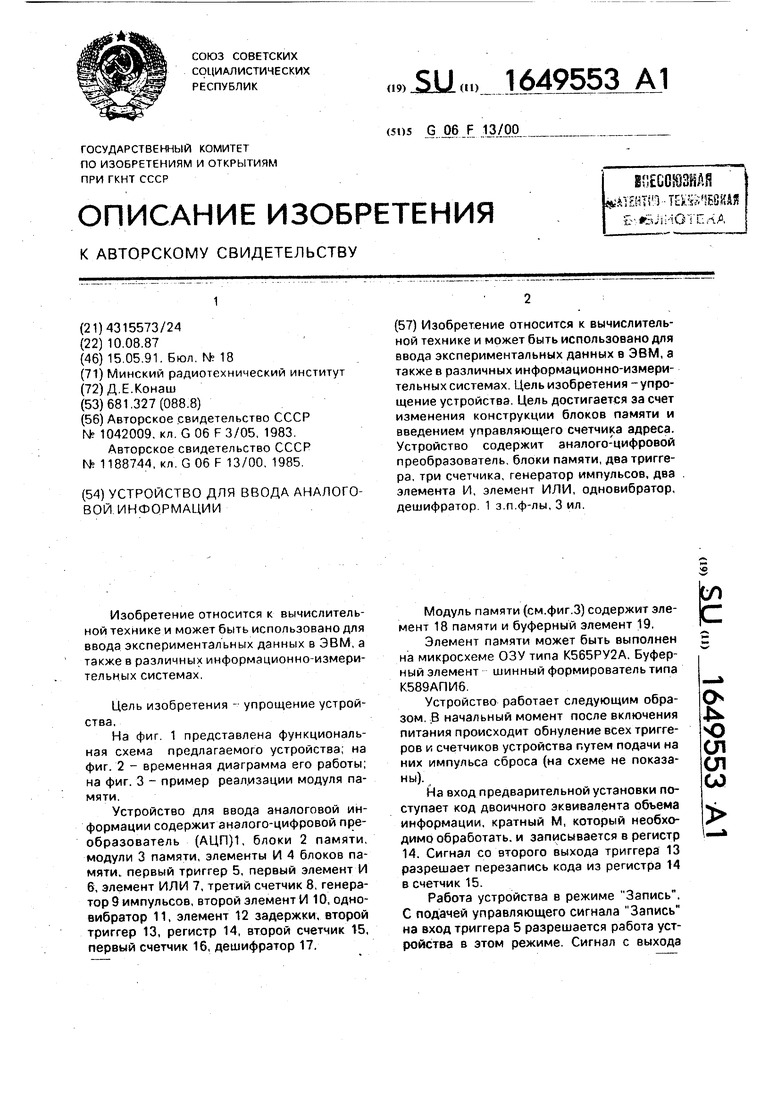

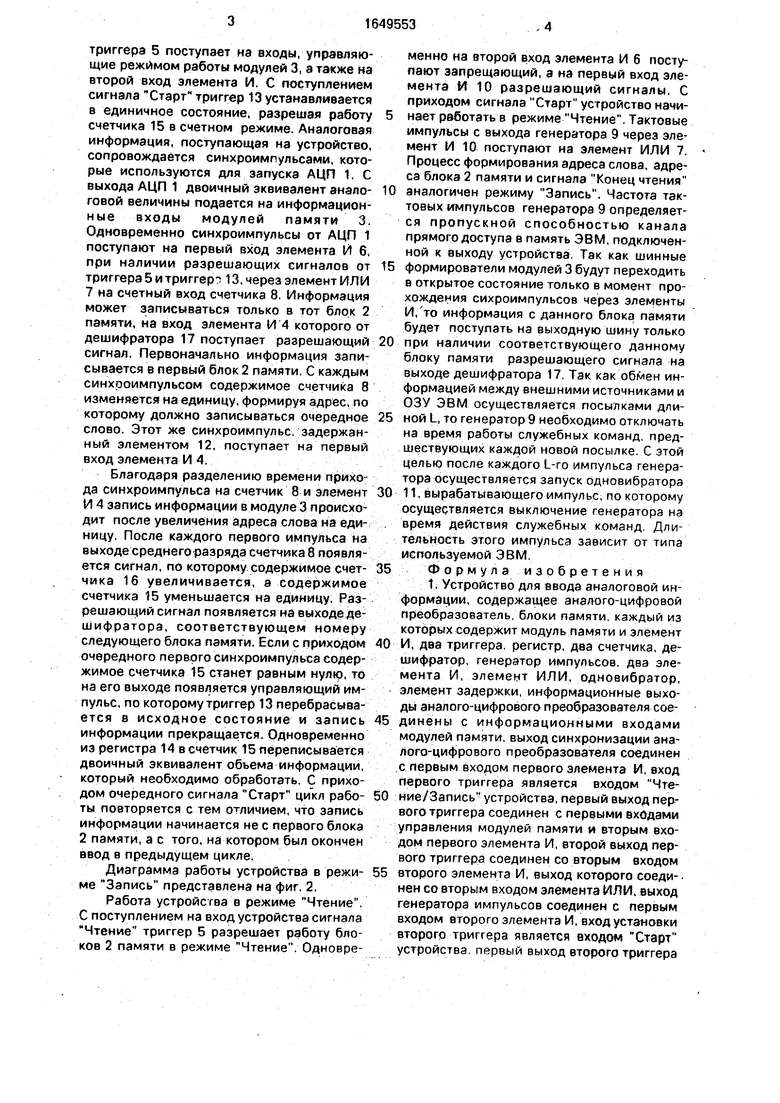

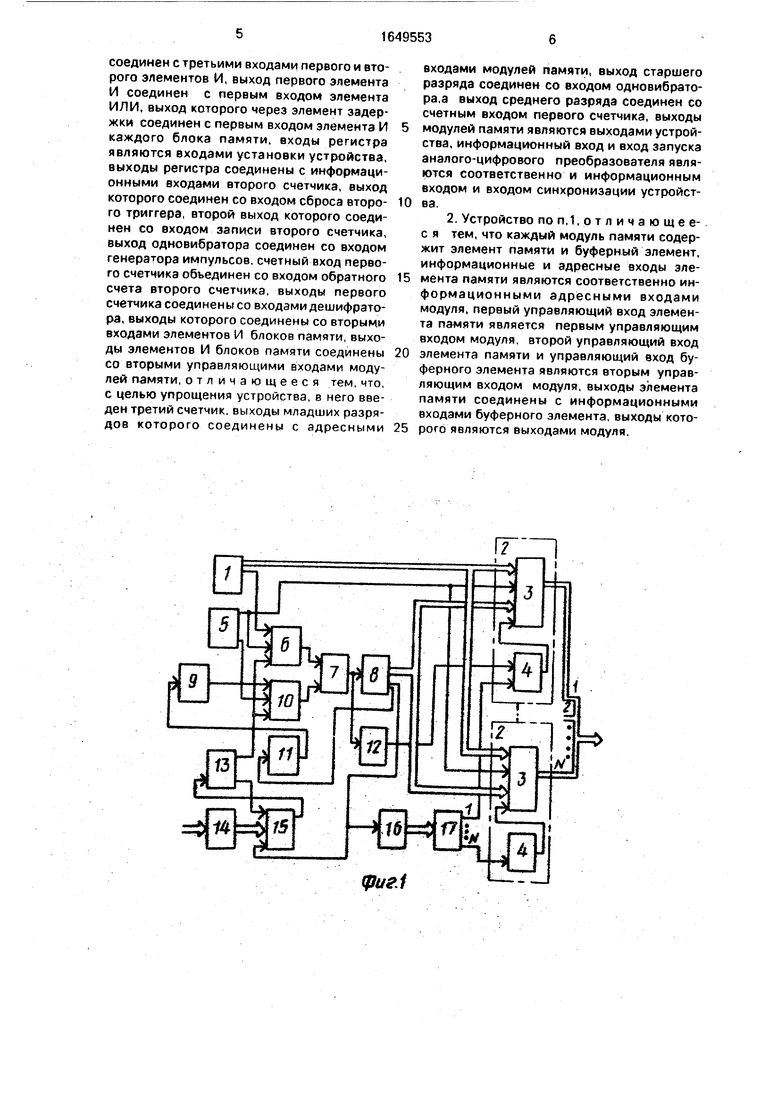

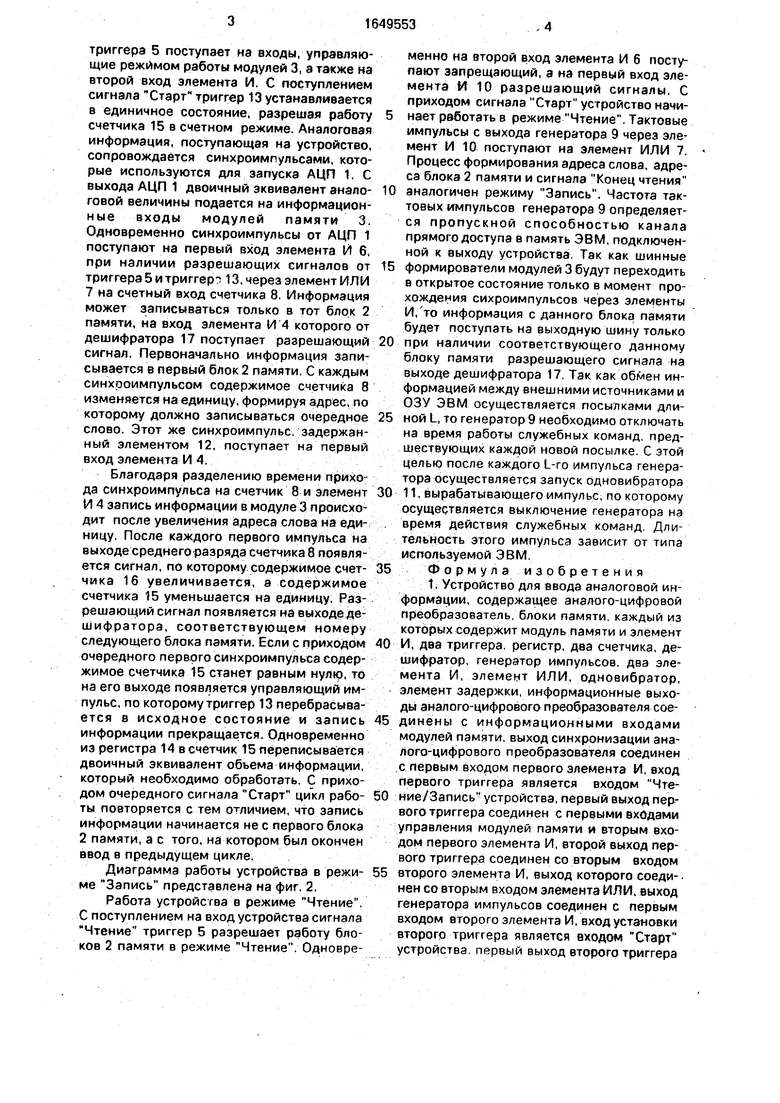

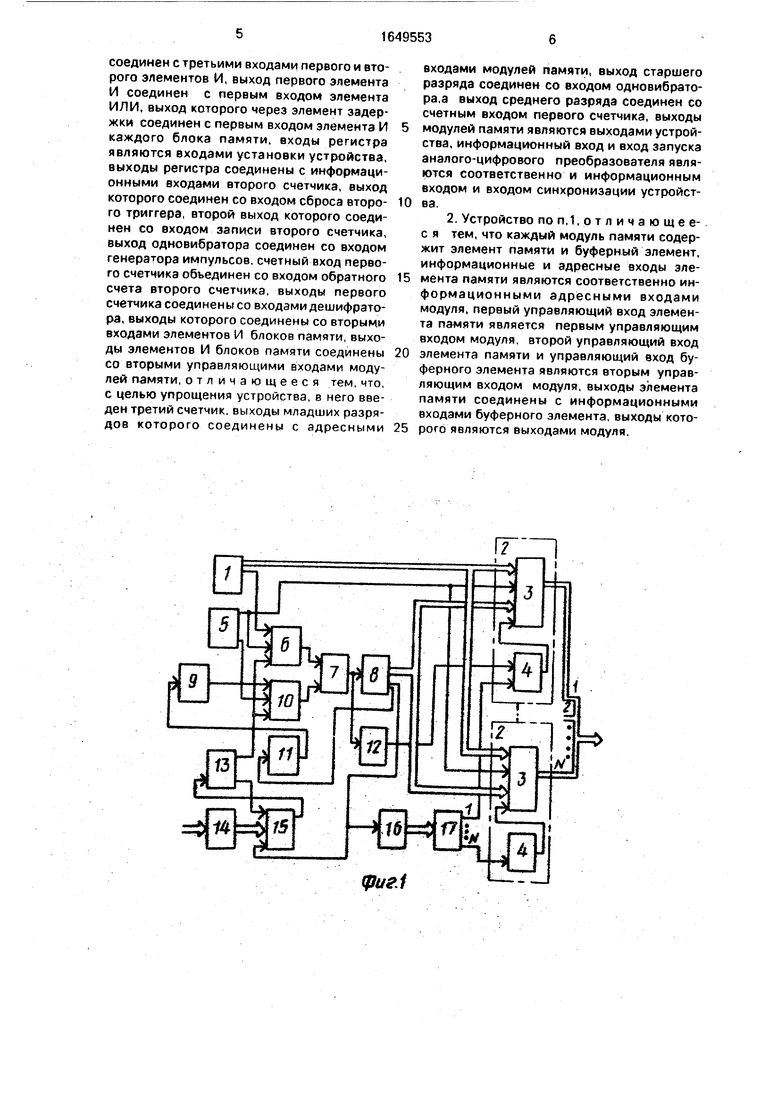

На фиг. 1 представлена функциональная схема предлагаемого устройства, на фиг. 2 - временная диаграмма его работы; на фиг. 3 - пример реализации модуля памяти.

Устройство для ввода аналоговой информации содержит аналого-цифровой преобразователь (АЦП)1, блоки 2 памяти, модули 3 памяти, элементы И 4 блоков памяти, первый триггер 5, первый элемент И 6, элемент ИЛИ 7, третий счетчик 8, генератор 9 импульсов, второй элемент И 10, одно- вибратор 11, элемент 12 задержки, второй триггер 13, регистр 14, второй счетчик 15, первый счетчик 16, дешифратор 17.

Модуль памяти (см.фиг.З) содержит элемент 18 памяти и буферный элемент 19,

Элемент памяти может быть выполнен на микросхеме ОЗУ типа К565РУ2А. Буферный элемент шинный формирователь типа К589АПИ6.

Устройство работает следующим образом. В начальный момент после включения питания происходит обнуление всех триггеров и счетчиков устройства путем подачи на них импульса сброса (на схеме не показаны).

На вход предварительной установки поступает код двоичного эквивалента объема информации, кратный М, который необходимо обработать, и записывается в регистр 14. Сигнал со второго выхода триггера 13 разрешает перезапись кода из регистра 14 в счетчик 15.

Работа устройства в режиме Запись. С подачей управляющего сигнала Запись на вход триггера 5 разрешается работа устройства в этом режиме. Сигнал с выхода

ч

е

О О

ел ел ы

триггера 5 поступает на входы, управляющие режимом работы модулей 3, а также на второй вход элемента И. С поступлением сигнала Старт триггер 13 устанавливается в единичное состояние, разрешая работу счетчика 15 в счетном режиме. Аналоговая информация, поступающая на устройство, сопровождается синхроимпульсами, которые используются для запуска АЦП 1, С выхода АЦП 1 двоичный эквивалент аналоговой величины подается на информэцион- ные входы модулей памяти 3. Одновременно синхроимпульсы от АЦП 1 поступают на первый вход элемента И 6, при наличии разрешающих сигналов от триггера 5 и триггер 13, через элемент ИЛИ 7 на счетный вход счетчика 8. Информация может записываться только в тот блок 2 памяти, на вход элемента И 4 которого от дешифратора 17 поступает разрешающий сигнал. Первоначально информация записывается в первый блок 2 памяти. С каждым синхроимпульсом содержимое счетчика 8 изменяется на единицу, формируя адрес, по которому должно записываться Очередное слово. Этот же синхроимпульс, задержанный элементом 12, поступает на первый вход элемента И 4.

Благодаря разделению времени прихода синхроимпульса на счетчик 8 и элемент И 4 запись информации в модуле 3 происходит после увеличения адреса слова на единицу. После каждого первого импульса на выходе среднего1эазряда счетчика 8 появляется сигнал, по которому содержимое счетчика 16 увеличивается, а содержимое счетчика 15 уменьшается на единицу. Разрешающий сигнал появляется на выходе дешифратора, соответствующем номеру следующего блока памяти. Если с приходом очередного первого синхроимпульса содержимое счетчика 15 станет равным нулю, то на его выходе появляется управляющий импульс, по которому триггер 13 перебрасывается в исходное состояние и запись информации прекращается. Одновременно из регистра 14 в счетчик 15 переписывается двоичный эквивалент объема информации, который необходимо обработать. С приходом очередного сигнала Старт цикл работы повторяется с тем отличием, что запись информации начинается не с первого блока 2 памяти, а с того, на котором был окончен ввод в предыдущем цикле.

Диаграмма работы устройства в режиме Запись представлена на фиг, 2.

Работа устройства в режиме Чтение. С поступлением на вход устройства сигнала Чтение триггер 5 разрешает работу блоков 2 памяти в режиме Чтение. Одновременно на второй вход элемента И 6 поступают запрещающий, а на первый вход элемента И 10 разрешающий сигналы. С приходом сигнала Старт устройство начинает работать в режиме Чтение. Тактовые импульсы с выхода генератора 9 через элемент И 10 поступают на элемент ИЛИ 7. Процесс формирования адреса слова, адреса блока 2 памяти и сигнала Конец чтения

0 аналогичен режиму Запись. Частота тактовых импульсов генератора 9 определяется пропускной способностью канала прямого доступа в память ЭВМ, подключенной к выходу устройства. Так как шинные

5 формирователи модулей 3 будут переходить в открытое состояние только в момент прохождения сихроимпульсов через элементы И/то информация с данного блока памяти будет поступать на выходную шину только

0 при наличии соответствующего данному блоку памяти разрешающего сигнала на выходе дешифратора 17. Так как обмен информацией между внешними источниками и ОЗУ ЭВМ осуществляется посылками дли5 ной L, то генератор9 необходимо отключать на время работы служебных команд, предшествующих каждой новой посылке. С этой целью после каждого L-ro импульса генератора осуществляется запуск одновибратора

0 11, вырабатывающего импульс, по которому осуществляется выключение генератора на время действия служебных команд. Длительность этого импульса зависит от типа используемой ЭВМ.

5 Формула изобретения

1. Устройство для ввода аналоговой информации, содержащее аналого-цифровой преобразователь, блоки памяти, каждый из которых содержит модуль памяти и элемент

0 И, два триггера, регистр, два счетчика, дешифратор, генератор импульсов, два элемента И, элемент ИЛИ, одновибратор, элемент задержки, информационные выходы аналого-цифрового преобразователя сое5 динены с информационными входами модулей памяти, выход синхронизации аналого-цифрового преобразователя соединен с первым входом первого элемента И, вход первого триггера является входом Чте0 ние/3аписьн устройства, первый выход первого триггера соединен с первыми входами управления модулей памяти и вторым входом первого элемента И, второй выход первого триггера соединен со вторым входом

5 второго элемента И, выход которого соеди-. ней со вторым входом элемента ИЛИ, выход генератора импульсов соединен с первым входом второго элемента И, вход установки второго триггера является входом Старт устройства, первый выход второго триггера

соединен с третьими входами первого и второго элементов И, выход первого элемента И соединен с первым входом элемента ИЛИ, выход которого через элемент задержки соединен с первым входом элемента И каждого блока памяти, входы регистра являются входами установки устройства, выходы регистра соединены с информационными входами второго счетчика, выход которого соединен со входом сброса второ- го триггера, второй выход которого соединен со входом записи второго счетчика, выход одновибратора соединен со входом генератора импульсов, счетный вход первого счетчика объединен со входом обратного счета второго счетчика, выходы первого счетчика соединены со входами дешифратора, выходы которого соединены со вторыми входами элементов И блоков памяти, выходы элементов И блоков памяти соединены со вторыми управляющими входами модулей памяти, отличающееся тем, что, с целью упрощения устройства, е него введен третий счетчик, выходы младших разрядов которого соединены с адресными

входами модулей памяти, выход старшего разряда соединен со входом одновибратора.а выход среднего разряда соединен со счетным входом первого счетчика, выходы модулей памяти являются выходами устройства, информационный вход и вход запуска аналого-цифрового преобразователя являются соответственно и информационным входом и входом синхронизации устройства.

2. Устройство поп.1,отличающее- с я тем, что каждый модуль памяти содержит элемент памяти и буферный элемент, информационные и адресные входы элемента памяти являются соответственно информационными адресными входами модуля, первый управляющий вход элемента памяти является первым управляющим входом модуля, второй управляющий вход элемента памяти и управляющий вход буферного элемента являются вторым управляющим входом модуля, выходы элемента памяти соединены с информационными входами буферного элемента, выходы которого являются выходами модуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода аналоговой информации | 1984 |

|

SU1188744A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для обработки видеоинформации | 1986 |

|

SU1322320A1 |

| Устройство для ввода информации | 1987 |

|

SU1529231A1 |

| Устройство для программного управления технологическими процессами | 1987 |

|

SU1495746A1 |

| Телеметрическая система для сбора сейсмической информации | 1989 |

|

SU1728822A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1278869A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

Изобретение относится к вычислительной технике и может быть использовано для ввода экспериментальных данных в ЭВМ, а также в различных информационно-измерительных системах. Цель изобретения -упрощение устройства. Цель достигается за счет изменения конструкции блоков памяти и введением управляющего счетчика адреса. Устройство содержит аналого-цифровой преобразователь, блоки памяти, два триггера, три счетчика, генератор импульсов, два элемента И, элемент ИЛИ, одновибратор, дешифратор 1 з.п.ф-лы, 3 ил.

Г

Фиг 2

| Устройство для ввода аналоговых величин в цифровую вычислительную машину | 1982 |

|

SU1042009A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода аналоговой информации | 1984 |

|

SU1188744A1 |

Авторы

Даты

1991-05-15—Публикация

1987-08-10—Подача