i(21) 4293628/24-24 . (22) 03.08.87 (46) 23.07.89. Бкш. № 27 (72) В. А. Мельников, А. Б. Дигоран, А. Д. Раевский и Ю. М. Бирюков (53) 621.503.55(088.8)

(56)Авторское свидетельство СССР № 1238035, кл. G 05 В 19/19, 1984.

Авторское свидетельство СССР № 1328795, кл. G 05 В 19/417, 1986. (34) УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УП- РАВЛЕН1}Я ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ

(57)Изобретение относится к вычислительной технике и автоматике и может найти применение при построении программируемых контроллеров, устройств и систем программного управления технологическими процессами.

Цель изобретения - расширение области применения на основе реализации динамического останова и продвижения процессов. Устройство ДЛЯ; программного управления содержит бдгок памяти адресов, блок памяти, блок стековой памяти, регистр адреса, счетчик адреса, счетчик длины линейной последовательности нанокоманд, два счетчика глубины стека, счетчик синхронизации, два дешифратора глубины стека, дешифратор синхронизации, два триггера фиксации метки, триггер запуска, триггер установки, два триггера управления, генератор, одновибратор, блок элементов ИЛИ, блок элементов суммы по моду- с лю два, элемента И, ИЛИ, И-НЕ, задерк- ки. 2 ил.

СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления процессами | 1986 |

|

SU1328795A1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Процессор | 1981 |

|

SU962964A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Устройство для ввода информации | 1986 |

|

SU1314326A1 |

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

Изобретение относится к вычислительной технике и автоматике и может найти применение при построении программируемых контроллеров, устройств и систем программного управления технологическими процессами. Цель изобретения - расширение области применения на основе реализации динамического останова и продвижения процессов. Устройство для программного управления содержит блок памяти адресов, блок памяти, блок стековой памяти, регистр адреса, счетчик адреса, счетчик длины линейной последовательности нанокоманд, два счетчика глубины стека, счетчик синхронизации, два дешифратора глубины стека, дешифратор синхронизации, два триггера фиксации метки, триггер запуска, триггер установки, два триггера управления, генератор, одновибратор, блок элементов ИЛИ, блок элементов суммы по модулю два, элемента И, ИЛИ, И-НЕ, задержки. 2 ил.

Изобретение относит ся к автоматике и вычислительной технике и может найти применение при построении программируемых контроллеров устройств и систем программного управления, АСУ технологическими процессами.

Цель изобретения - расширение области применения на основе реализации динамического останова и продвижения процессов.

Сущность изобретения состоит в по- выпении производительности устройства путем оперативного копирования линейной последовательности команд управления и использования их копий в режиме гибкого управления двумя про- процессами.

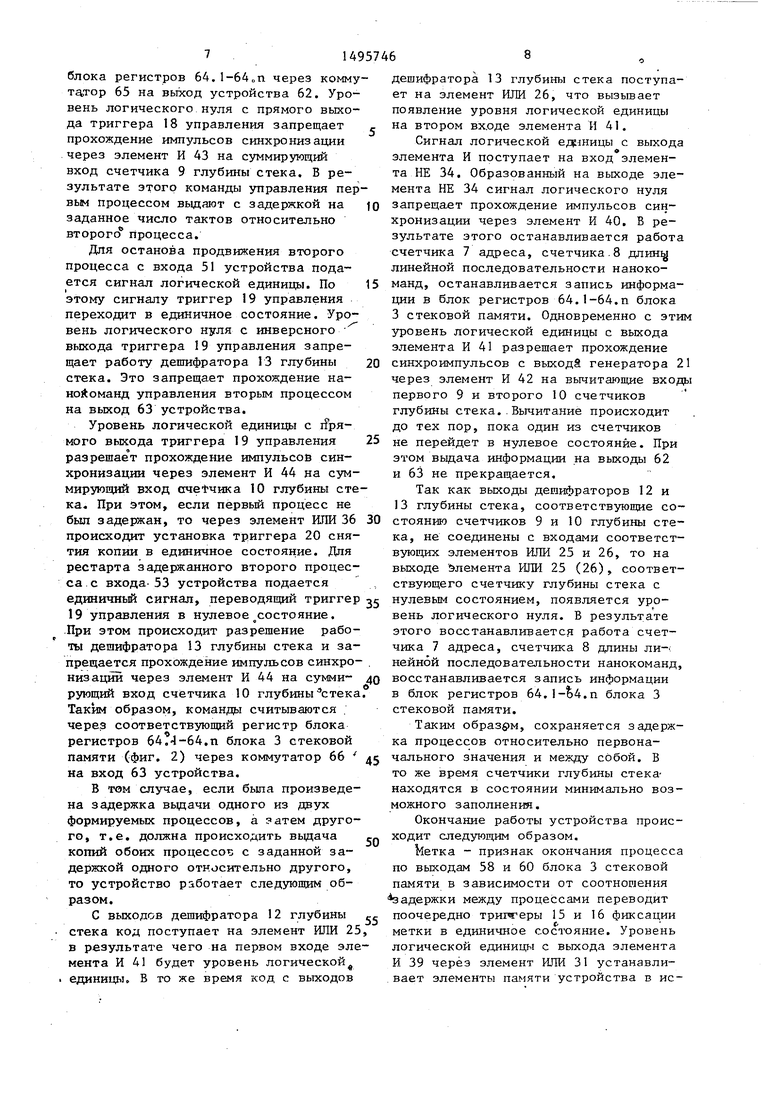

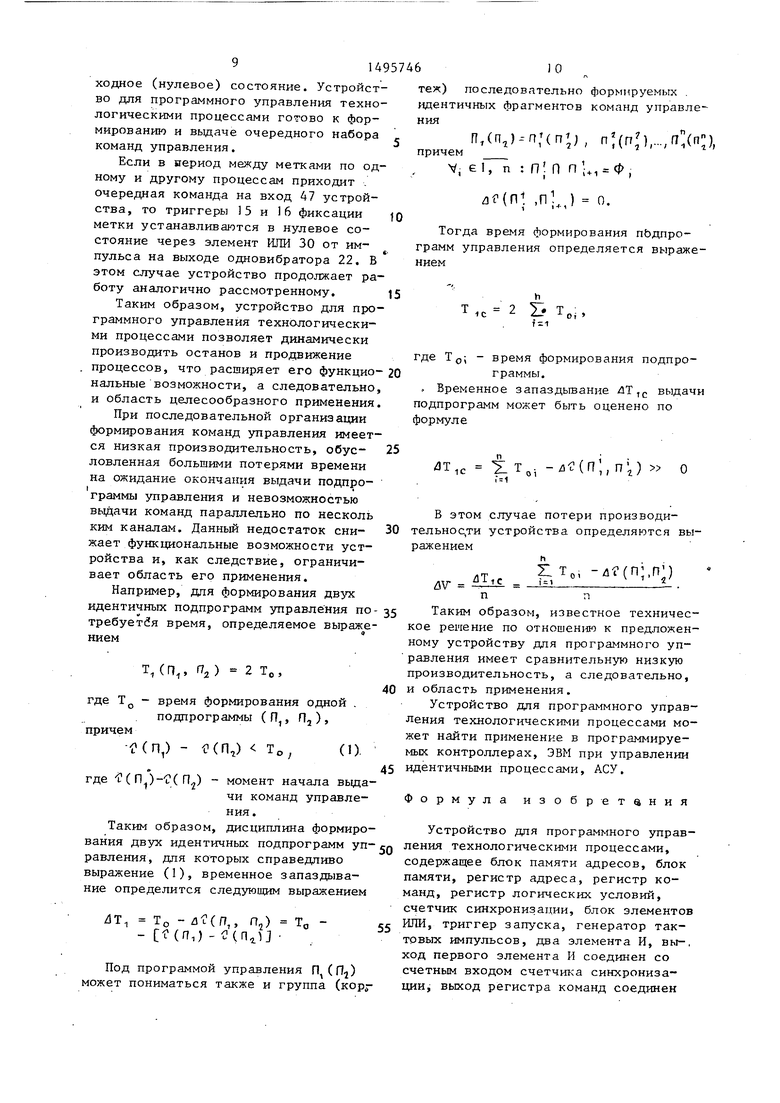

На фиг. 1 представлена функциональ- рая схема устройства для программного

управления технологическими процессами; на фиг. 2 - функциональная схема блока стековой памяти.

Устройство дпя программного управления технологическими процессами (фиг. 1) содержит блок 1 памяти адресов, блок 2 памяти, блок 3 стековой памяти, регистр 4 команд, регистр 5 логических условий, регистр 6 адреса, счетчик 7 адреса, счетчик 8 длины линейной последовательности нанокоманд, первьй счетчик 9 глубины стека, второй счетчик 10 глубины стека, счетчик 11 синхронизации, первый дешифратор 12 глубины стека, второй дешифратор 13 глубины стека, дешифратор 14 синхронизации, первый 15 и второй

16триггеры фиксации метки, триггер

17запуска, первый 18 и второй 19

ий

СО

сд |

4

05

3:j49

триггеры управления, триггер 20 установки, генератор 21 тактовых импульсов, одиовибратор 22, блок элементов ИЛИ 23, первьй 24, девятый 25, и одиннадцатый 26 элементы ИЛИ, блок 27 элементов суммы по модулю два, элемент 28 задержки, второй 29, пятый 30 и четвёртый 31 элементы ИЛИ, элемент И-НЕ 32, первый 33 и второй 34 элементы НЕ, третий 35, восьмой 36, шестой 37 и седьмой 38 элементы ИЛИ, .третий 39, второй 40, седьмой 41, восьмой 42, четвертый 43, пятый 44, шестой 45 и первый 46 элементы И.

На фиг. 1 обозначены также информационный вход 47 устройства, вход 48 логических условий устройства, установочньй вход 49 устройства, третий 50 и четвертьй 51 управляющие входы устройства, первый 52 и второй 53 управляющие входы устройства, первьй управляющий вход 54 блока стековой памяти, информационный вход 55 блока стековой памяти, тактовый вход 56 блока стековой памяти, второй управляющий вход 57 блока стековой памяти, первьй управляющий выход 38 блока стековой памяти, первый инфор- мациокньй выход 59 блока стековой памяти, второй управляющий выход 60 блока стековой памяти, второй инфор- мационньй выход 61 блока стежковой памяти, первый 62 и второй 63 управляющие выходы устройства.

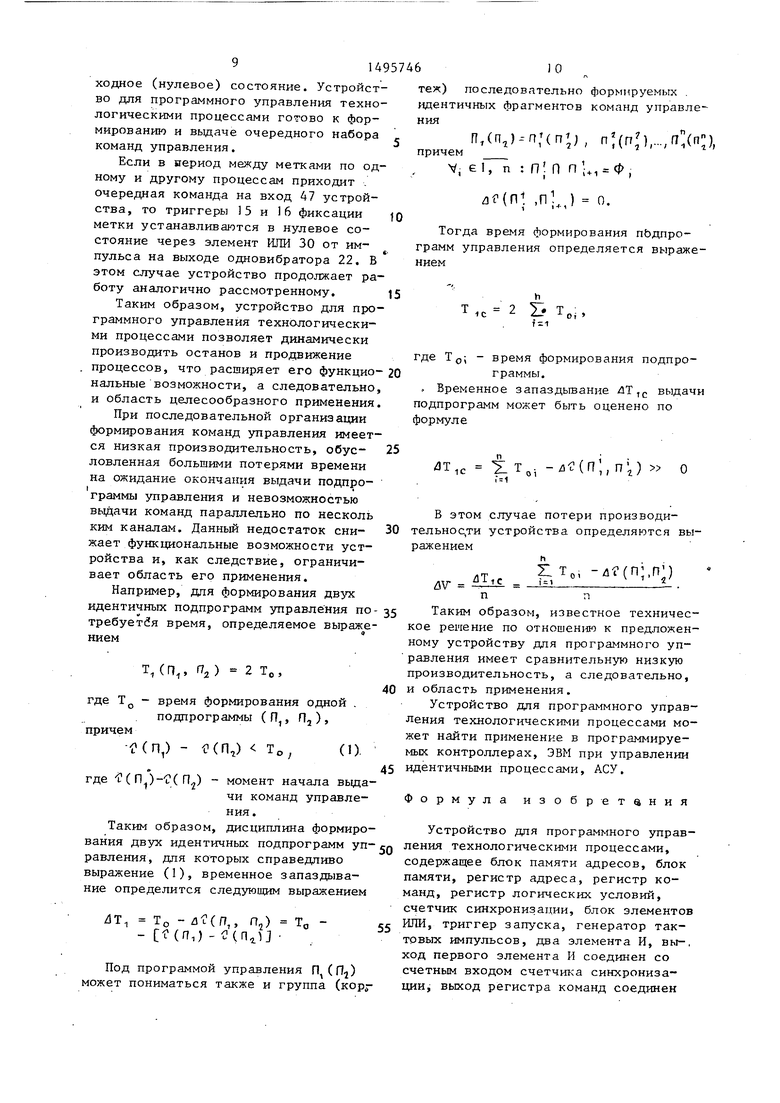

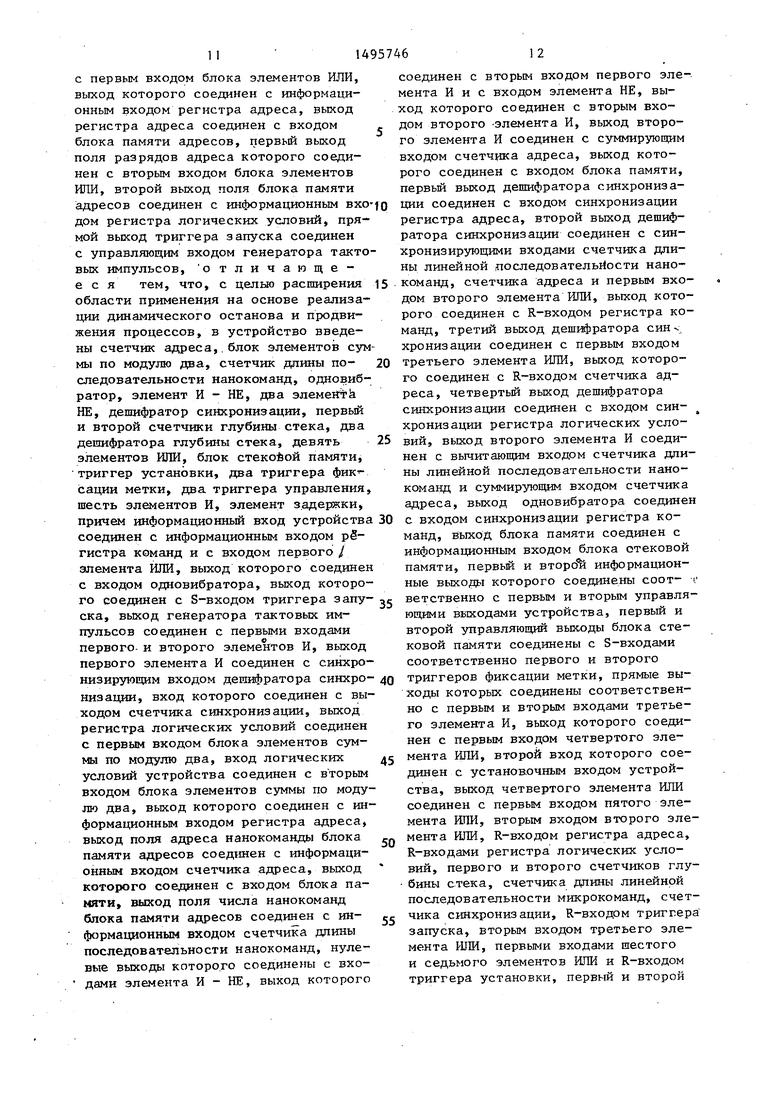

Блок 3 стековой памяти (фиг. 2) содержит блоки 64.1-64.п регистров (где п - глубина стекаХ первьй 65 и второй 66 коммутаторы. :

Работа устройства начинается путем подачи на вход 49 сигнала начальной установки.«Импульс начальной установки через элемент ИЛИ 31 поступает на R-входы регистра 5 логических условий, счетчиков 9 и 10 глубины стека, счетчика 8 длины линейной последовательности нанокоманд, регистра 6 адреса, триггера 17 запуска, счетчика 11 синхронизации и через элемент ИЛИ 30 Ha.R-входа первого 15 и вто- рого триггеров 16 фиксации метки, через элемент ИЛИ 29 на R-вход регистра 4 команд, через элементы ИЛИ 37 и 38 первого 18 и второго 19 триггеров управления, триггера 20 установки

При поступлении команды, определяю щей адрес программы формирования команд управления, на вход 47 устройства команда через элемент ШШ 24 на

выходе одновибратора 22 формирует гш- пульс. Этот импульс поступает на вход синхронизации регистра 4 команд, обеспечивая тем самым запись кода с входа 47 устройства в регистр 4 команд.«

Одновременно с записью информации в регистр 4 команд импульс на выходе одновибратора 22 устанавливает триггер 17 запуска в единичное состояние. Уровень логической единицы с выхода триггера 17 запуска разрешает формирование тактовых импульсов на выходе генератора 21 для синхронр зации работы устройств . Импульсы с выхода генератора 2 через элемент И 46 поступают на вход счетчика 11 синхронизации. Прохождение тактовых импульсов через элемент И 46 обусловлено тем, что счетчик 8 дпины линейной последовательности нанокоманд находится в нулевом состоянии и поэтому на выходе элемента НЕ 32 состояние логической единицы.

При изменении состояния счетчика II синхронизации на первом выходе дешифратора 14 синхронизации появляется сигнал логической единицы. Этот сигнал передним фронтом обеспечивает перезапись информации из регистра 4 команд через блок элементов ИЛИ 23 в регистр 6 адреса. Очередной импульс генератора 21 вызьшает, изменение состояния дешифратора 14 синхронизации. Импульс с второго выхода дешифратора 14 поступает на входы синхронизации счетчиков 7 и 8, обеспечивая тем самым запись информации из соответствующих полей блока 1 памяти адресов в эти счетчики. Кроме того, этот же импульс через элемент ИЛИ 29 устанавливает в ноль регистр 4 команд.

Занесение кода в счетчик 8 дпины линейной последовательности нанокоманд вызьшает появление уровня логического нуля на выходе элемента И - НЕ 32. Это запрещает прохождение импульсов генератора 21 через элемент И 46 на вход счетчика 11 синхронизации. В то же время на выходе элемента НЕ 33 появляется уровень логической единицы, что разрешает прохождение импульсов синхронизации с выхода генератора 21 через элемент И 40. На третьем входе элемента И 40 будет сигнал логической единицы. Это обусловлено тем, что счетчики 9 и 10 глубины стека находятся в нулевом со14957-466

Информация в регистре 6 адреса формируется из кода номера следующей последовательности с поля 11 блока 1 памяти, дополняемой (в зависимости от хода процесса управления) информацией из регистра 5 логических.условий. Переменная часть адреса образуется путем модификации на блоке 27 элементов суммы по модулю два информации регистра 5 логическими условиями, поступающими с входа 48 устройства. Далее описанньй цикл работы повторяется.

. В любой момент времени мокет быть подана команда на останов одного из двух вьщаваемых процессов. Дпя останова продвижения первого процесса на вход 50 устройства подается импульс. (фиг, 2) блока 3 стековой памяти. Эти 20 Этот импульс переводит триггер 18 упстоянии. Следовательно, на первых выходах дешифраторов 12 и 13 глубины стека будет урювень логической единицы. Так как первые вькоды дешифраторов 12 и 13 не соединены с входами элементов ИЛИ 25 н 26, то на выходе элемента И 41 будет сигнал логического нуля. Этот сигнал поступает на вход элемента НЕ 34 и разрешает прохождение тактовых импульсов через элемент И 40 с выхода генератора 21.

Импульсы синхронизации с выхода элемента И 40 поступают на суммирующий вход счетчика 7 адреса, тем самымj5 обеспечивая последовательное считывание из блока 2 памяти.

Сосчитанные из блока 2 памяти на- нокоманды поступают на вход 55

10

нанокоманды с выходов 59 и 61 блока 3 стековой памяти поступают на выходы 62 и 63 устройства (фиг. 1) на управ«- ление исполнительными элементами, блоками.

Одновременно синхроимпульсы с выхода элемента И 40 поступают на вы- читающий вход счетчика 8 длины линейной последовательности нанокоманд. При достижении счетчиком 8 нулевого состояния на выходе элемента И-НЕ 32 появляется сигнал логической единицы. Этот сигнал через элемент И 46 разрешает прохождение импульсов сихрониза-. цин с выхода генератора 21 на вход счетчика 11 синхронизации. Одновременно с этим на выходе элемента НЕ 33 появляется сигнал логиче.ского нуля, который запрещает прохождение импульсов синхронизации с выхода генератора 21 через элемент И 40.

Очередной импульс с выхода генератора 21 изменяет состояние счетчика 11 синхронизации, что, в свою очередь вызвтает возникновение импульса на третьем выходе дешифратора 14 синхро- низации. Этот импульс через элемент ИЦИ 35 устанавливает в нулевое состояние счетчик 7 адреса. При следующем импульсе синхронизации на четвертом выходе дешифратора 14 синхронизации появляется импульс, которьй обеспечивает запись информации в регистр 5 логических условий из соответствующего поля блока 1 памяти адресов.

Следующий синхроимпуль.с вызывает появление на первом выходе тора 14 импульса, обеспечивающего запись информации в регистр 6 адреса.

35

равления в единичное состояние. Сигнал логического нуля с инверсного выхода триггера 18 yпpaвheния запрещает работу дешифратора 12 глубины сте25 ка. Это вызьшает запрещение прохожде- ния нанокоманд на выход 62 устройства через блок 3 стековой памяти. Сигнал логической единицы с прямого выхода триггера 18 управления разрешает про30 хождение импульсов синхронизации через элементы И 40 и 43 на суммирующий вход счетчика 9 глубины стека, определяющего величину задержки выдачи команд управления первого процесса. В то же время уровень логической единицы с прямого выхода триггера 18 управления через элемент ИЛИ 36 устанавливает триггер 20 установки в единичное состояние. Это обеспечивает

4Q прохождение импульсов синхронизации через элемент И 45 и элемент 28 задержки на вход 56 блока 3 стековой памяти. Поступающие синхроимпульсы производят последовательное занесе-

дс ние нанокоманд в стековую память, состоящую из блока регистров 64.1-64.п, где п - глубина стека (фиг. 2).

Для перезапуска (рестарта) задержанного первого процесса с входа 52

50 устройства подается сигнал логической единицы. По этому сигналу через элемент ИЛИ 37 триггер 18 управления переходит в нулевое состояние. Уровень логической единицы с инверсного

ее выхода триггера 18 управления разрешает работу дешифратора 12 глубины стека, который по входу 54 блока 3 стековой памяти разрешает считьшание нанокоманд из соответствующего регистра

10

5

равления в единичное состояние. Сигнал логического нуля с инверсного выхода триггера 18 yпpaвheния запрещает работу дешифратора 12 глубины сте5 ка. Это вызьшает запрещение прохожде- ния нанокоманд на выход 62 устройства через блок 3 стековой памяти. Сигнал логической единицы с прямого выхода триггера 18 управления разрешает про0 хождение импульсов синхронизации через элементы И 40 и 43 на суммирующий вход счетчика 9 глубины стека, определяющего величину задержки выдачи команд управления первого процесса. В то же время уровень логической единицы с прямого выхода триггера 18 управления через элемент ИЛИ 36 устанавливает триггер 20 установки в единичное состояние. Это обеспечивает

Q прохождение импульсов синхронизации через элемент И 45 и элемент 28 задержки на вход 56 блока 3 стековой памяти. Поступающие синхроимпульсы производят последовательное занесе-

с ние нанокоманд в стековую память, состоящую из блока регистров 64.1-64.п, где п - глубина стека (фиг. 2).

Для перезапуска (рестарта) задержанного первого процесса с входа 52

0 устройства подается сигнал логической единицы. По этому сигналу через элемент ИЛИ 37 триггер 18 управления переходит в нулевое состояние. Уровень логической единицы с инверсного

е выхода триггера 18 управления разрешает работу дешифратора 12 глубины стека, который по входу 54 блока 3 стековой памяти разрешает считьшание нанокоманд из соответствующего регистра

71495746

блока регистров 64.1-64„п через коммутатор 65 на выход устройства 62. Уровень логического нуля с прямого выхода триггера 18 управления запрещает прохождение импульсов синхронизации через элемент И 43 на суммирующий вход счетчика 9 глубины стека. В результате этого команды управления первым процессом выдают с задержкой на to заданное число тактов относительно второго процесса.

Для останова продвижения второго процесса с входа 51 устройства подается сигнал логической единицы. По 15 этому сигналу триггер 19 управления переходит в единичное состояние. Уровень логического нуля с инверсного выхода триггера 19 управления запрещает работу дешифратора 13 глубины 20 стека. Это запрещает прохождение на- ноЛоманд управления вторым процессом на выход 63 устройства.

Уровень логической единицы с мого выхода триггера 19 управления 25 разрешае т прохождение импульсов синхронизации через элемент И 44 на суммирующий вход 10 глубины стека. При этом, если первый процесс не

Сигнал логической е; р1ницы с выхода элемента И поступает на вход элемента НЕ 34. Образованный на выходе элемента НЕ 34 сигнал логического нуля запрещает прохождение импульсов синхронизации через элемент И 40. В результате этого останавливается работа счетчика 7 адреса, счетчика.8 длин линейной последовательности наноко- манд, останавливается запись информа- 1ЩИ в блок регистров 64.1-64.п блока 3 стековой памяти. Одновременно с этим уровень логической единицы с выхода элемента И 41 разрешает прохождение синхроимпульсов с выходи генератора 21 через элемент И 42 на вычитающие входы первого 9 и второго 10 счетчиков глубины стека..Вычитание происходит до тех пор, пока один из счетчиков не перейдет в нулевое состояние. При этом вьщача информации на выходы 62 и 63 не прекращается.

Так как выходы дешифраторов 12 и 13 глубины стека, соответствующие со-

был задержан, то через элемент ИЛИ 36 30 стоянию счетчиков 9 и 10 глубины степроисходит установка триггера 20 снятия копии в единичное состояние. Для рестарта задержанного второго процесса с входа- 53 устройства подается

единичньй сигнал, переводящий триггер 5 нулевым состоянием, появляется уро- 19 управления в нулевое со стояние. .При этом происходит разрешение работы дешифратора 13 глубины стека и запрещается прохождение импульсов синхро- . низаций через элемент И 44 на сумми- дО рующий вход счетчика 10 глубины стека. Таким образом, команда считываются

вень логического нуля. В результате этого восстанавливается работа счетчика 7 адреса, счетчика 8 длины нейной последовательности нанокоманд восстанавливается запись информации в блок регистров 64..п блока 3 стековой памяти.

50

через соответствующий регистр блока регистров .п блока 3 стековой памяти (фиг. 2) через коммутатор 66 j на вход 63 устройства.

В том случае, если быпа произведена задержка выдачи одного из двух формируемых процессов, а затем другого, т.е. должна происходить вьщача копий обоих пpoцeccot; с заданной задержкой одного относительно другого, то устройство работает следующим образом.

С выходов дешифратора 12 глубины стека код поступает на элемент ИЛИ 25, в результате чего на первом входе элемента И 41 будет уровень логической единицы. В то же время код с выходов

55

8

дешифратора 13 глубиш 1 стека поступает на элемент ИЛИ 26, что вызывает появление уровня логической единицы на втором вх.оде элемента И 41.

Сигнал логической е; р1ницы с выхода элемента И поступает на вход элемента НЕ 34. Образованный на выходе элемента НЕ 34 сигнал логического нуля запрещает прохождение импульсов синхронизации через элемент И 40. В результате этого останавливается работа счетчика 7 адреса, счетчика.8 длин линейной последовательности наноко- манд, останавливается запись информа- 1ЩИ в блок регистров 64.1-64.п блока 3 стековой памяти. Одновременно с эти уровень логической единицы с выхода элемента И 41 разрешает прохождение синхроимпульсов с выходи генератора 2 через элемент И 42 на вычитающие вход первого 9 и второго 10 счетчиков глубины стека..Вычитание происходит до тех пор, пока один из счетчиков не перейдет в нулевое состояние. При этом вьщача информации на выходы 62 и 63 не прекращается.

Так как выходы дешифраторов 12 и 13 глубины стека, соответствующие со-

ка, не соединены с входами соответствующих элементов ИЛИ 25 и 26, то на выходе Элемента ШШ 25 (26), соответствующего счетчику глубины стека с

нулевым состоянием, появляется уро-

вень логического нуля. В результате этого восстанавливается работа счетчика 7 адреса, счетчика 8 длины нейной последовательности нанокоманд, восстанавливается запись информации в блок регистров 64..п блока 3 стековой памяти.

Таким образб)м, сохраняется задержка процессов относительно первоначального значения и между собой. В то же время счетчики глубины стека- находятся в состоянии минимально возможного заполнения.

Окончание работы устройства происходит следующим образом.

- признак окончания процесса по выходам 58 и 60 блока 3 стековой памяти в зависимости от соотношения задержки между процессами переводит поочередно триггеры 15 и 16 фиксации метки в единичное состояние. Уровень логической единицы с выкода элемента И 39 через элемент ИЛИ 31 устанавливает элементы памяти устройства в исходкое (нулевое) состояние. Устройство для программного управления технологическими процессами готово к формированию и выдаче очередного набора команд управления.

Если в период между метками по одному и другому процессам приходит . очередная команда на вход 47 устройства, то триггеры 15 и 16 фиксации метки устанавливаются в нулевое состояние через элемент ИЛИ 30 от импульса на выходе одновибратора 22. В этом случае устройство продолжает работу аналогично рассмотренному.

Таким образом, устройство для программного управления технологическими процессами позволяет динамически производить останов и продвижение процессов, что расширяет его функциональные возможности, а следовательно, и область целесообразного применения.

При последовательной организации формирования команд управления имеется низкая производительность, обус- ловленная большими потерями времени на ожидание окончания выдачи подпрограммы управления и невозможностью выдачи команд параллельно по несколь КИМ каналам. Данный недостаток сни- жает функциональные возможности устройства и, как следствие, ограничивает область его применения.

Например, для формирования двух идентичных подпрограмм управления по- требуется время, определяемое выражением

Т, ( П, ) 2 TO ,

где Тр - время формирования одной .

подпрограммы ( П,, П), причем

-(П,) - 1(П,) TO, (1),

где i ( ПЛ-СС П) - момент начала выдачи команд управления.

Таким образом, дисциплина формирования двух идентичных подпрограмм УП-

равления, для которых справедливо выражение (1), временное запаздывание определится следующим выражением

ЛТ, TO - Л(П,, П,) TO -

- t cnj (п

Под программой управления П, (П) может пониматься также и группа (кор;теж) последовательно формируемых . идентичных фрагментов команд управле- ния

г/г,

причем

пДп,)--п;(г7р, п;(п,),.,г7,(п),

V, el, п : П П пи, ф, л (П ,П,.,) 0.

Тогда время формирования пЬдпро- грамм управления определяется выражением

1C

2 I. Т,,,

1-1

где TO; - время формирования подпрограммы.

. Временное запаздьгоание ЛТ, выдачи подпрограмм может быть оценено по формуле

ЛТ,е |-Т„. -Я(П;,П-,)

В этом случае потери производи- тельнос,ти устройства определяются выражением

25 30

35

40

5

Q

5

UY

т,с (п;.п;)

пп

Таким образом, известное техническое реиение по отношению к предложенному устройству для программного управления имеет сравнительную низкую производительность, а следовательно, и область применения.

Устройство для программного управления технологическими процессами может найти применение в програм {ируе- мых контроллерах, ЭВМ при управлении идентичными процессами, АСУ.

Формула изобретения

Устройство дпя программного управления технологическими процессами, содержащее блок памяти адресов, блок памяти, регистр адреса, регистр команд, регистр логических условий, счетчик синхронизации, блок злементов ИЛИ, триггер запуска, генератор тактовых импульсов, два элемента И, вы-, ход первого элемента И соединен со счетным входом счетчика синхронизации, выход регистра команд соединен

с первым входом блока элементов ИЛИ, выход которого соединен с информационным входом регистра адреса, выход регистра адреса соединен с входом блока памяти адресов, первый выход поля разрядов адреса которого соединен с вторым входом блока элементов ИЛИ, второй выход поля блока памяти адресов соединен с информационным вхо дом регистра логических условий, прямой выход триггера запуска соединен с управляющим входом генератора тактовых импульсов, отличающееся тем, что, с целью расширения области применения на основе реализации динамического останова и продвижения процессов, в устройство введены счетчик адреса,.блок элементов суммы по модулю два, счетчик длины по- следовательности нанокоманд, одновиб- ратор, элемент И - НЕ, два элeмeйtk НЕ, дешифратор синхронизации, первый и второй счетчики глубины стека, два дешифратора глубины стека, девять

элементов ИЛИ, блок стекойой памяти, триггер установки, два триггера фик - сации метки, два триггера управления, шесть элементов И, элемент задержки, причем информационньй вход устройства соединен с информационным входом регистра команд и с входом первого / элемента ИЛИ, выход которого соединен с входом одновибратора, выход которого соединен с S-входом триггера запу- ска, выход генератора тактовых импульсов соединен с первыми входами первого- и второго элементов И, выход первого элемента И соединен с синхронизирующим входом дешифратора синхро- низащш, вход которого соединен с выходом счетчика синхронизации, выход регистра логических условий соединён с первым входом блока элементов суммы по модулю два, вход логических условий устройства соединен с вторым входом блока элементов суммы по модулю два, выход которого соединен с информационным входом регистра адреса, выход поля адреса нанокоманды блока памяти адресов соедтшен с информационным входом счетчика адреса, выход которого соединен с входом блока памяти выход поля числа нанокоманд блока памяти адресов соединен с ин- формационным входом счетчика длины последовательности нанокоманд, нулевые выходы которого соединены с входами элемента И - НЕ, выход которого

соединен с вторым входом первого элемента И и с входом элемента НЕ, выход которого соединен с вторым входом второго -элемента И, выход второго элемента И соединен с суммирующем входом счетчика адреса, выход которого соединен с входом блока памяти, первьй выход депшфратора синхронизации соединен с входом синхронизации регистра адреса, второй выход дешифратора синхронизации соединен с синхронизирующими входами счетчика длины линейной доследовательйости нанокоманд, счетчика адреса и первым входом второго элемента ИЛИ, выход которого соединен с R-входом регистра команд, третий выход дешифратора син хронизации соединен с первым входом третьего элемента ИЛИ, выход которого соединен с R-входом счетчика адреса, четвертьй выход дешифратора синхронизации соединен с входом синхронизации регистра логических условий, выход второго элемента И соединен с вычитающим входом счетчика длины линейной последовательности нанокоманд и суммирующим входом счетчика адреса, выход одновибратора соединен с входом синхронизации регистра команд, выход блока памяти соединен с информационным входом блока стековой памяти, первьй и второчи информационные выходы которого соединены соот- ветственно с первым и вторым управляющими выходами устройства, первый и второй управляющий выходы блока стековой памяти соединены с S-входами соответственно первого и второго триггеров фиксации метки, прямые выходы которых соединены соответственно с первым и вторым входами третьего элемента И, выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с установочным входом устройства, выход четвертого элемента ИЛИ соединен с первым входом пятого элемента ИЛИ, вторым входом второго элемента ИЛИ, R-входом регистра адреса, R-входами регистра логических условий, первого и второго счетчиков глубины стека, счетчика длины линейной последовательности микрокоманд, счетчика синхронизации, R-входом триггера запуска, вторым входом третьего элемента ИЛИ, первыми входами шестого и седьмого элементов ИЛИ и R-входом триггера установки, первый и второй

управляющие входы устройства соединены с вторыми входами соответственно шестого и седьмого элементов ИЛИ, выходы которых соединены с R-входами соответственно первого и второго триггеров управления, третий и чет- вертьй управляющие входы устройства соединены с S-входами соответственно первого и второго триггеров управления, выход одновибратора соединен с вторым входом пятого элемента РШИ, выход которого соединен с R-входами первого и второго триггеров фиксации метки, прямой выход первого триггера управления соединен с первым входом восьмого элемента ИЛИ и первым входом четвертого элемента И, выход которого соединен с суммирующим входом первого счетчика гл убины стека, выход второго элемента И соединен с вторым выходом четвертого элемента И, первым входом пятого элемента И и первым входом шестого элемента И, выход пятого элемента И соединен с суммирующим входом второго счетчика глубины стека, прямой выход второго триггера управления соединен с вторым В5СОДОМ пятого элемента И и вторым входом восьмого элемента ИЛИ, выход которого соединен с S-входом триггера снятия копии, прямой выход

которого соединен с вторым входом ше-- стого элемента И, выходы первого и второго счетчиков глубины стека соединены со входами соответственно первого и второго дешифраторов глубины стека, управляющие входы которых соединены с инверсными выходами соответственно первого и второго триггеров

управления, выход шестого элемента И - через элемент задержки соединен с тактовым входом блока стековой памяти, выход первого дешифратора глубины СТек соединен с входом девятого элемента ИЛИ и первым управляющим входом блока стековой памяти, выход второго дешифратора глубины стека соединен с входом десятого элемента ИЛИ и вторым управляющим входом блока стековой

памяти, выходы первого и второго дешифраторов гл гбины стека соединены соответственно с первым(И вторым выходами седьмого. элементш И, выход которого соединен с первым входом восьмого элемента И и входом второго элемента НЕ, выход генератора тактовых импульсов соединен с вторым входом восьмого элемента И, выход которого соединен с вычитающими входами перво

го и второго счетчиков глубины стека, выход элемента НЕ соединен с третьим входом второго элемента И.

фие.2

Авторы

Даты

1989-07-23—Публикация

1987-08-03—Подача