74

/25

/т7

(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования и декодирования телевизионного сигнала | 1988 |

|

SU1649674A1 |

| Кодер сигнала изображения | 1990 |

|

SU1730724A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Кодер сигнала изображения | 1989 |

|

SU1644389A1 |

| Дифференциальный импульсный кодер телевизионного сигнала | 1987 |

|

SU1481900A2 |

| Кодер телевизионного сигнала | 1988 |

|

SU1569990A1 |

| Устройство для кодирования и декодирования цифрового телевизионного сигнала | 1988 |

|

SU1566485A1 |

| Кодер видеосигнала | 1987 |

|

SU1506554A1 |

| Устройство для эффективного кодирования изображений | 1988 |

|

SU1559412A1 |

| Кодер сигнала изображения | 1988 |

|

SU1518922A1 |

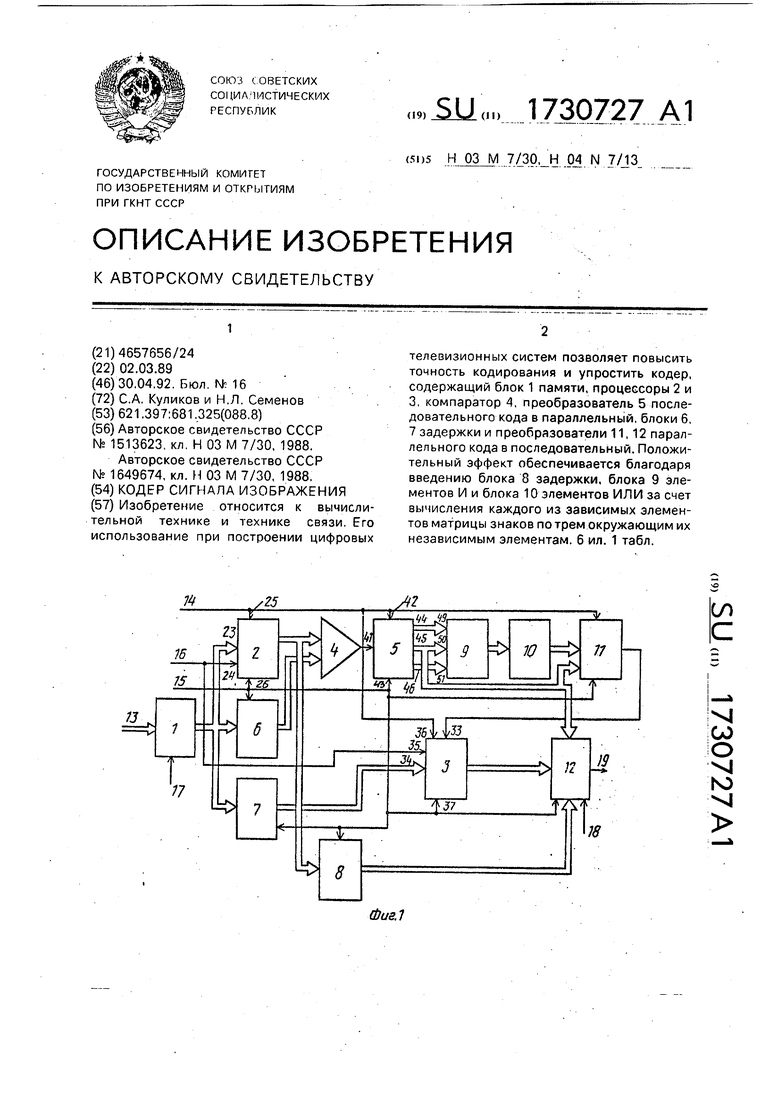

Изобретение относится к вычислительной технике и технике связи. Его использование при построении цифровых телевизионных систем позволяет повысить точность кодирования и упростить кодер, содержащий блок 1 памяти, процессоры 2 и 3, компаратор 4, преобразователь 5 последовательного кода в параллельный, блоки 6, 7 задержки и преобразователи 11,12 параллельного кода в последовательный. Положительный эффект обеспечивается благодаря введению блока 8 задержки, блока 9 элементов И и блока 10 элементов ИЛИ за счет вычисления каждого из зависимых элементов матрицы знаков по трем окружающим их независимым элементам. 6 ил. 1 табл.

XI

CJ О

XI

ю

х|

Изобретение относится к вычислительной технике и технике связи и может быть использовано при построении цифровых телевизионных (ТВ) систем.

Цель изобретения - повышение точности кодирования и упрощение кодера.

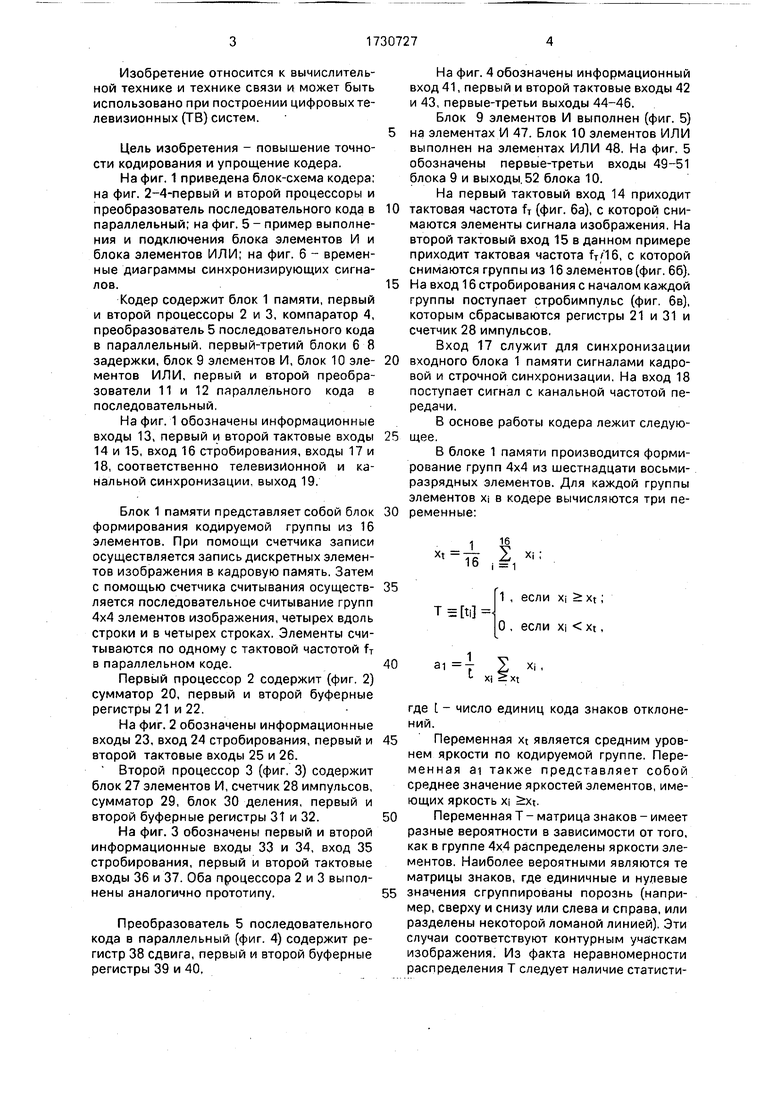

На фиг. 1 приведена блок-схема кодера; на фиг. 2-4-первый и второй процессоры и преобразователь последовательного кода в параллельный; на фиг. 5 - пример выполнения и подключения блока элементов И и блока элементов ИЛИ; на фиг. 6 - временные диаграммы синхронизирующих сигналов.

Кодер содержит блок 1 памяти, первый и второй процессоры 2 и 3, компаратор 4, преобразователь 5 последовательного кода в параллельный, первый-третий блоки б 8 задержки, блок 9 элементов И, блок 10 элементов ИЛИ, первый и второй преобразователи 11 и 12 параллельного кода в последовательный.

На фиг. 1 обозначены информационные входы 13, первый и второй тактовые входы 14 и 15, вход 16 стробирования,входы 17 и 18, соответственно телевизионной и канальной синхронизации, выход 19.

Блок 1 памяти представляет собой блок формирования кодируемой группы из 16 элементов. При помощи счетчика записи осуществляется запись дискретных элементов изображения в кадровую память. Затем с помощью счетчика считывания осуществляется последовательное считывание групп 4x4 элементов изображения, четырех вдоль строки и в четырех строках. Элементы считываются по одному с тактовой частотой fT в параллельном коде.

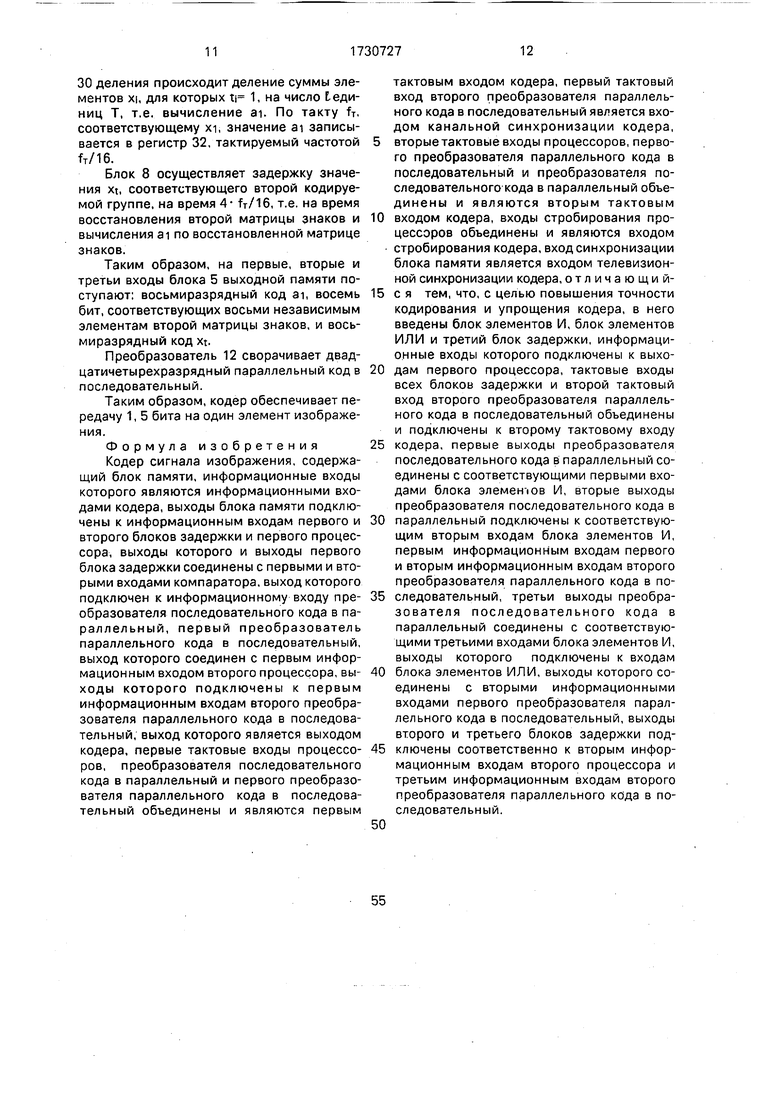

Первый процессор 2 содержит (фиг. 2) сумматор 20, первый и второй буферные регистры 21 и 22.

На фиг. 2 обозначены информационные входы 23, вход 24 стробирования, первый и второй тактовые входы 25 и 26.

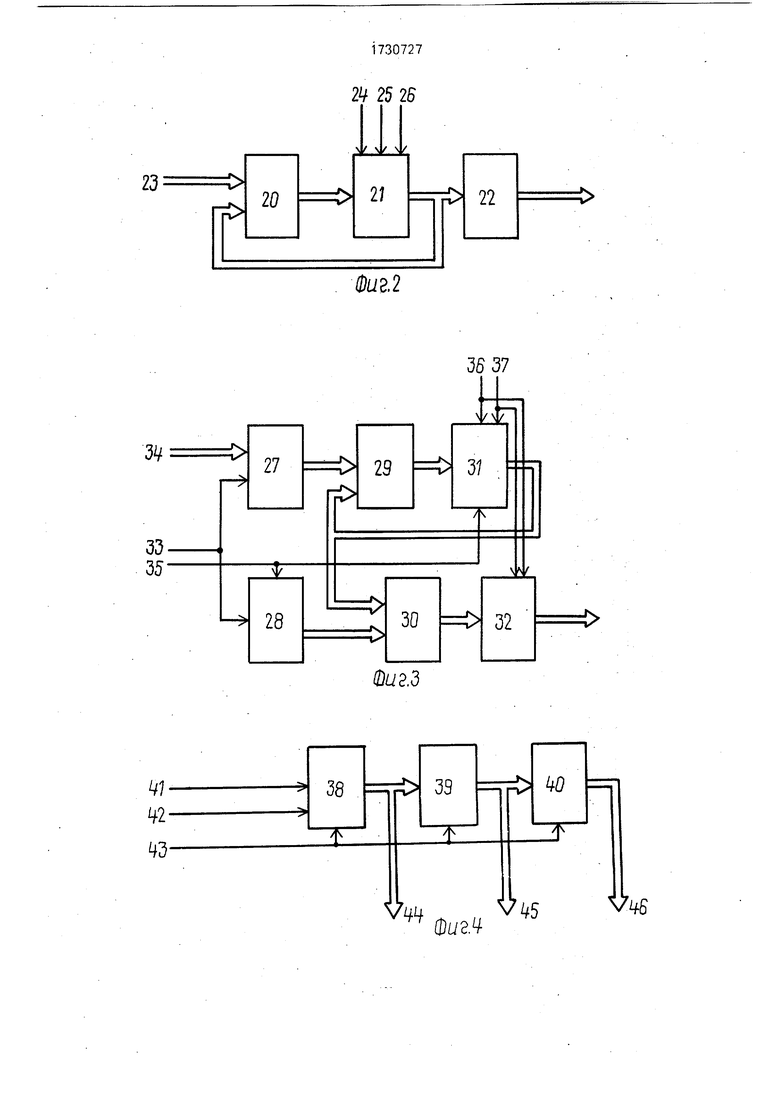

Второй процессор 3 (фиг. 3) содержит блок 27 элементов И, счетчик 28 импульсов, сумматор 29, блок 30 деления, первый и второй буферные регистры 31 и 32.

На фиг. 3 обозначены первый и второй информационные входы 33 и 34, вход 35 стробирования, первый и второй тактовые входы 36 и 37. Оба процессора 2 и 3 выполнены аналогично прототипу.

Преобразователь 5 последовательного кода в параллельный (фиг. 4) содержит регистр 38 сдвига, первый и второй буферные регистры 39 и 40,

На фиг. 4 обозначены информационный вход 41, первый и второй тактовые входы 42 и 43, первые-третьи выходы 44-46.

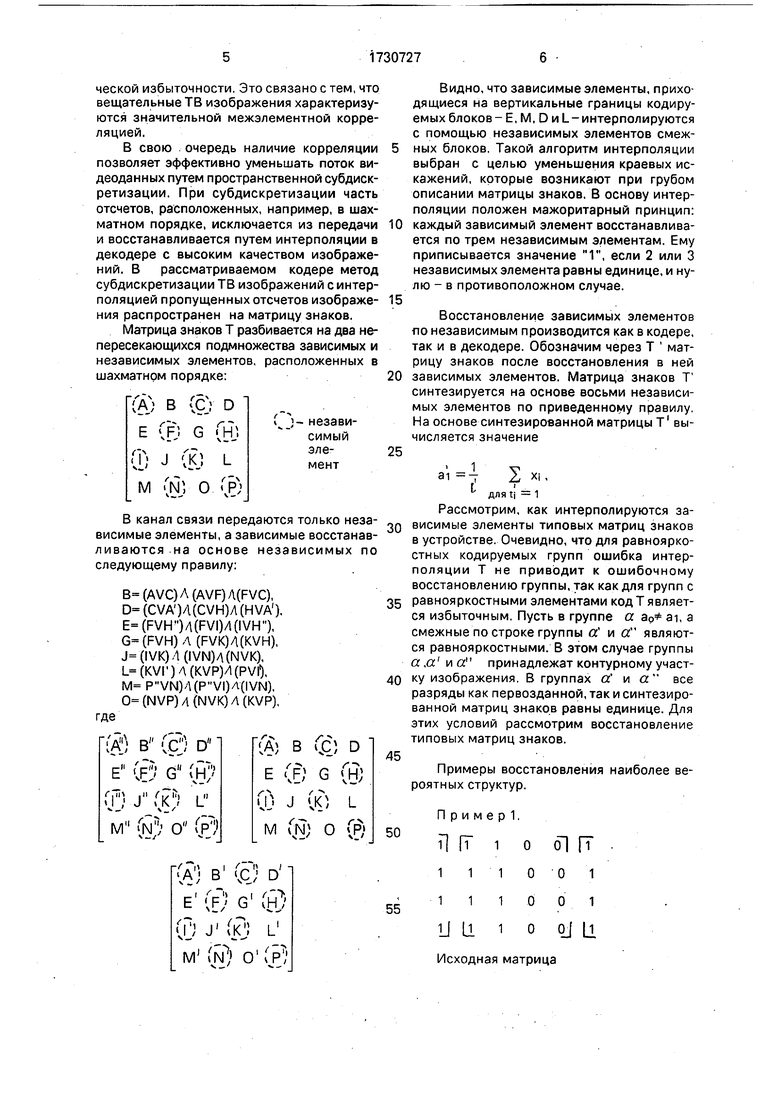

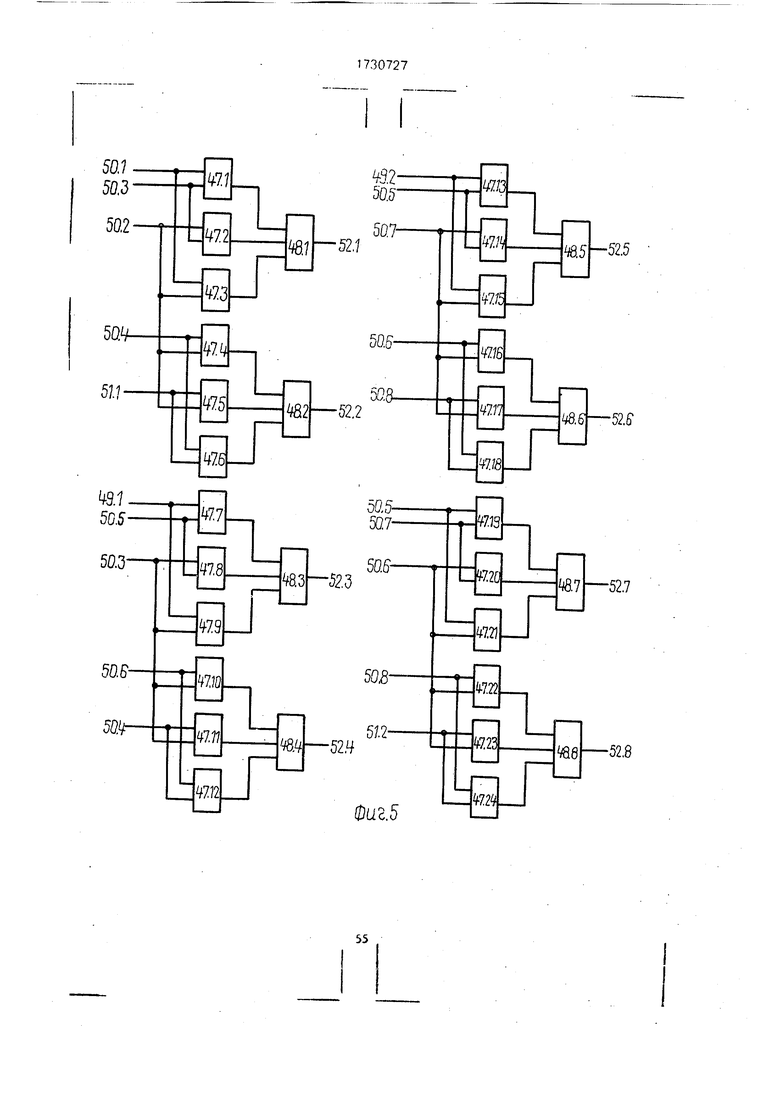

Блок 9 элементов И выполнен (фиг. 5)

на элементах 1/1 47. Блок 10 элементов ИЛИ

выполнен на элементах ИЛИ 48. На фиг. 5

обозначены первые-третьи входы 49-51

блока 9 и выходы. 52 блока 10.

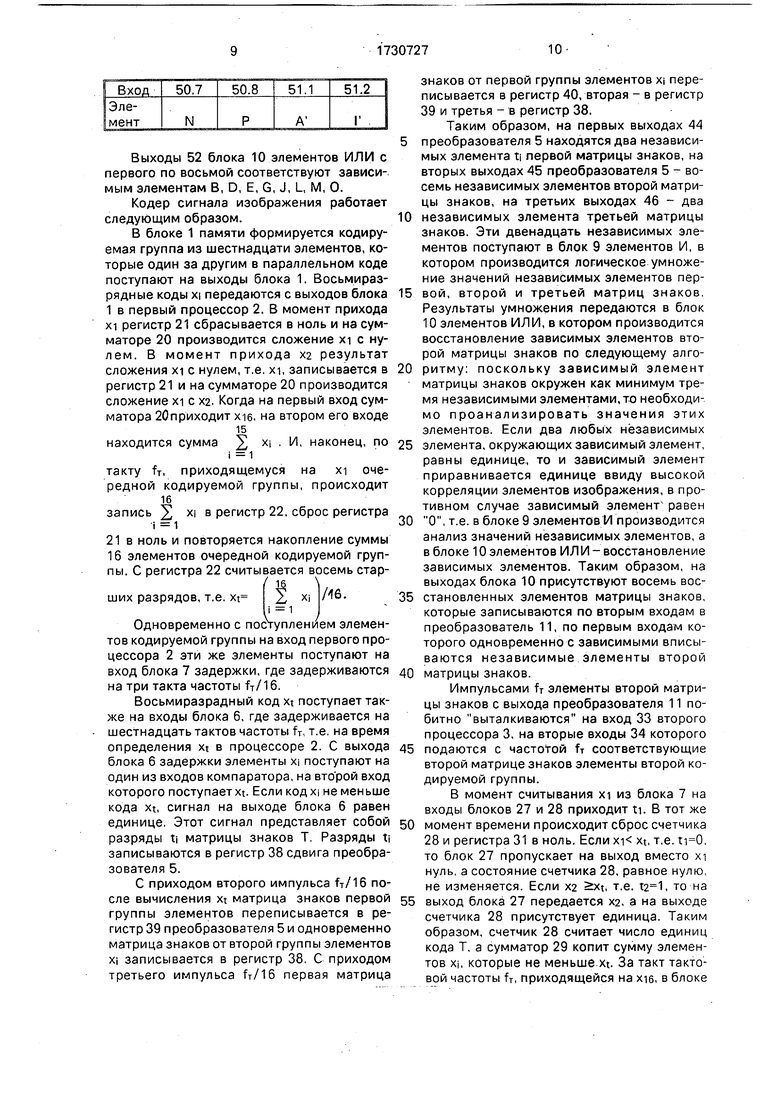

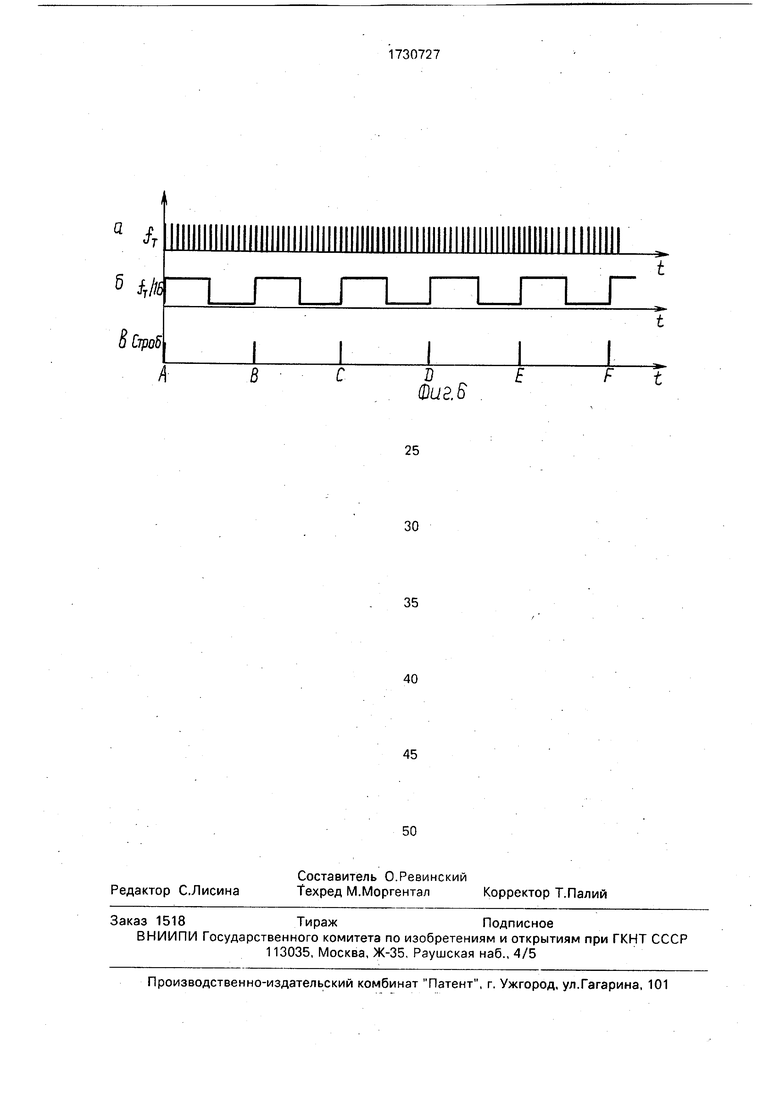

На первый тактовый вход 14 приходит тактовая частота ft (фиг. 6а), с которой снимаются элементы сигнала изображения. На второй тактовый вход 15 в данном примере приходит тактовая частота fT/16, с которой снимаются группы из 16 элементов (фиг. 66). На вход 16 стробирования с началом каждой группы поступает стробимпульс (фиг. 6в), которым сбрасываются регистры 21 и 31 и счетчик 28 импульсов.

Вход 17 служит для синхронизации входного блока 1 памяти сигналами кадровой и строчной синхронизации. На вход 18 поступает сигнал с канальной частотой передачи.

В основе работы кодера лежит следую- щее.

В блоке 1 памяти производится формирование групп 4x4 из шестнадцати восьмиразрядных элементов. Для каждой группы элементов х, в кодере вычисляются три пе- ременные;

,2т Xi:

35

, если xi xt О , если xi xt

40

31 I

Xi ,

Xi Sxt

где I - число единиц кода знаков отклонений.

Переменная xt является средним уровнем яркости по кодируемой группе. Переменная ai также представляет собой среднее значение яркостей элементов, имеющих ЯРКОСТЬ Xi Xt.

Переменная Т - матрица знаков - имеет разные вероятности в зависимости от того, как в группе 4x4 распределены яркости элементов. Наиболее вероятными являются те матрицы знаков, где единичные и нулевые

значения сгруппированы порознь (например, сверху и снизу или слева и справа, или разделены некоторой ломаной линией). Эти случаи соответствуют контурным участкам изображения. Из факта неравномерности распределения Т следует наличие статистической избыточности. Это связано с тем, что вещательные ТВ изображения характеризуются значительной межэлементной корреляцией.

В свою очередь наличие корреляции позволяет эффективно уменьшать поток видеоданных путем пространственной субдискретизации. При субдискретизации часть отсчетов, расположенных, например, в шахматном порядке, исключается из передачи и восстанавливается путем интерполяции в декодере с высоким качеством изображений. В рассматриваемом кодере метод субдискретизации ТВ изображений с интерполяцией пропущенных отсчетов изображения распространен на матрицу знаков.

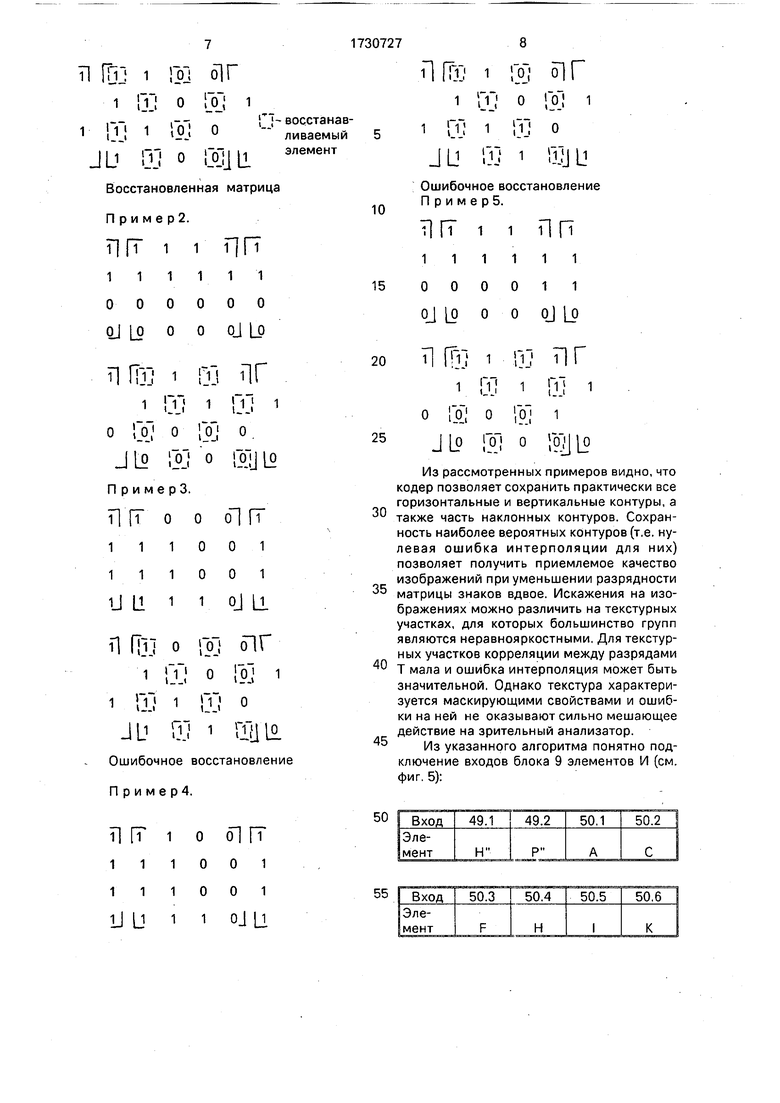

Матрица знаков Т разбивается на два непересекающихся подмножества зависимых и независимых элементов, расположенных в шахматном порядке:

В канал связи передаются только независимые элементы, а зависимые восстанав- ливаются на основе независимых по следующему правилу:

B(AVC)A(AVF)A(FVC), D (CVA )A(CVH)A (HVA ). E(FVH)A(FVIM(IVH), G(FVH)A(FVK)A(KVH), J(IVK)4(IVN)A(NVK), L(KVI )A(KVP)/1(PVr), M )/()A(IVN), 0(NVP)4(NVK)A(KVP),

D

L Cp7 )

/v

f,A) В (ЧС) D

E (F; G (н)

CD J (к) L

M (N) о (P)

rf T

IA J в1 cj D E ® G © ® j () L M (N) o (p5

0

5

0

Видно, что зависимые элементы, приходящиеся на вертикальные границы кодируемых блоков - E, M, D и L - интерполируются с помощью независимых элементов смежных блоков. Такой алгоритм интерполяции выбран с целью уменьшения краевых искажений, которые возникают при грубом описании матрицы знаков. В основу интерполяции положен мажоритарный принцип: каждый зависимый элемент восстанавливается по трем независимым элементам. Ему приписывается значение 1, если 2 или 3 независимых элемента равны единице, и нулю - в противоположном случае.

Восстановление зависимых элементов по независимым производится как в кодере, так и в декодере. Обозначим через Т матрицу знаков после восстановления в ней зависимых элементов. Матрица знаков Т синтезируется на основе восьми независимых элементов по приведенному правилу. На основе синтезированной матрицы Т1 вычисляется значение

1 1 V

31 - 2/ Xi , гi

для ti 1

Рассмотрим, как интерполируются зависимые элементы типовых матриц знаков в устройстве. Очевидно, что для равноярко- стных кодируемых групп ошибка интерполяции Т не приводит к ошибочному восстановлению группы, так как для групп с равнояркостными элементами код Т является избыточным, Пусть в группе а а0 ai, a смежные построке группы а и а являются равнояркостными. В этом случае группы а ,а и а принадлежат контурному участку изображения. В группах а и а все разряды как первозданной, так и синтезированной матриц знаков равны единице. Для этих условий рассмотрим восстановление типовых матриц знаков.

Примеры восстановления наиболее вероятных структур.

Пример.

Т 1 0 Т

111001

111001

ij LL 1 о oj LL

Исходная матрица

71 iTij 1 о о|Г

1 Т| о oj 1

.-(--, восстанав1 ij 1 iOj ° ливаемый

элемент

JL S ° GDJH

Восстановленная матрица П ри м е р2.

лги

пг

ГГ

(j

о о

ffi о I5U15

рЗ.

о о

оПГТ

0 0 1 О 0 1

1 oJ Li

Л Г о ipjо Г

1 |T« о|pj 1

1 и 1 ио

JU Э 1пЩо.

Ошибочное восстановлени П р и м е р 4.

Л Т 1 0 61 Т 111001 111001

ij U 1 1 oj ц.

Л 1 Го; о Г

1 1

о

i:°j

1 ,..,

L1 ffl 1 SJU

i л 1 пп о

Ошибочное восстановление П р и м е р 5.

7| 7 1 1 Л П 111111 00001 1 OJ О 0 0 Oj 0

fins

1 -1 I ijj

лг

ijj

о

L°J

И1 1JJ

1

25

jLo S о iojjio

Из рассмотренных примеров видно, что кодер позволяет сохранить практически все горизонтальные и вертикальные контуры, а также часть наклонных контуров. Сохранность наиболее вероятных контуров (т.е. нулевая ошибка интерполяции для них) позволяет получить приемлемое качество изображений при уменьшении разрядности матрицы знаков вдвое. Искажения на изображениях можно различить на текстурных участках, для которых большинство групп являются неравнояркостными. Для текстурных участков корреляции между разрядами Т мала и ошибка интерполяция может быть значительной. Однако текстура характеризуется маскирующими свойствами и ошибки на ней не оказывают сильно мешающее действие на зрительный анализатор.

Из указанного алгоритма понятно подключение входов блока 9 элементов И (см. фиг. 5):

Выходы 52 блока 10 элементов ИЛИ с первого по восьмой соответствуют зависимым элементам В, D, E, G, J, L, М, О.

Кодер сигнала изображения работает следующим образом.

В блоке 1 памяти формируется кодируемая группа из шестнадцати элементов, которые один за другим в параллельном коде поступают на выходы блока 1. Восьмиразрядные коды xi передаются с выходов блока 1 в первый процессор 2. В момент прихода xi регистр 21 сбрасывается в ноль и на сумматоре 20 производится сложение xi с нулем. В момент прихода Х2 результат сложения xi с нулем, т.е. xi, записывается в регистр 21 и на сумматоре 20 производится сложение xi с Х2. Когда на первый вход сумматора 20приходит xi6, на втором его входе

15

находится сумма 2 х И, наконец, по

i 1

такту fr, приходящемуся на xi очередной кодируемой группы, происходит

16 запись 2 х| в регистр 22, сброс регистра

i 1

21 в ноль и повторяется накопление суммы 16 элементов очередной кодируемой группы. С регистра 22 считывается восемь стар( « ,.А ших разрядов, т.е. xt 2, х

11 1 J

Одновременно с поступлением элементов кодируемой группы на вход первого процессора 2 эти же элементы поступают на вход блока 7 задержки, где задерживаются на три такта частоты fV/16.

Восьмиразрадный код xt поступает также на входы блока 6, где задерживается на шестнадцать тактов частоты fT т.е. на время определения xt в процессоре 2. С выхода блока 6 задержки элементы xi поступают на один из входов компаратора, на второй вход которого поступаетхь Если код xi не меньше кода xt, сигнал на выходе блока 6 равен единице. Этот сигнал представляет собой разряды tj матрицы знаков Т. Разряды ti записываются в регистр 38 сдвига преобразователя 5.

С приходом второго импульса fT/16 после вычисления xt матрица знаков первой группы элементов переписывается в регистр 39 преобразователя 5 и одновременно матрица знаков от второй группы элементов х| записывается в регистр 38. С приходом третьего импульса fT/16 первая матрица

знаков от первой группы элементов xi переписывается в регистр 40, вторая - в регистр 39 и третья - в регистр 38.

Таким образом, на первых выходах 44

преобразователя 5 находятся два независимых элемента ti первой матрицы знаков, на вторых выходах 45 преобразователя 5 - восемь независимых элементов второй матрицы знаков, на третьих выходах 46 - два

0 независимых элемента третьей матрицы знаков. Эти двенадцать независимых элементов поступают в блок 9 элементов И, в котором производится логическое умножение значений независимых элементов пер5 вой, второй и третьей матриц знаков. Результаты умножения передаются в блок 10 элементов ИЛИ, в котором производится восстановление зависимых элементов второй матрицы знаков по следующему алго0 ритму: поскольку зависимый элемент матрицы знаков окружен как минимум тремя независимыми элементами, то необходи- мо проанализировать значения этих элементов. Если два любых независимых

5 элемента, окружающих зависимый элемент, равны единице, то и зависимый элемент приравнивается единице ввиду высокой корреляции элементов изображения, в противном случае зависимый элемент4 равен

0 О, т.е. в блоке 9 элементов И производится анализ значений независимых элементов, а в блоке 10 элементов ИЛИ- восстановление зависимых элементов. Таким образом, на выходах блока 10 присутствуют восемь вос5 становленных элементов матрицы знаков, которые записываются по вторым входам в преобразователь 11, по первым входам которого одновременно с зависимыми вписываются независимые элементы второй

0 матрицы знаков.

Импульсами fT элементы второй матрицы знаков с выхода преобразователя 11 по- битно выталкиваются на вход 33 второго процессора 3, на вторые входы 34 которого

5 подаются с частотой fT соответствующие второй матрице знаков элементы второй кодируемой группы.

В момент считывания xi из блока 7 на входы блоков 27 и 28 приходит ti. В тот же

0 момент времени происходит сброс счетчика 28 и регистра 31 в ноль. Если xi xt, т.е. , то блок 27 пропускает на выход вместо xi нуль, а состояние счетчика 28, равное нулю, не изменяется. Если Х2 xt, т.е. , то на

5 выход блока 27 передается ха, а на выходе счетчика 28 присутствует единица. Таким образом, счетчик 28 считает число единиц кода Т, а сумматор 29 копит сумму элементов XL которые не меньше xt. За такт тактовой частоты fT, приходящейся на xie, в блоке

30 деления происходит деление суммы элементов xi, для которых ti 1, на число Iединиц Т, т.е. вычисление ai. По такту fT, соответствующему xi, значение ai записывается в регистр 32, тактируемый частотой

Тт/16.

Блок 8 осуществляет задержку значения xt, соответствующего второй кодируемой группе, на время 4- fT/16, т.е. на время восстановления второй матрицы знаков и вычисления ai по восстановленной матрице знаков.

Таким образом, на первые, вторые и третьи входы блока 5 выходной памяти поступают: восьмиразрядный код ai, восемь бит, соответствующих восьми независимым элементам второй матрицы знаков, и восьмиразрядный код xt.

Преобразователь 12 сворачивает двадцатичетырехразрядный параллельный код в последовательный.

Таким образом, кодер обеспечивает передачу 1, 5 бита на один элемент изображения.

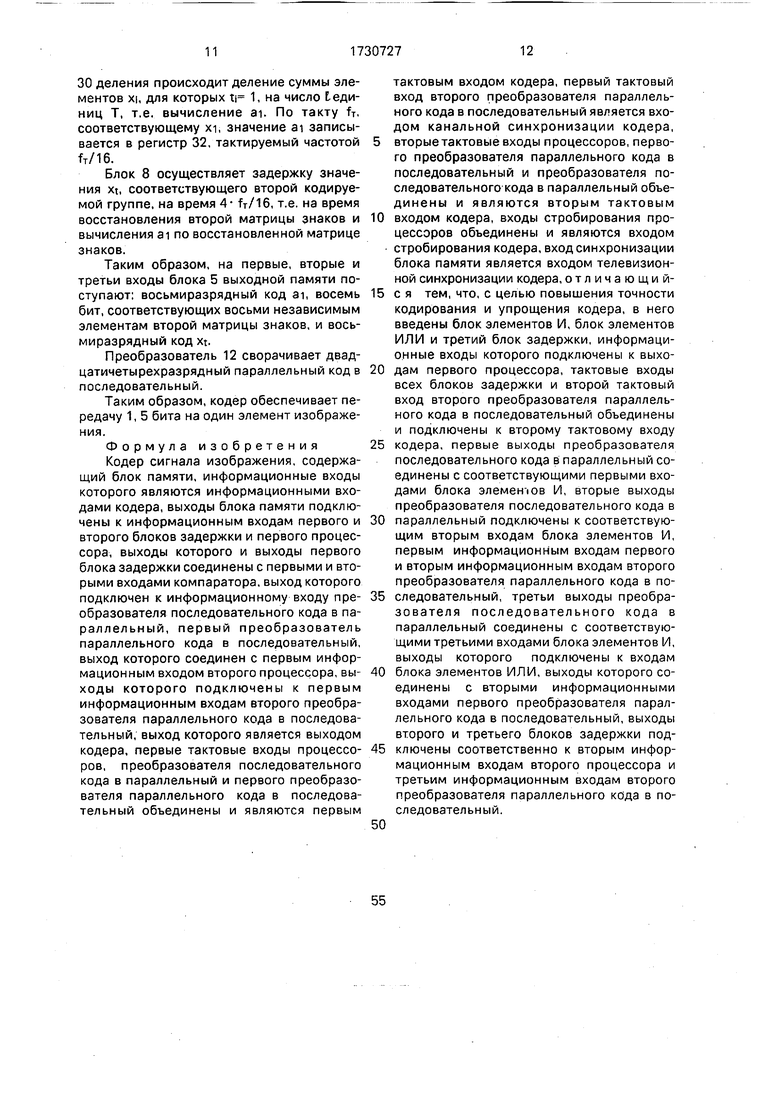

Формула изобретения

Кодер сигнала изображения, содержащий блок памяти, информационные входы которого являются информационными входами кодера, выходы блока памяти подключены к информационным входам первого и второго блоков задержки и первого процессора, выходы которого и выходы первого блока задержки соединены с первыми и вторыми входами компаратора, выход которого подключен к информационному входу преобразователя последовательного кода в параллельный, первый преобразователь параллельного кода в последовательный, выход которого соединен с первым информационным входом второго процессора, выходы которого подключены к первым информационным входам второго преобразователя параллельного кода в последовательный, выход которого является выходом кодера, первые тактовые входы процессоров, преобразователя последовательного кода в параллельный и первого преобразователя параллельного кода в последовательный объединены и являются первым

тактовым входом кодера, первый тактовый вход второго преобразователя параллельного кода в последовательный является входом канальной синхронизации кодера,

вторые тактовые входы процессоров, первого преобразователя параллельного кода в последовательный и преобразователя последовательного кода в параллельный объединены и являются вторым тактовым

входом кодера, входы стробирования процессоров объединены и являются входом стробирования кодера, вход синхронизации блока памяти является входом телевизионной синхронизации кодера, отличающийс я тем, что, с целью повышения точности кодирования и упрощения кодера, в него введены блок элементов И, блок элементов ИЛИ и третий блок задержки, информационные входы которого подключены к выходам первого процессора, тактовые входы всех блоков задержки и второй тактовый вход второго преобразователя параллельного кода в последовательный объединены и подключены к второму тактовому входу

кодера, первые выходы преобразователя последовательного кода в параллельный соединены с соответствующими первыми входами блока элементов И, вторые выходы преобразователя последовательного кода в

параллельный подключены к соответствующим вторым входам блока элементов И, первым информационным входам первого и вторым информационным входам второго преобразователя параллельного кода в последовательный, третьи выходы преобразователя последовательного кода в параллельный соединены с соответствующими третьими входами блока элементов И, выходы которого подключены к входам

блока элементов ИЛИ, выходы которого соединены с вторыми информационными входами первого преобразователя параллельного кода в последовательный, выходы второго и третьего блоков задержки подключены соответственно к вторым информационным входам второго процессора и третьим информационным входам второго преобразователя параллельного кода в последовательный.

23

С

гтс

14 25 26

f

л

1

22

te.2

3537

fe.3

Vuu щ

v

W

IW.2

№ -52.1

№

ш--

Ш-52.2

ад

.8

W-523

№

ш

Ш-5Ы

-52.5

-52.61

I-52.7

а

4

6 4А

А

В

Б

Фиг.8

F

| Авторское свидетельство СССР №1513623 кл Н 03 М 7/30, 1988 | |||

| Устройство для кодирования и декодирования телевизионного сигнала | 1988 |

|

SU1649674A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-30—Публикация

1989-03-02—Подача