Изобретение относится к импульсной технике и может быть использовано в системах автоматического управления.

Цель изобретения - повышение точности деления периодов следования импульсных сигналов при изменении интервалов между входными импульсами.

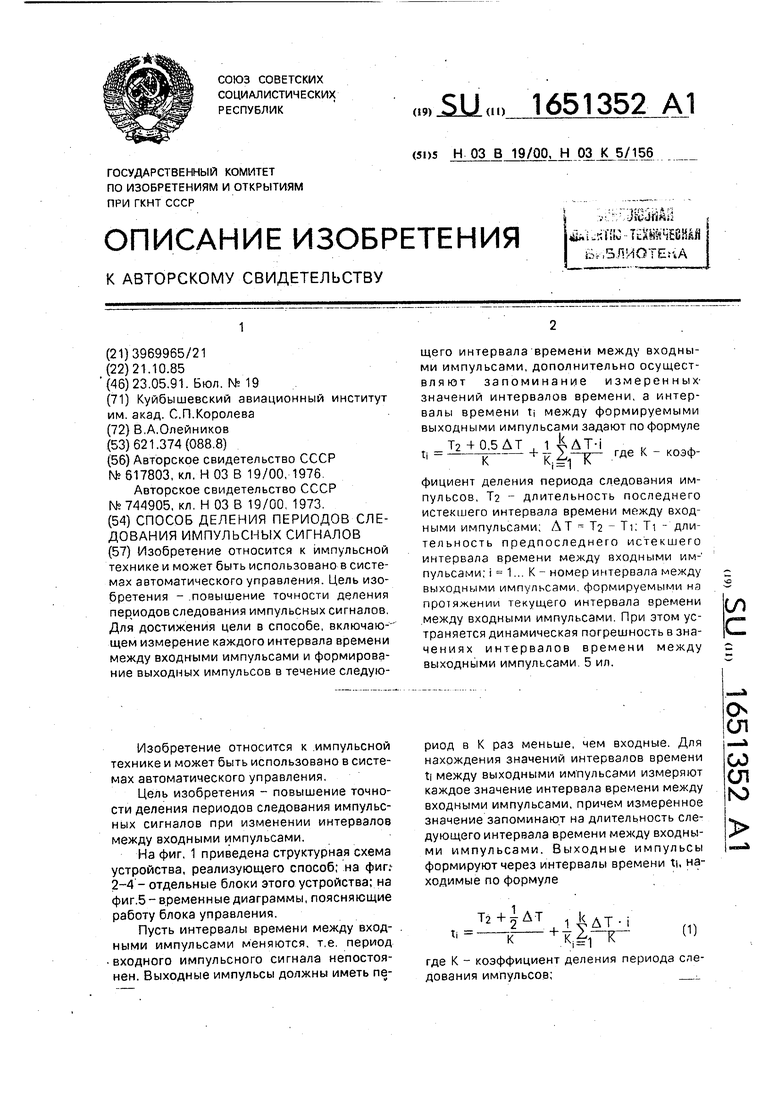

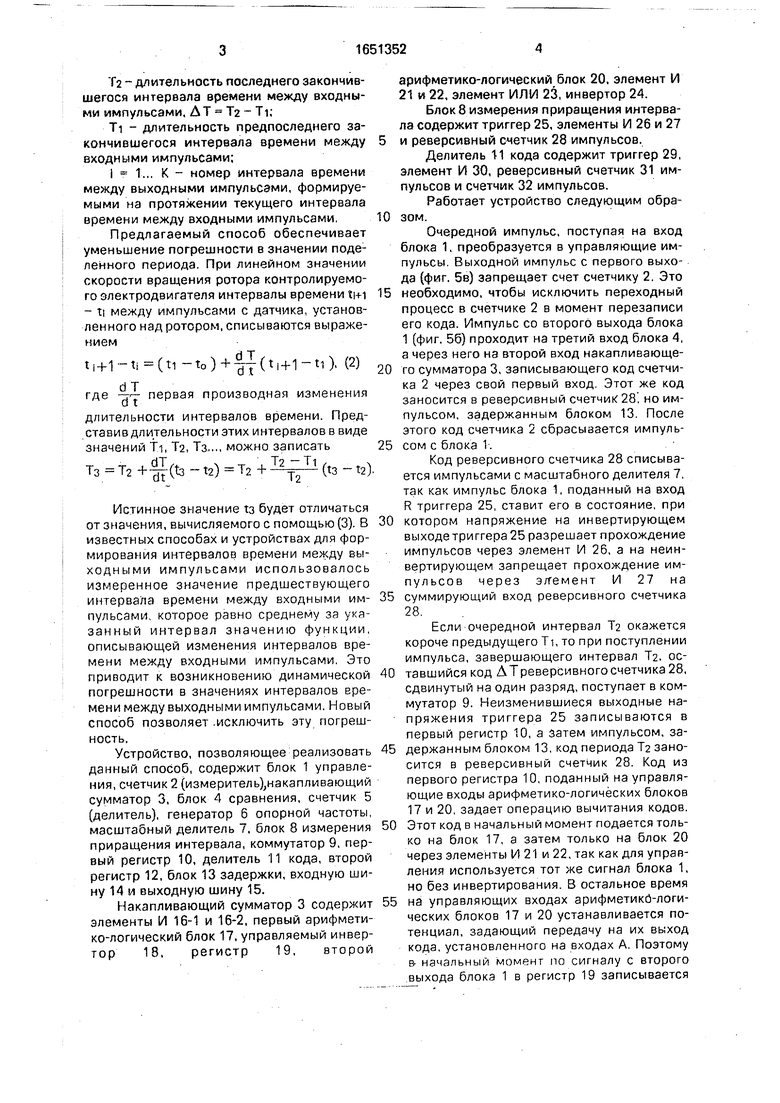

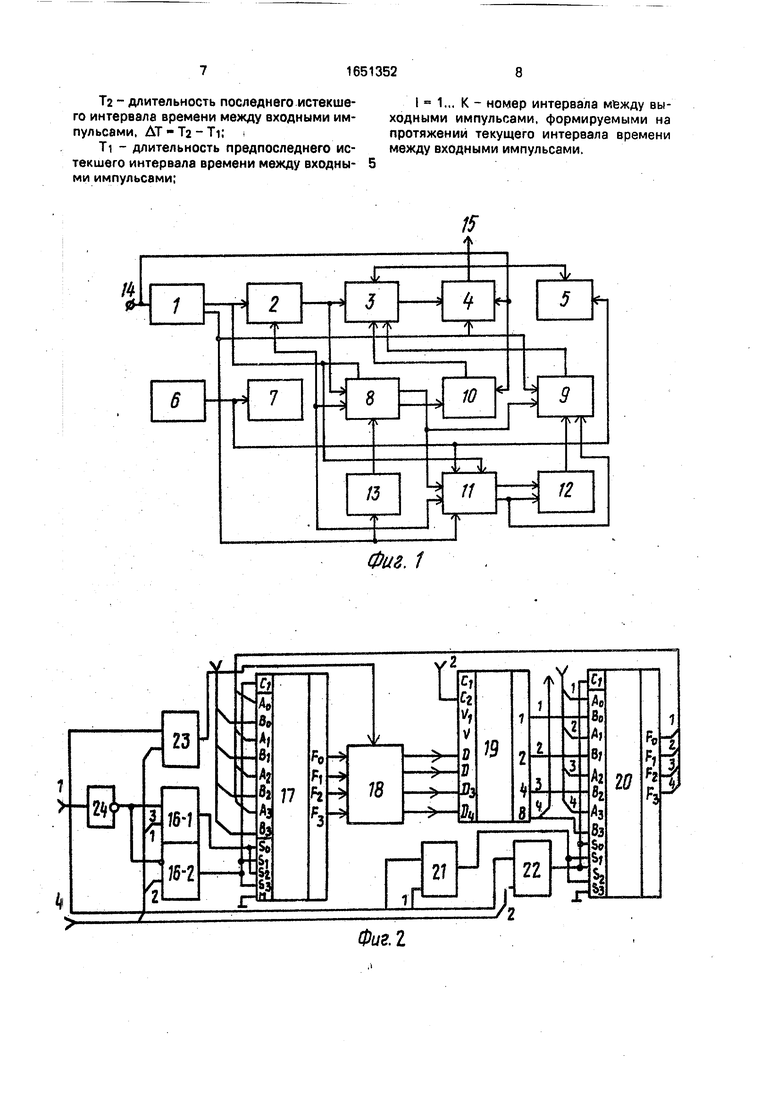

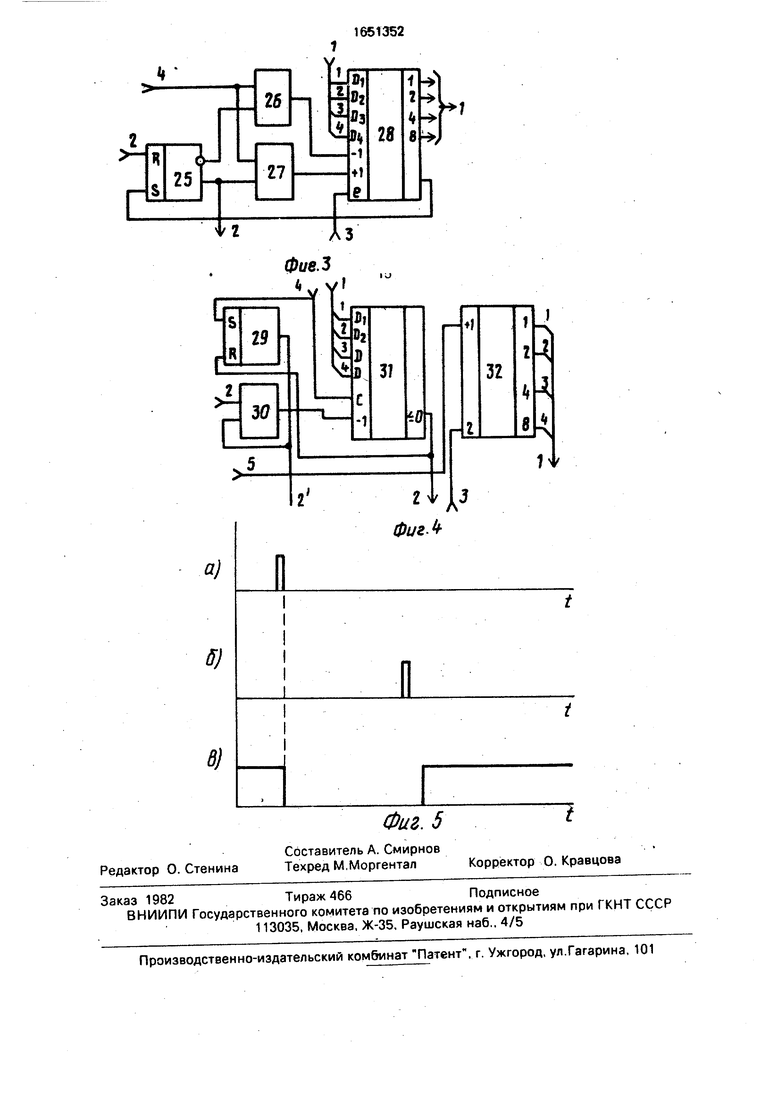

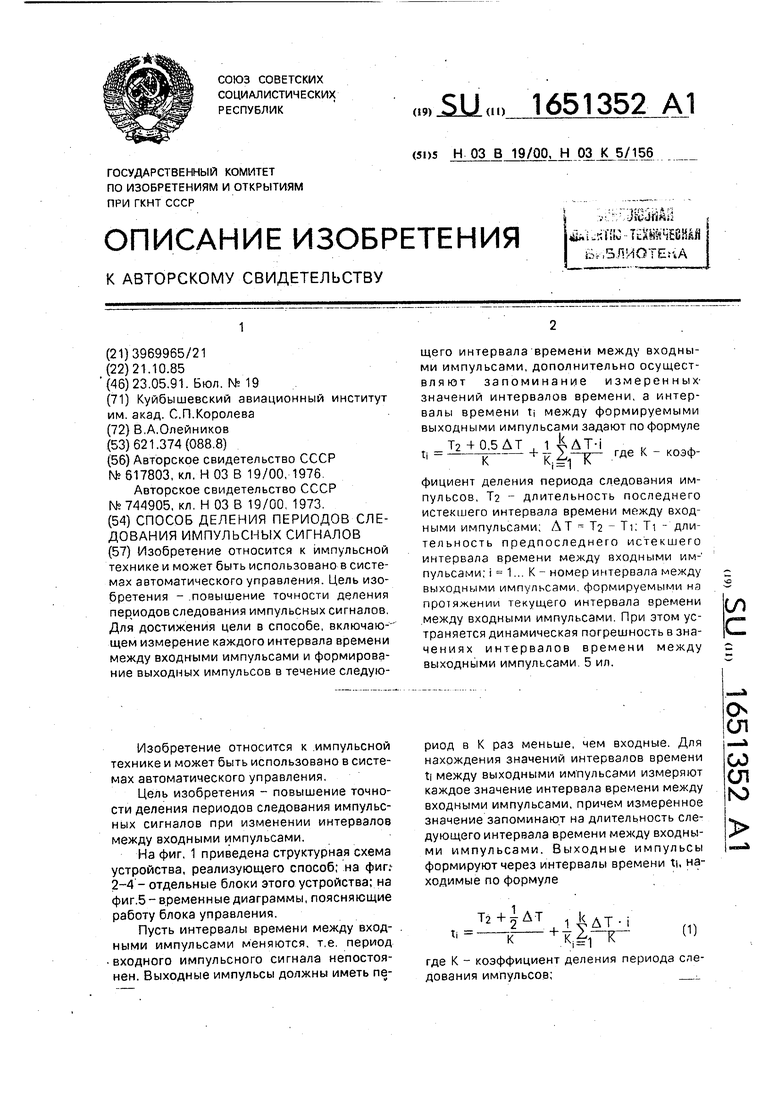

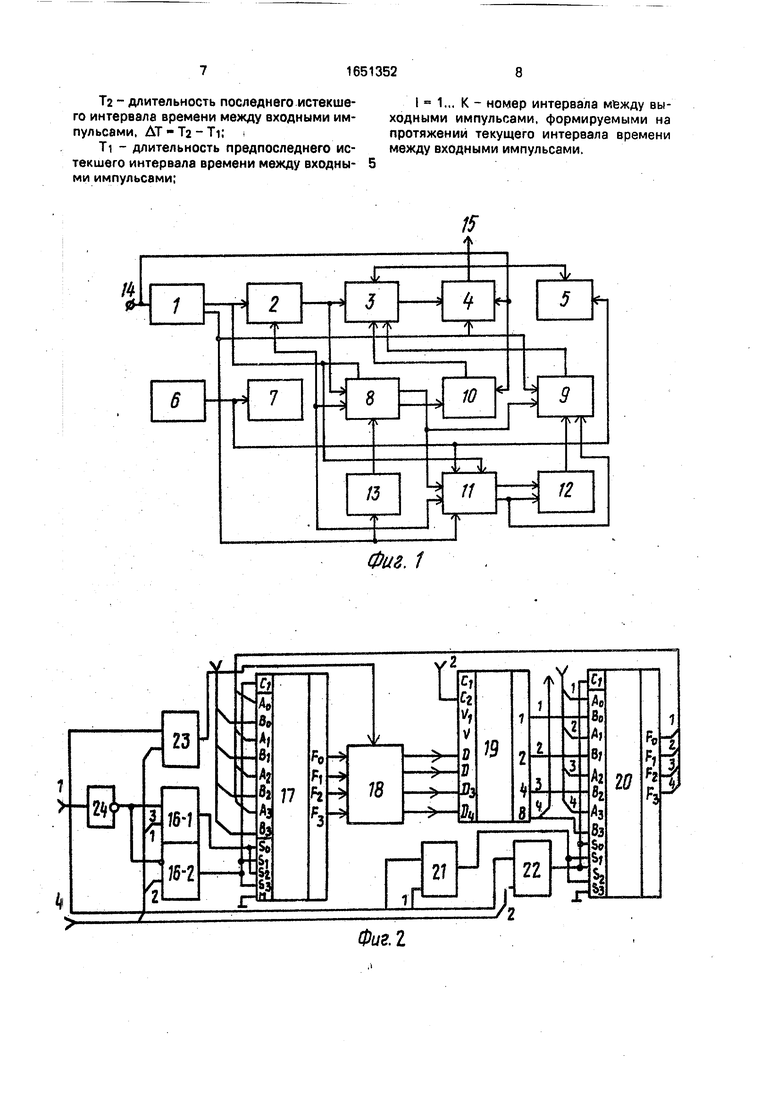

На фиг. 1 приведена структурная схема устройства, реализующего способ; на фиг; 2-4 - отдельные блоки этого устройства; на фиг.5 - временные диаграммы, поясняющие работу блока управления.

Пусть интервалы времени между входными импульсами меняются, т.е. период входного импульсного сигнала непостоянен. Выходные импульсы должны иметь период в К раз меньше, чем входные. Для нахождения значений интервалов времени ti между выходными импульсами измеряют каждое значение интервала времени между входными импульсами, причем измеренное значение запоминают на длительность следующего интервала времени между входными импульсами. Выходные импульсы формируют через интервалы времени ti, находимые по формуле

О |СЛ

СО СЛ

го

т2+|дт

tl к +к,1

lvAT

1Г

(1)

где К - коэффициент деления периода следования импульсов;

fa - длительность последнего закончившегося интервала времени между входными импульсами, AT Т2 - Ti;

TI - длительность предпоследнего закончившегося интервала времени между входными импульсами;

I 1... К - номер интервала времени между выходными импульсами, формируемыми на протяжении текущего интервала времени между входными импульсами,

Предлагаемый способ обеспечивает уменьшение погрешности в значении поделенного периода. При линейном значении скорости вращения ротора контролируемого электродвигателя интервалы времени ti+i - ti между импульсами с датчика, установленного над ротором, списываются выражением

ll(tl+l-ti), (2)

ti + 1-tl (tl -to) +

dT

где

dt

первая производная изменения

длительности интервалов времени. Представив длительности этих интервалов в виде значений ti, Та, Тз..., можно записать25

Т3 Т2 +(t3 - t2) Т2 + (t3 - t2).

Истинное значение тз будет отличаться от значения, вычисляемого с помощью (3). В известных способах и устройствах для формирования интервалов времени между выходными импульсами использовалось измеренное значение предшествующего интервала времени между входными им- пульсами, которое равно среднему за указанный интервал значению функции, описывающей изменения интервалов времени между входными импульсами. Это приводит к возникновению динамической погрешности в значениях интервалов времени между выходными импульсами. Новый способ позволяет исключить эту погрешность.

Устройство, позволяющее реализовать данный способ, содержит блок 1 управления, счетчик 2 (измеритель);накапливающий сумматор 3, блок 4 сравнения, счетчик 5 (делитель), генератор 6 опорной частоты, масштабный делитель 7, блок 8 измерения приращения интервала, коммутатор 9, первый регистр 10, делитель 11 кода, второй регистр 12, блок 13 задержки, входную шину 14 и выходную шину 15.

Накапливающий сумматор 3 содержит элементы И 16-1 и 16-2, первый арифметико-логический блок 17, управляемый инвертор 18, регистр 19, второй

0

5

0

5

0 5 0

5 0

5

арифметико-логический блок 20, элемент И 21 и 22, элемент ИЛИ 23, инвертор 24.

Блок 8 измерения приращения интервала содержит триггер 25, элементы И 26 и 27 и реверсивный счетчик 28 импульсов.

Делитель 11 кода содержит триггер 29, элемент И 30, реверсивный счетчик 31 импульсов и счетчик 32 импульсов.

Работает устройство следующим образом.

Очередной импульс, поступая на вход блока 1, преобразуется в управляющие импульсы. Выходной импульс с первого выхода (фиг. 5в) запрещает счет счетчику 2, Это необходимо, чтобы исключить переходный процесс в счетчике 2 в момент перезаписи его кода. Импульс со второго выхода блока 1 (фиг, 56) проходит на третий вход блока 4, а через него на второй вход накапливающего сумматора 3, записывающего код счетчика 2 через свой первый вход. Этот же код заносится в реверсивный счетчик 28. но импульсом, задержанным блоком 13. После этого код счетчика 2 сбрасывается импульсом с блока 1.

Код реверсивного счетчика 28 списывается импульсами с масштабного делителя 7, так как импульс блока 1, поданный на вход R триггера 25, ставит его в состояние, при котором напряжение на инвертирующем выходе триггера 25 разрешает прохождение импульсов через элемент И 26, а на неинвертирующем запрещает прохождение импульсов через элемент И 27 на суммирующий вход реверсивного счетчика 28

Если очередной интервал Т2 окажется короче предыдущего Ti, то при поступлении импульса, завершающего интервал Т2, оставшийся код ДТреверсивногосчетчика28, сдвинутый на один разряд, поступает в коммутатор 9. Неизменившиеся выходные напряжения триггера 25 записываются в первый регистр 10, а затем импульсом, задержанным блоком 13, код периода Т2 заносится в реверсивный счетчик 28. Код из первого регистра 10, поданный на управляющие входы арифметико-логических блоков 17 и 20, задает операцию вычитания кодов. Этот код в начальный момент подается только на блок 17, а затем только на блок 20 через элементы И 21 и 22. так как для управления используется тот же сигнал блока 1, но без инвертирования. В остальное время на управляющих входах арифметико-логических блоков 17 и 20 устанавливается потенциал, задающий передачу на их выход кода, установленного на входах А. Поэтому в- начальный момент по сигналу с второго выхода блока 1 в регистр 19 записывается

код счетчика измерителя 2 минус выходной код коммутатора, прошедший без изменения на вход арифметико-логического блока 17 через арифметико-логический блок 20.

Поскольку выход счетчика-измерителя 2 подключен на вход В арифметико-логического блока 17, а он может выполнять только операцию А-В, выходной сигнал блока 17 необходимо инвертировать с помощью управляемого инвертора 18 по сигналу с элемента ИЛИ 23.

Полученный код Т2 с регистра 19 поступает на блок 4, где он сравнивается с кодом счетчика 5, заполняемого импульсами генератора 6. В момент совпадения кодов на выходе блока 4 появляется импульс, который обнуляет счетчик 5 и заносит новый код в регистр 19. Этот код будет равен предшествующему коду минус код с коммутатора, потому что за время заполнения счетчика 5 изменились управляющие сигналы, а арифметико-логический блок 17 передает код поступающий на входы А без изменения, так как изменился выходной сигнал блока 1, поданный через элемент ИЛИ 23 на управляемый инвертор 18, а арифметико-логический блок 20 выдает код, равный разности кода регистра 19 и коммутатора 9.

Управляющий сигнал коммутатора 9 к этому времени изменится, так как в делителе 11 закончится процесс деления, и на выходе реверсивного счетчика 31 появится импульс, по которому во второй регистр 12 заносится код счетчика 32 и меняется состояние триггера 29. Тот же код поступает на выход коммутатора 9. Это произойдет в результате изменения потенциала триггера 29, определяющего подключение групп вхо - дов к выходу коммутатора 9. В начальный же момент после прихода входного импульса опорной частоты импульсов с второго выхода блока 1 в реверсивный счетчик 31 заносится код AT реверсивного счетчика 28, ставится в состояние 1 триггер 29, который выходным потенциалом определяет передачу через коммутатор 9 кода реверсивного счетчика 28, сдвинутого на разряд влево с помощью начальной коммуДТтации и поэтому равного -л- .

Кроме этого, тем же выходным импульсом блока 1 обнуляется счетчик 32. Деление кода происходит следующим образом. Триггер 29 выходным потенциалом разрешает прохождение через элемент И 30 импульсов с генератора 6, в то же время заполняется счетчик 32 импульсами с масштабного делителя 7, Как только код Д Т реверсивного счетчика 31 будет списан, на его выходе

появится импульс, по которому будет переписан во второй регистр 12 код счетчика 32,

AT Так как время списывания кода равно

то код счетчика 32 будет равен AT V К К

Этот код и поступает на входы коммутатора 9.

Если интервал между импульсами неизменен Ti Тз, то корректирующие коды

AT AT

AT и -пг- отсутствуют.

В случае, если Т2 Ti, реверсивный

счегчик 28 успеет списать занесенный в него код, на его выходе появится импульс, опрокидывающий триггер 25, который- в свою очередь управляет элементами 26, 27 и 28. Реверсивный счетчик 28 переключается из режима вычитания в режим суммиро вания импульсов. В момент прихода импульса из блока 1 код из реверсивного счетчика 28. как и в первом случае, переносится в коммутатор 9, но поскольку в момент

прихода импульса состояние триггера было переписано в первый регистр 10, то в накапливающий сумматор 3 поступает команда об увеличении кода, которая реализуется элементами И 16-1. 16-2, 21 и 22. Выходной код

арифметико-логического блока 17 передается без инвертирования. Остальные блоки работают без изменений

Таким образом корректируют опорный код, находящийся в регистре 19 накапливающего сумматора 3. формирование выходных импульсов происходит в момент сравнения кода счетчика 5 с опорным кодом. Это обеспечивает устранение погрешности в выходных интервалах времени.

Формула изобретен и я

Способ деления периодов следования импульсных сигналов, в соответствии с которым измеряют каждый интервал времени между входными импульсами, а в течение

следующего интервала времени между входными импульсами формируют выходные импульсы, отличающийся тем, что, с целью повышения точности деления при изменении интервала между входными

импульсами, каждое измеренное значение интервала времени между входными импульсами запоминают на длительность следующего интервала времени, а интервалы времени ti между выходными импульсами

формируют в соответствии с выражением

То +0,5 ДТ , 1 АДТ-i

К

II yil

+w

где К - коэффициент деления периода следования импульсов;

Tz длительность последнего истекшего интервала времени между входными импульсами, ДТ-12-Ti; ,

TI - длительность предпоследнего истекшего интервала времени между входны- ми импульсами;

I 1... К - номер интервала между выходными импульсами, формируемыми на протяжении текущего интервала времени между входными импульсами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коммутатор тока катушки зажигания | 1991 |

|

SU1832157A1 |

| Устройство для управления непосредственным преобразователем частоты | 1985 |

|

SU1265944A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Многоканальное устройство для обработки информации датчиков с частотным выходом | 1984 |

|

SU1196892A1 |

| Сумматор-вычитатель частотно-импульсных сигналов | 1991 |

|

SU1807483A1 |

| Устройство для контроля настройки музыкальных инструментов | 1984 |

|

SU1176375A1 |

| Быстродействующий селективный измеритель амплитуды ВЧ-сигнала | 1990 |

|

SU1780029A1 |

| Устройство для разделения импульсного потока на периодические последовательности импульсов | 1988 |

|

SU1608791A1 |

| Преобразователь двоичного кода во временной интервал | 1987 |

|

SU1444952A1 |

| Адаптивный аналого-цифровой преобразователь | 1982 |

|

SU1095387A1 |

Изобретение относится к импульсной технике и может быть использовано в системах автоматического управления. Цель изобретения - повышение точности деления периодов следования импульсных сигналов. Для достижения цели в способе, включающем измерение каждого интервала времени между входными импульсами и формирование выходных импульсов в течение следующего интервала времени между входными импульсами, дополнительно осуществляют запоминание измеренных- значений интервалов времени, а интервалы времени ti между формируемыми выходными импульсами задают по формуле Та + 0,5 AT 1 -К TiГ К ДТ-i где коэффициент деления периода следования импульсов, Т2 - длительность последнего истекшего интервала времени между входными импульсами; AT T2 - Ti; Ti - длительность предпоследнего истекшего интервала времени между входными импульсами; i 1... К - номер интервала между выходными импульсами, формируемыми на протяжении текущего интервала времени .между входными импульсами. При этом устраняется динамическая погрешность в зна- чениях интервалов времени между выходными импульсами 5 ил. СЛ

Фиг. 1

Фиг.2

Фие.З ., vf

| Умножитель частоты | 1976 |

|

SU617803A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-23—Публикация

1985-10-21—Подача