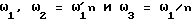

Способ измерения относительной величины удельной электрической проводимости электропроводящих изделий, включающий в себя четыре цикла измерения выходных сигналов вихретокового преобразователя, в каждом из которых осуществляют последовательное возбуждение преобразователя на трех частотах  ,

,

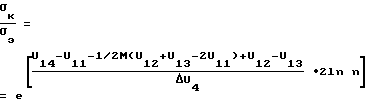

где n > 1, и измерение соответствующих сигналов U1i, U2i и U3i преобразователя, где i - номер цикла измерения, формирование из этих сигналов в первом, втором и третьем циклах сигналов корректировки S1, S2 и S3, коррекции сигналов преобразователя в первом, втором и третьем циклах до выполнения условий S1 = 0, S2 = 0, S3 = 0 соответственно и запоминания величин U1, U12, U13 и U14, причем первый и второй циклы измерения проводят при установке преобразователя на эталонный образец, во втором и третьем циклах измеряют величину мешающего параметра P, на величину ΔP, а четвертый цикл измерений проводят при установке преобразователя на контролируемый образец, отличающийся тем, что, с целью увеличения точности измерения, третий цикл измерения проводят при установке преобразователя на эталонный образец, устанавливают величину опорного напряжения Uo, сигналы S1, S2 и S3 формируют в виде S1 = 2U11 - U21 - U31, S2 = U21 - U31 + Uo - U22 + U32, S3 = U21 - U31 - Uo - U23 + U32, в первом цикле коррекцию S1 осуществляют путем итерационного изменения величин частот ω1, ω2 и ω3, находят и запоминают величину ΔU1 = U21 - U31, во втором цикле коррекцию S2 осуществляют путем итерационного изменения величины ΔP, находят и запоминают величину ΔU2 = U22 - U32, в третьем цикле коррекцию S3 осуществляют путем итерационного изменения величины ΔP, в четвертом цикле находят и запоминают величину ΔU4 = U24 - U34, а величину относительной удельной электрической проводимости материала контролируемого образца находят в виде

где  ;

;

σк, σэ - величины удельной электрической проводимости материала контролируемого и эталонного образцов соответственно.

2. Устройство для измерения относительной величины удельной электрической проводимости электропроводящих изделий, содержащее последовательно соединенные первый коммутатор, к входам которого подключены три генератора, вихретоковый преобразователь, состоящий из возбуждающей и измерительной катушек, усилитель, амплитудный детектор и второй коммутатор, а также четыре блока памяти, три первых из которых подключены к выходу второго коммутатора, три блока вычитания, компаратор, блок световой индикации, масштабный преобразователь, блок управления, выход которого подключен к управляющим входам трех генераторов, и генератор тактовых импульсов, выход которого подключен к управляющим входам первого и второго коммутаторов, причем выходы второго и третьего блоков памяти соединены соответственно с первыми и вторыми входами первого и второго блоков вычитания, выход первого блока памяти соединен через масштабный преобразователь с третьим входом первого блока вычитания, выход которого соединен с блоком управления и через компаратор с блоком световой индикации, отличающееся тем, что, с целью увеличения точности измерения, оно снабжено последовательно соединенными источником опорного напряжения, инвертирующим усилителем, третьим коммутатором и блоком сложения, последовательно соединенными первым триггером, вход которого подключен к выходу компаратора, одновибратором и вторым триггером, выход которого подключен к управляющему входу третьего коммутатора, а также вычислительным устройством, вторым компаратором, линией задержки, индикатором нуля и логическим элементом И, причем выход второго блока вычитания подключен к входу четвертого блока памяти, к первому входу вычислительного устройства и к первому входу третьего блока вычитания, второй вход которого подключен к выходу блока сложения, выход третьего блока вычитания соединен с входом индикатора нуля и через последовательно соединенные второй компаратор и логический элемент И с вторым входом второго триггера и с первым синхронизирующим входом вычислительного устройства, второй синхронизирующий вход которого и управляющий вход четвертого блока памяти соединены с выходом одновибратора, выход первого блока памяти соединен с вторым входом вычислительного устройства, выход четвертого блока памяти подключен к второму входу блока сложения, второй вход третьего коммутатора соединен с источником опорного напряжения, а линия задержки включена между выходом второго компаратора и вторым входом логического элемента И.

Авторы

Даты

2000-03-27—Публикация

1988-02-29—Подача