Изобретение относится к вычисли- тельной технике и может быть использовано для контроля выполнения операций в устройствах управления и сопряжения,

Цель изобретения - повышение полноты и достоверности контроля после- довательнос ги сигналов за счет обнаружения ошибок, вызванных нару ления- ми очередностей одиночных сигналов и параллельным поступлением нескольких сигналов, обеспечение контроля произвольных последовательностей сигналов импульсного или потенздиаль- ного вида.

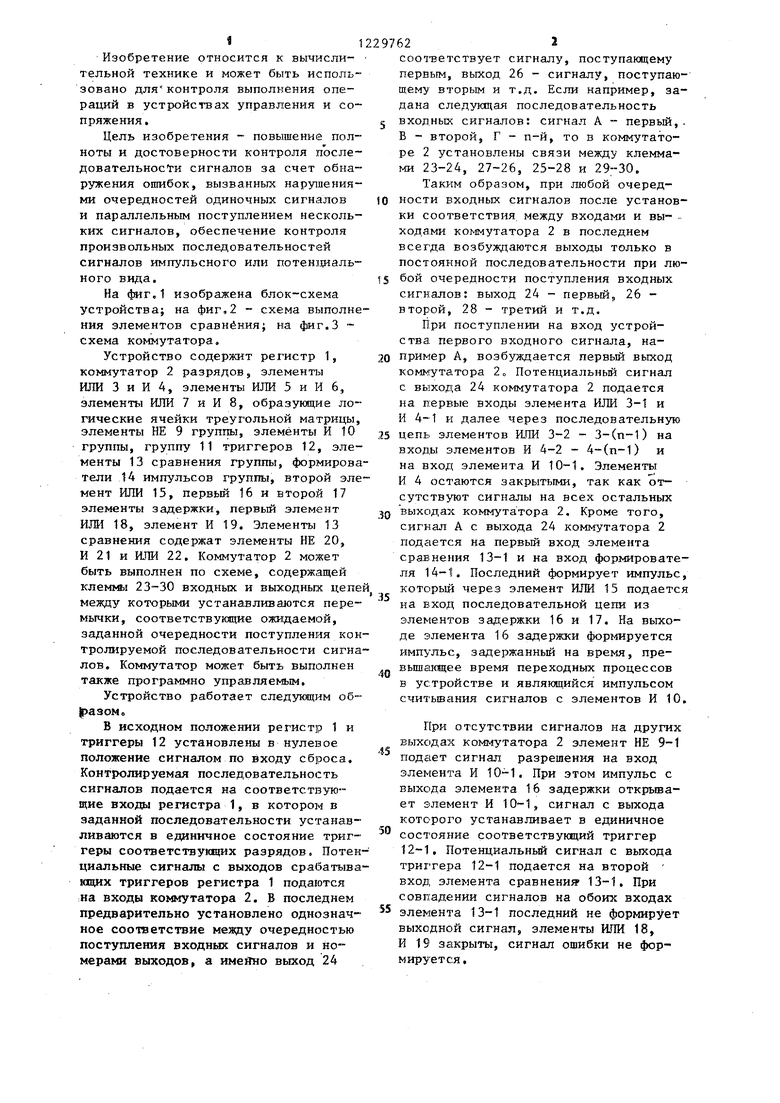

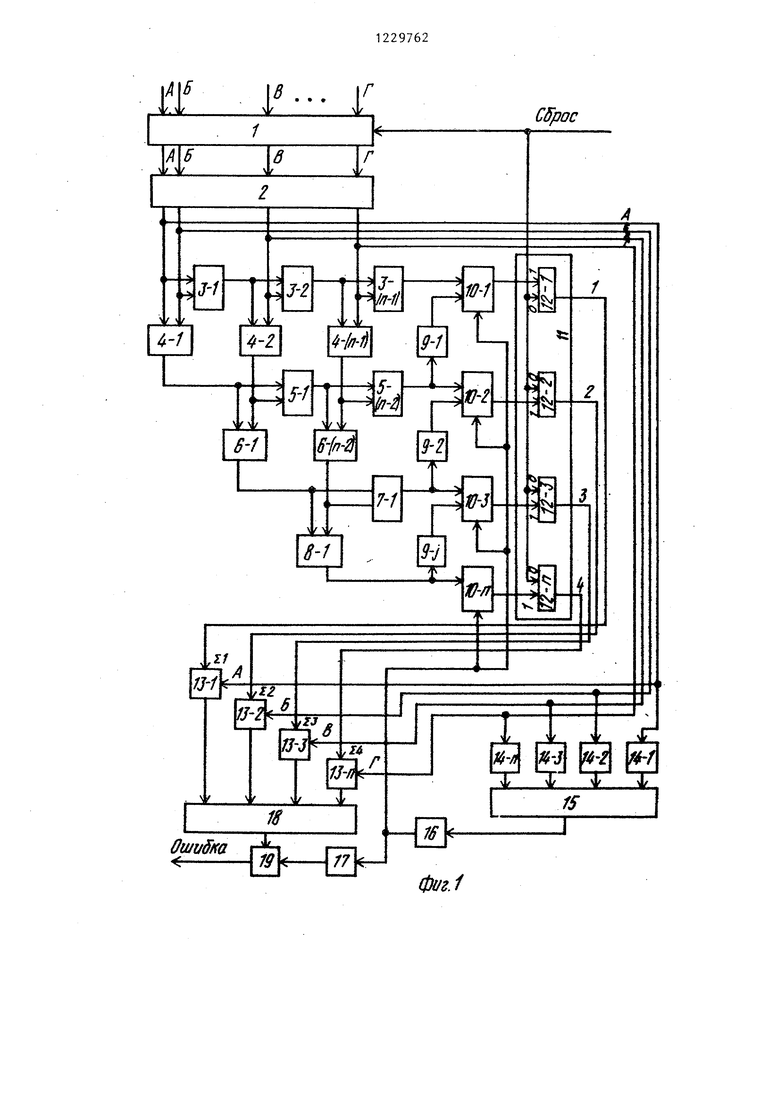

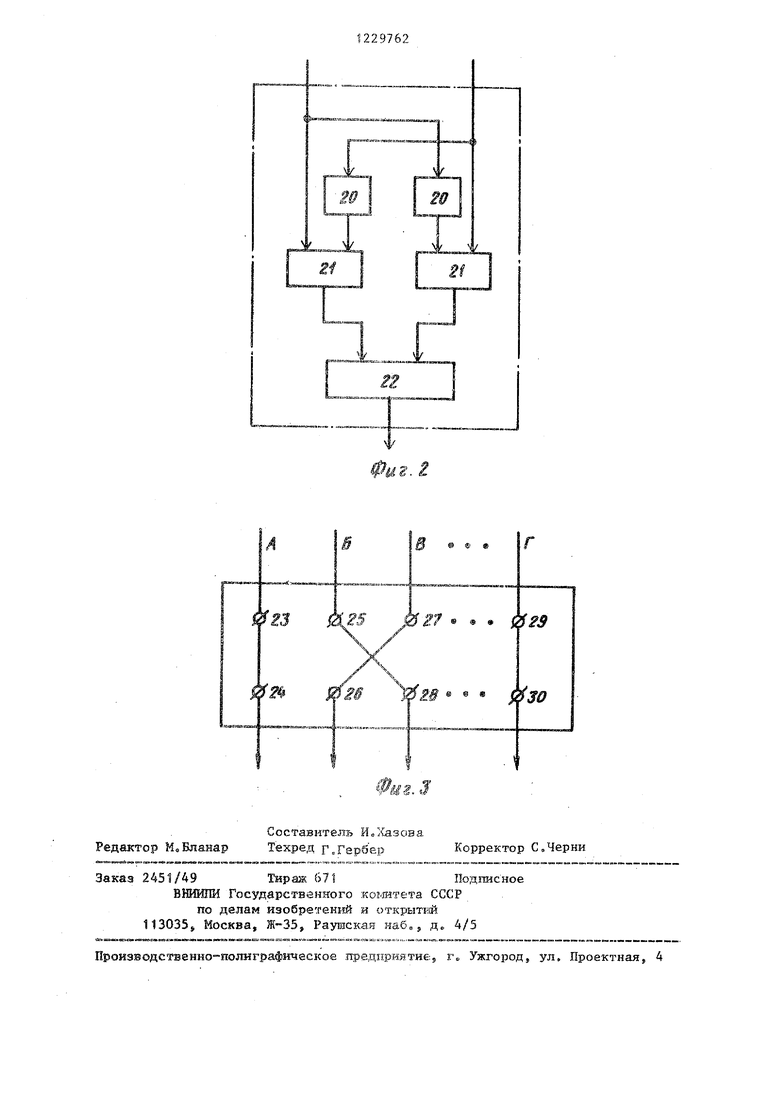

На фиг.1 изображена блок-схема устройства; на фиг,2 - схема выполнения элементов сравнения; на фиг.З - схема коммутатора.

Устройство содержит регистр 1, коммутатор 2 разрядов, элементы ИЛИ 3 и И 4, элементы ИЛИ 5 и И 6, элементы ИЛИ 7 и И 8, образующие логические ячейки треугольной матрицы, элементы НЕ 9 группы, элементы И 10 группы, группу 11 TppirrepOB 12, элементы 13 сравнения группы, формирователи 14 импульсов группы, второй элемент ИЛИ 15, первый 16 и второй 17 элементы задержки, первый элемент ИЛИ 18, элемент И 19. Элементы 13 сравнения содержат элементы НЕ 20, И 21 и ИЛИ 22. Коммутатор 2 может быть выполнен по схеме, содержащей клеммы 23-30 входных и выходных цепе между которыми устанавливается перемычки, соответствующие ожидаемой, заданной очередности поступления контролируемой последовательности сигналов. Коммутатор может быть выполнен также программно управляекым.

Устройство работает следукщим об- |)азом,

В исходном положении регистр 1 и триггеры 12 установлены в нулевое положение сигналом по входу сброса, Контролируемая последовательность сигналов подается на соответствующие входы регистра 1, в котором в заданной последовательности устанавливаются в единичное состояние триггеры соответствуицих разрядов. Потенциальные сигналы с выходов срабатывающих триггеров регистра 1 подаются на входы коммутатора 2. В последнем предварительно установлено однозначное соответствие между очередностью поступления входных сигналов и номерами выходов, а имеЯно выход 24

соответствует сигналу, поступающему первым, выход 26 - сигналу, поступающему вторым и т.д. Если например, задана следующая последовательность ВХОДНЫУ: сигналов: сигнал А - первый,. В - второй, Г - п-й, то в коммутаторе 2 установлены связи между клеммами 23-24, 27-26, 25-28 и 29-30.

Таким образом, при .гаобой очередности входных сигналов после установки соответствия между входами и вы- . хода.ми коммутатора 2 в последнем всегда возбуждаются выходы только в постоянной последовательности при любой очередности поступления входных сигналов: выход 24 - первый, 26 - второй, 28 - третий и т.д.

При поступлении на вход устройства первого входного сигнала, например А, возбуждается первый выход коммутатора 2„ Потенциальный сигнал с выхода 24 коммутатора 2 подается на первые входы элемента ИЛИ 3-1 и И 4-1 и далее через последов ательнзто цепь элементов ИЛИ 3-2 - 3-(п-1) на входы элементов И 4-2 - 4-(п-1) и на вход элемента И 10-1. Элементы И 4 остаются закрытыми, так как от- сутств тот сигналы на всех остальных выходах коммутатора 2. Кроме того, сигнал А с выхода 24 коммутатора 2 подается на первый вход элемента сравнения 13-1 и на вход фор ировате- ля 14-11. Последний формирует импульс, который через элемент ИЛИ 15 подается на вход последовательной цепи из элементов задержки 16 и 17. На выходе элемента 16 задержки формируется импульс, задержанный на время, пре- вышанадее время переходных процессов в устройстве и являюшийся импульсом считьшания сигналов с элементов И 10.

При отсутствии сигналов на других выходах коммутатора 2 элемент НЕ 9-1 подает сигнал разрешения на вход элемента И 10-1. При этом импульс с выхода элемента 16 задержки открывает элемент И 10-1, сигнал с выхода которого устанавливает в единичное состояние соответствукщий триггер 12-1. Потенциальный сигнал с выхода триггера 12-1 подается на второй вход элемента сравнения 13-1. При совпадении сигналов на обоих входах элемента 13-1 последний не формирует выходной сигнал, элементы ИЛИ 18, И 19 закрыты, сигнал ошибки не формируется.

3

При поступлении второго по очередности входного сигнала, например В, возбуждается второй выход коммутатора 2, при этом продолжает действовать сигйал на первом его выходе 24. Сигнал с выхода 26 коммутатора 2 подается на вторые входы элемента РШИ 3-1, И 4-1. Сигналы на входах элемента И 4-1 совпадают, он открьгоает- ся и подает сигнал на первые входы элементов И 6-1 и через последовательную цепь элементов ИЛИ 5-1 - ) на входы элементов И 6-(п-2) и И 10-2. Кроме того, сигнал с выхода элементаИЛИ 5-(п-2) через элемент НЕ 9-1 закрывает элемент И 10-1.Элементы И 6 остаются закпытыми, гак как отсу ствуют сигналы на последующих выходах 28-30 коммутатора 2. Аналогично второй входной сигнал с помощью формирователя 14-2 формирует импульс, который через элемент ИЛИ 15, элемент 16 задержки считьшает сигнал с элемента И 10-2 и устанавливает в единичное состояние триггер 12-2. При этом сигналы на входах элемента сравнения 13-2 также совпадают и сигнал ошибки не формируется. Аналогично работает устройство при поступлении остальных сигналов в правильной последовательности

В случае нарушения заданной очередности поступления входных сигналов, например первым поступает сигнал А, а вторым сигнал Б вместо сигнала В, устройство работает следующим образом.

Сигнал А действует аналогично описанному. Сигнал Б возбуждает третий выход 28 коммутатора 2, сигнал с которого подается на вторые входы элементов ИЛИ 3-2 и И 4-2. При этом на первый вход элемента И 4-2 подается сигнал с выхода элемента ИЛИ 3-1, открытого сигналом А с первого выхода коммутатора 2. Элемент И 4-2 открывается и через последовательную цепь элементов ИЛИ 5-1 - 5(п-2) подготавливает к открьшанию элемент И 10-2. Кроме того, сигнал с третьего выхода 28 коммутатора 2 подается на вход элемента 13-3 сравнения и через формирователь 14-3, элементы 16 и 17 задержки открьгоает элемент И 10-2. При этом срабатьшает триггер 12-2, сигнал с выхода которого подается на элемент 13-2 сравнения.

Такш образом, сигналы на входах элементов 13-2 и 13-3 сравнения не совпадают. Эти элементы формируют

29762

сигналы ошибки, которые через элементы ШШ 18 подготавлирают к открыванию элемент И 19. Импульс с выхода элемента 17 задержки открьшает эле- г мент И 19, с выхода которого на выход устройства выдается сигнал ошибки.

В случае нарушения очередности поступления входных сигналов, напри- 10 мер при параллельном поступлении сигналов А и В вместо одного сигнала А, устройство работает следующим образом.

При параллельном поступлении сиг- 15 налов А и В одновременно возбуждаются выходы 24 и 26 коммутатора 2. Сигнал с выхода 24 подается на первый вход элемента И 4-1 и через элементы ИЛИ 3 на вход элемента И 10-1. Сиг- 2Q нал с выхода 26 коммутатора 2 открывает элемент И 4-1, сигнал с выхода которого через элементы ИЛИ 5 подается на вход элемента И 10-2 и через элемент НЕ 9-1 закрывает элемент И 25 10-1.

Таким образом, импульс считьюанкя с выхода элемента 16 задержки открывает только элемент И 10-2, при этом срабатьшает триггер 12-2 и сигналы на входах элемента 13-2 сравнения совпадут. Однако из-за того, что элемент И 10-1 закрыт, триггер 12-1 не срабатьюает и сигналы на входах элемента 13-1 сравнения не совпадают. Элемент 13-1 сравнения формирует сиг- нал ошибки, который поступает на выход устройства.

Аналогично работает устройство при всех других комбинациях наруше- 1ний очередности контролируемых сиг- налов.

Формула изо.бретения

Устройство для контроля последо- вательности сигналов, содержащее регистр, входы которого являются входами устройства, а выходы соединены с входами коммутатора разрядов, группу элементов И, группу триггеров, 50 входы сброса которых подключены к

входу сброса устройства, элементы задержки, группу элементов сравнения, выходы которых подключены к входам первого элемента ИЛИ, а первые и вто- 55 рые входы - соответственно к выходам коммутатора разрядов и триггеров группы, отличающееся тем, что, с целью повышения полноты к до-

30

стоверности контроля, в него введены группа элементов НЕ, группа формирователей импулбсов, второй элемент ИЛИ, элемент И и треугольная матри™ ца 2(п-1)х() логических ячеек, где п - разрядность регистра, каждая из которых содержит элемент ИЛИ и элемент И, первые и вторые входы

которых объединены и являются СООТ-

ветственно первым и вторым входами логической ячейки, а выходы - соответственно первым и вторым выходами ячейки, при этом первые входы логических ячеек первой строки матрицы соединены соответственно с второго по п-й выходами коммутатора разрядов второй вход первой логаческой ячейки первой строки подключен к первому выходу кo м yтaтopa разрядов, в каздо строке матрицы первый выход j-и логической ячейки fJ 1,,,. (п-2У соединен с вторым входом 0+1)-й логической ячейки, первый вход логической ячейки t -и строки L 2... ( со единен с вторым выходом ( + 1)-й логической ячейки ()™й строки матрицы, второй выход первой логической

ячейки каждой строки соединен с вторым входом первой логической ячейки последующей строки, первые выходы логических ячеек (n-l)-ro столбца и второй выход (п-1)-й логической ячейки (n-l)-ro столбца матрицы соединены соответственно с первыми входами элементов И группы, выходы которых . соединены с установочными входами триггеров группы, выходы коммутатора разрядов с единены через соответствующие формирователи импульсов труппы с входами второго элемента ИЛИ, выход которого через первый элемент задержки соединен с вторыми входами элементов И группы и входом второго элемента эадержки, выход которого соединен с первым входом элемента И, второй вход коччзрого соединен с выходом первого элемента ИЛИ, а выход является выходом ошибки устройства, первые выходы логических ячеек 1 -и строки через соответствующие элементы НЕ группы соединены с третьими входами (i-1)-x элементов И группы, вход сброса устройства соединен с входом сброса регистра.

у.

фиг.1

w

f

L

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1983 |

|

SU1157545A1 |

| Устройство для регистрации информации | 1985 |

|

SU1355984A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЯ ОБЪЕКТА | 1992 |

|

RU2054196C1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1987 |

|

SU1474727A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для передачи и приема информации | 1983 |

|

SU1156109A1 |

| Логический анализатор | 1986 |

|

SU1381512A1 |

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля выполнения операций в устройствах управления и сопряжения. Целью изобретения является повьшение полноты и достоверности контроля. Устройство содержит регистр, коммутатор разрядов, элемен- ты И, ИЛИ, образующие ячейки треугольной матрицы, группу элементов И, элементы НЕ, группу триггеров, группу элементов сравнения, группу формирователей импульсов, элементы задержки И, ИЛИ, НЕ. Цепь достигается за счет возможности обнаружения нарушения очередности поступления сигналов, одновременного поступления нескольких СИГНАЛОВ, обеспечения контроля произвольных последовательностей сигналов импульсного или потенциального вида. 3 ил. (Л

. 0/S

X

Wi

Редактор М Бланар

Составитель И /Чазова Техред г.Гербер

Заказ 2451/49 Тираж 671Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытки 113035s Москва, Ж-35, Раушская наб, Д. 4/5

Прокзводственно-поляграф Ическое предприятие;j г Ужгород, ул. Проектная, 4

Корректор С вЧерни

| Устройство для контроля выполненияпОСлЕдОВАТЕльНОСТи дЕйСТВий ОпЕРАТОРА | 1978 |

|

SU807300A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| СХЕМА КОНТРОЛЯ ПРАВИЛЬНОСТИ ЗАПИСИ ЧИСЛА В РЕГИСТРЕ | 0 |

|

SU296109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-07—Публикация

1984-02-24—Подача