Изобретение относится к вычислительной технике и цифровой автоматике и может быть использовано в системах передачи данных для адаптации периферийного интерфейса связи с двунаправленным параллельным интерфейсом.

Целью изобретения является повышение быстродействия.

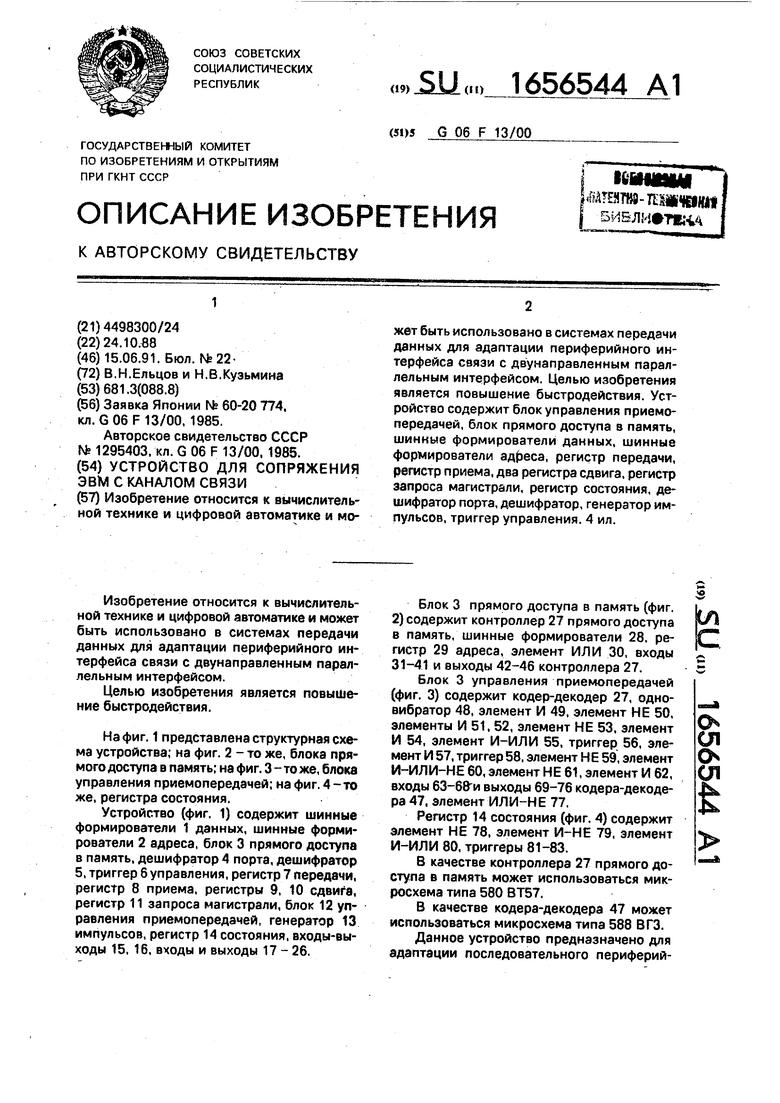

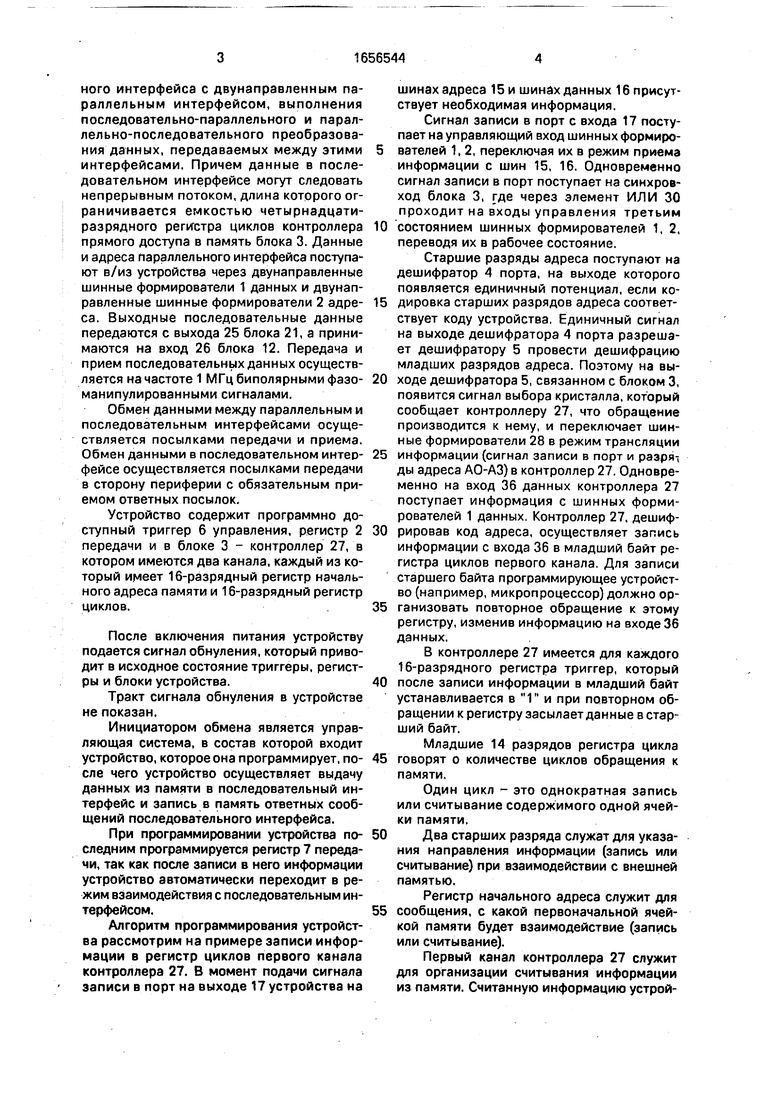

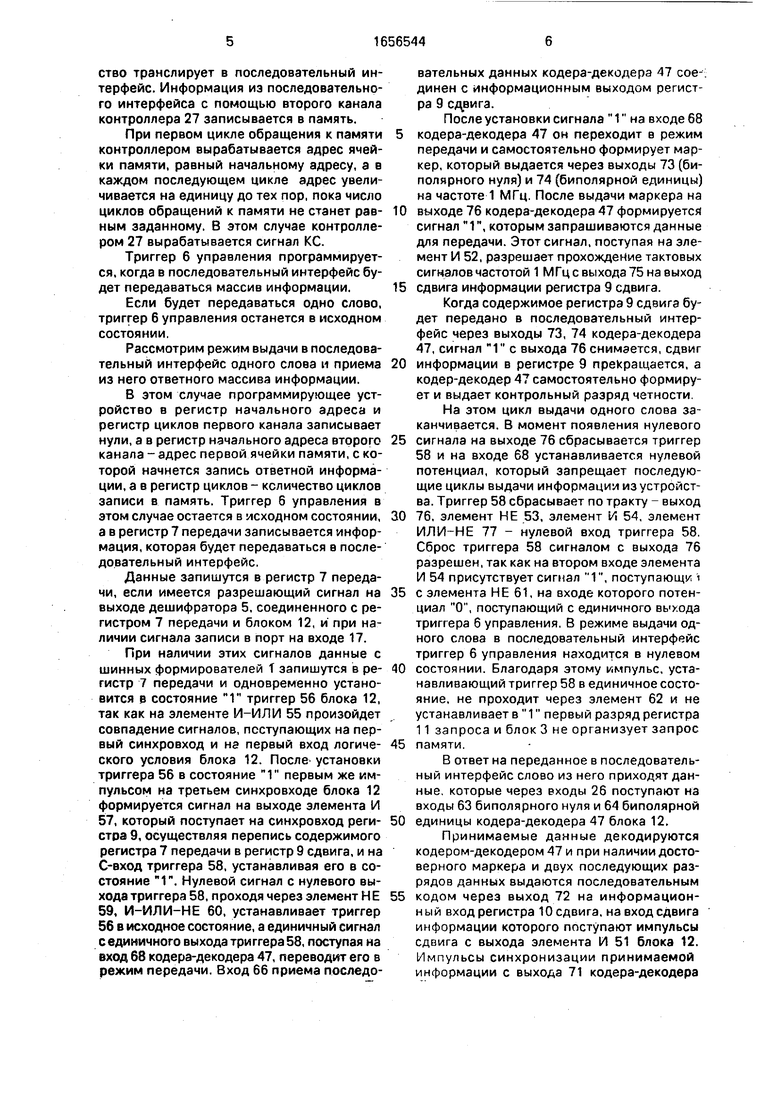

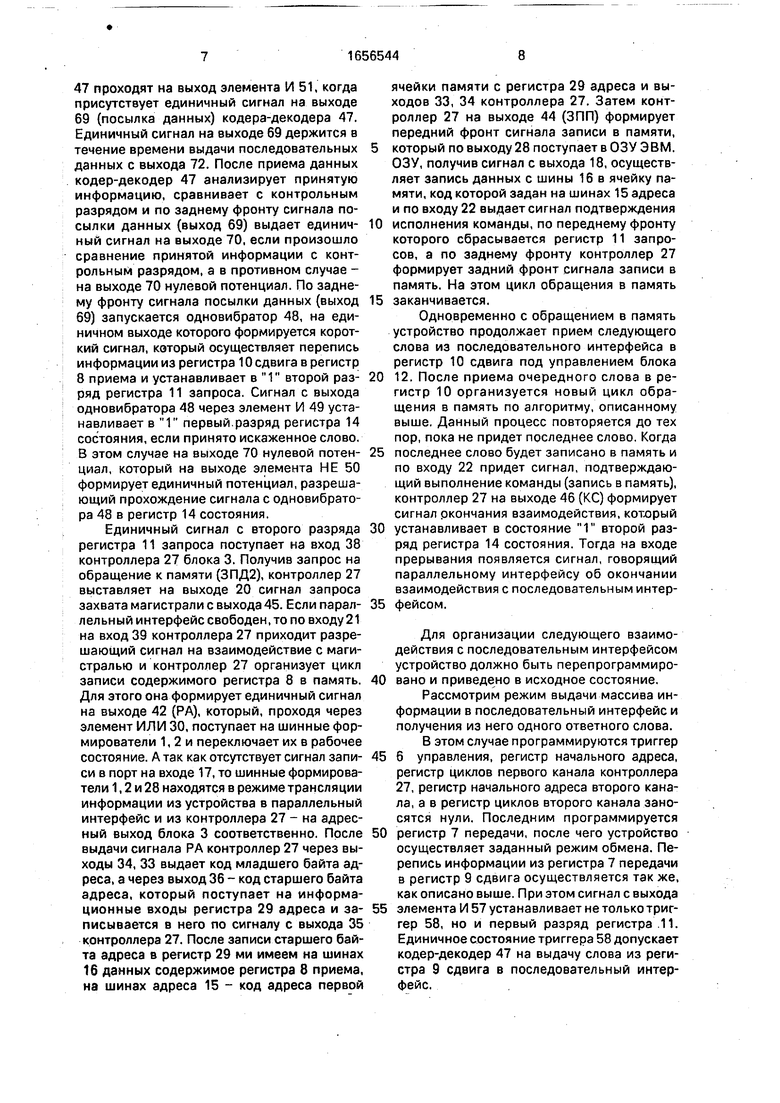

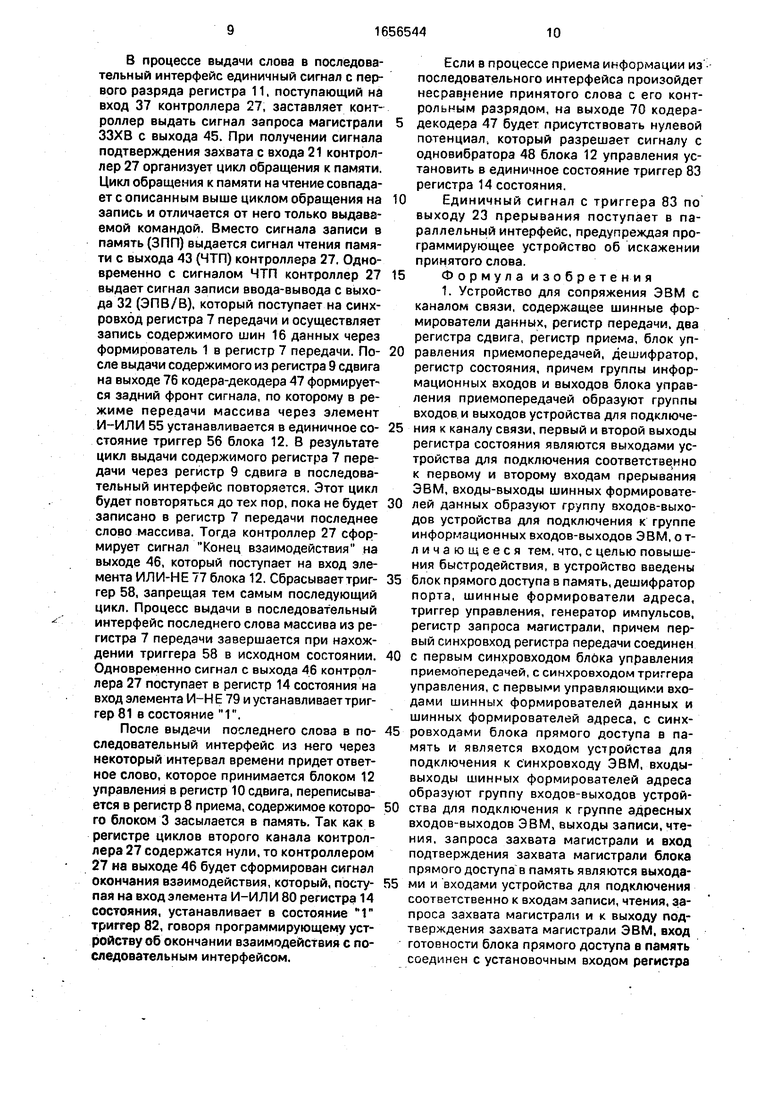

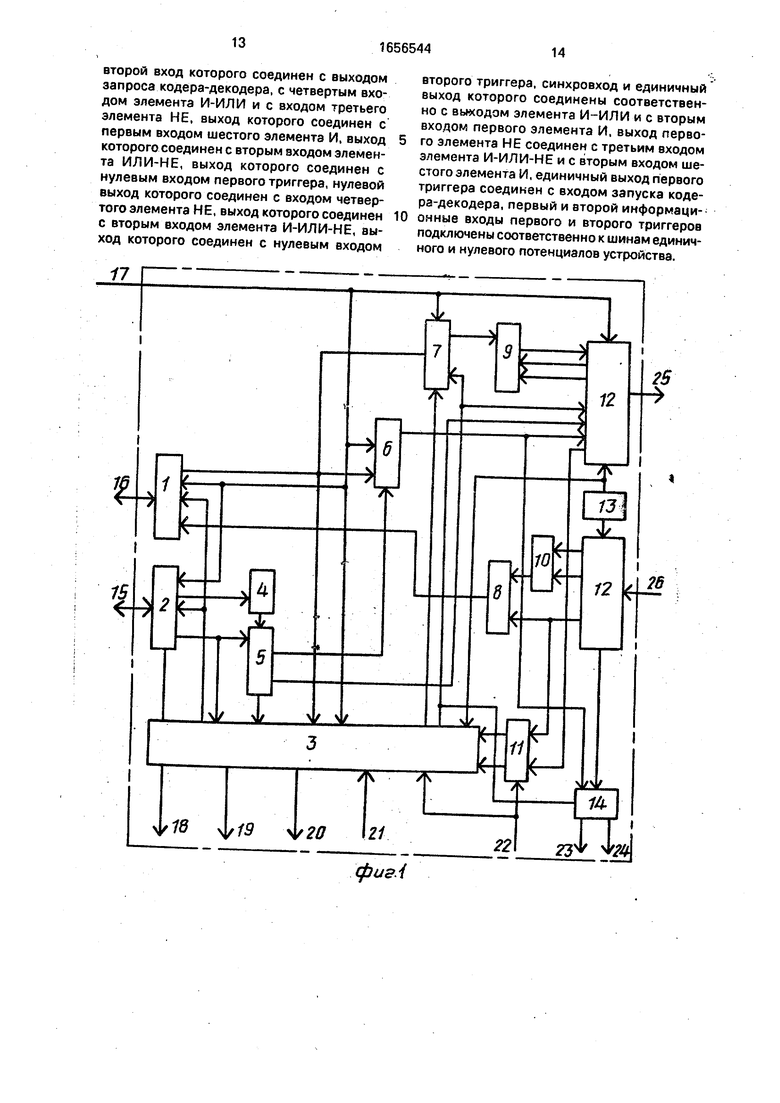

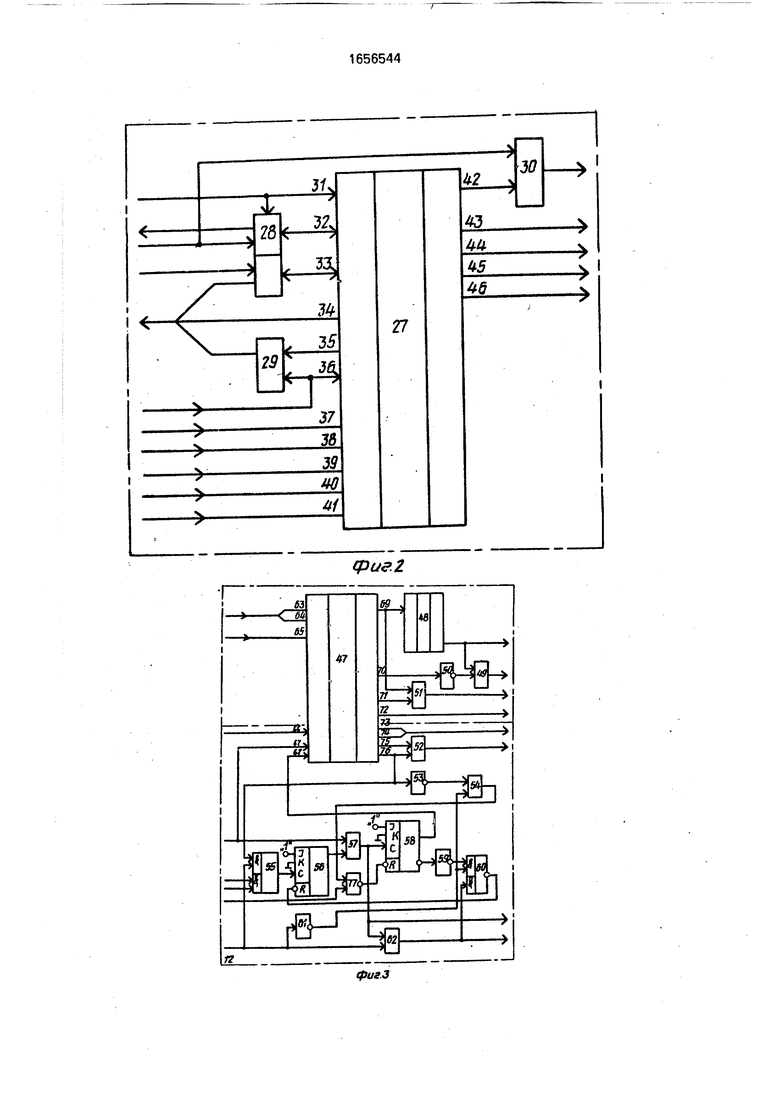

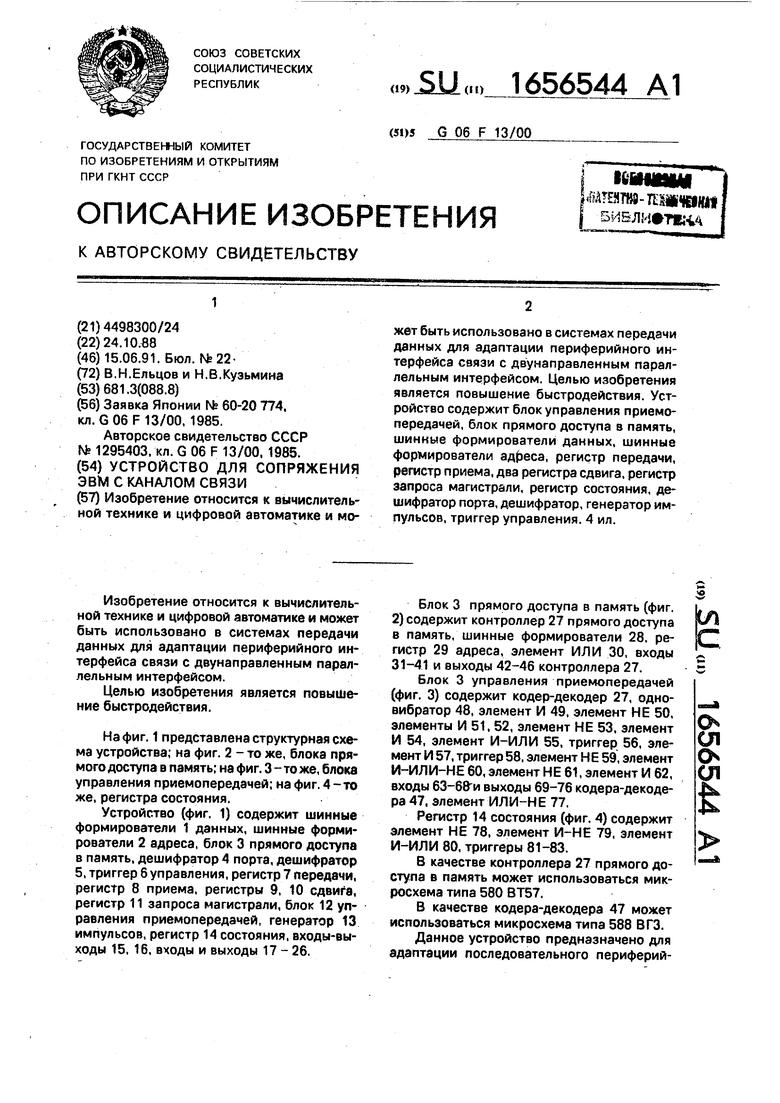

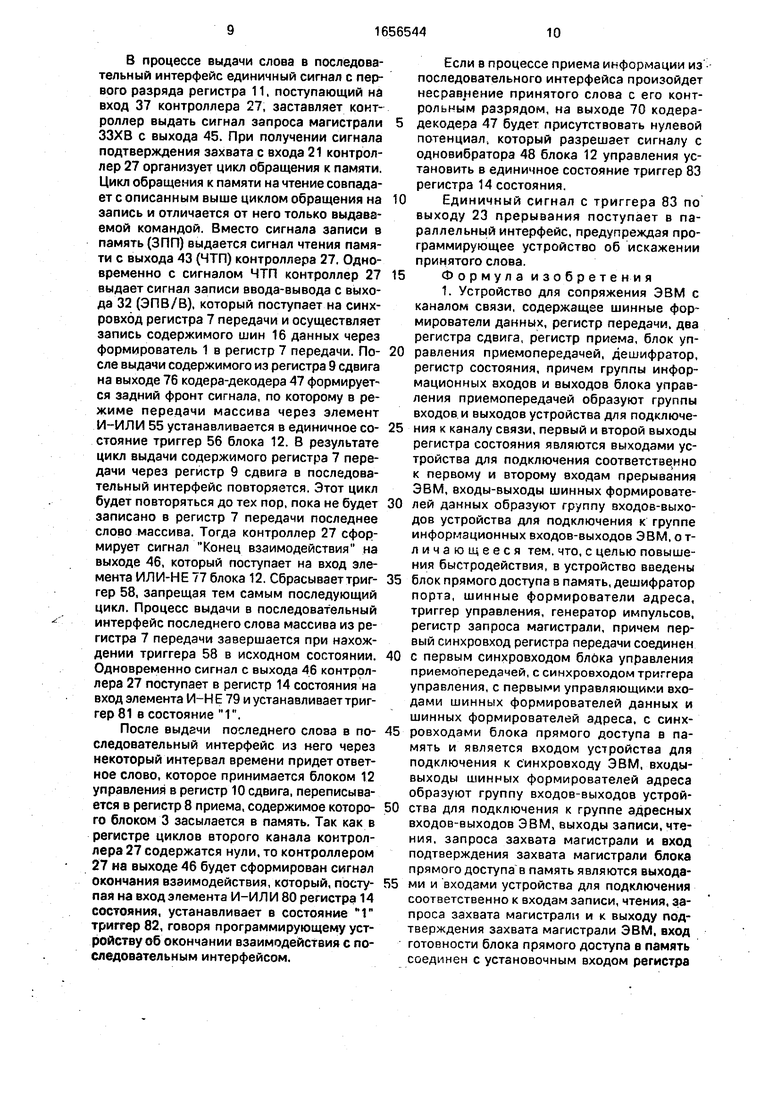

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - то же, блока прямого доступа в память; на фиг. 3 - то же, блока управления приемопередачей; на фиг. 4 -то же, регистра состояния.

Устройство (фиг. 1) содержит шинные формирователи 1 данных, шинные формирователи 2 адреса, блок 3 прямого доступа в память, дешифратор 4 порта, дешифратор 5, триггер 6 управления, регистр 7 передачи, регистр 8 приема, регистры 9, 10 сдвига, регистр 11 запроса магистрали, блок 12 управления приемопередачей, генератор 13 импульсов, регистр 14 состояния, входы-выходы 15, 16, входы и выходы 17 - 26.

Блок 3 прямого доступа в память (фиг. 2) содержит контроллер 27 прямого доступа в память, шинные формирователи 28. регистр 29 адреса, элемент ИЛИ 30, входы 31-41 и выходы 42-46 контроллера 27.

Блок 3 управления приемопередачей (фиг. 3) содержит кодер-декодер 27, одно- вибратор 48, элемент И 49. элемент НЕ 50, элементы И 51, 52, элемент НЕ 53, элемент И 54, элемент И-ИЛИ 55, триггер 56, элемент И 57, триггер 58, элемент НЕ 59, элемент И-ИЛИ-НЕ 60, элемент НЕ 61, элемент И 62, входы 63-68 выходы 69-76 кодера-декодера 47, элемент ИЛИ-НЕ 77.

Регистр 14 состояния (фиг. 4) содержит элемент НЕ 78, элемент И-НЕ 79, элемент И-ИЛИ 80, триггеры 81-83.

В качестве контроллера 27 прямого доступа в память может использоваться микросхема типа 580 ВТ57.

В качестве кодера-декодера 47 может использоваться микросхема типа 588 ВГЗ.

Данное устройство предназначено для адаптации последовательного периферийО (Я

сх

01

fc

ного интерфейса с двунаправленным параллельным интерфейсом, выполнения последовательно-параллельного и параллельно-последовательного преобразования данных, передаваемых между этими интерфейсами. Причем данные в последовательном интерфейсе могут следовать непрерывным потоком, длина которого ограничивается емкостью четырнадцатиразрядного регистра циклов контроллера прямого доступа в память блока 3. Данные и адреса параллельного интерфейса поступа- ют в/из устройства через двунаправленные шинные формирователи 1 данных и двунаправленные шинные формирователи 2 адреса. Выходные последовательные данные передаются с выхода 25 блока 21, а принимаются на вход 26 блока 12. Передача и прием последовательных данных осуществляется на частоте 1 МГц биполярными фазо- манипулированными сигналами,

Обмен данными между параллельным и последовательным интерфейсами осуществляется посылками передачи и приема. Обмен данными в последовательном интерфейсе осуществляется посылками передачи в сторону периферии с обязательным приемом ответных посылок.

Устройство содержит программно доступный триггер 6 управления, регистр 2 передачи и в блоке 3 - контроллер 27, в котором имеются два канала, каждый из который имеет 16-разрядный регистр начального адреса памяти и 16-разрядный регистр циклов.

После включения питания устройству подается сигнал обнуления, который приводит в исходное состояние триггеры, регистры и блоки устройства.

Тракт сигнала обнуления в устройстве не показан.

Инициатором обмена является управляющая система, в состав которой входит устройство, которое она программирует, после чего устройство осуществляет выдачу данных из памяти в последовательный интерфейс и запись в память ответных сообщений последовательного интерфейса.

При программировании устройства последним программируется регистр 7 передачи, так как после записи в него информации устройство автоматически переходит в режим взаимодействия с последовательным интерфейсом.

Алгоритм программирования устройства рассмотрим на примере записи информации в регистр циклов первого канала контроллера 27. В момент подачи сигнала записи в порт на выходе 17 устройства на

шинах адреса 15 и шинах данных 16 присутствует необходимая информация.

Сигнал записи в порт с входа 17 поступает на управляющий вход шинных формирователей 1, 2, переключая их в режим приема информации с шин 15, 16. Одновременно сигнал записи в порт поступает на синхрош- ход блока 3, где через элемент ИЛИ 30 проходит на входы управления третьим

0 состоянием шинных формирователей 1, 2, переводя их в рабочее состояние.

Старшие разряды адреса поступают на дешифратор 4 порта, на выходе которого появляется единичный потенциал, если ко5 дировка старших разрядов адреса соответствует коду устройства. Единичный сигнал на выходе дешифратора 4 порта разрешает дешифратору 5 провести дешифрацию младших разрядов адреса. Поэтому на вы0 ходе дешифратора 5, связанном с блоком 3, появится сигнал выбора кристалла, который сообщает контроллеру 27, что обращение производится к нему, и переключает шинные формирователи 28 в режим трансляции

5 информации (сигнал записи в порт и разря ды адреса АО-АЗ) в контроллер 27. Одновременно на вход 36 данных контроллера 27 поступает информация с шинных формирователей 1 данных. Контроллер 27, дешиф0 рировав код адреса, осуществляет запись информации с входа 36 в младший байт регистра циклов первого канала. Для записи старшего байта программирующее устройство (например, микропроцессор) должно ор5 ганизовать повторное обращение к этому регистру, изменив информацию на входе 36 данных,

В контроллере 27 имеется для каждого 16-разрядного регистра триггер, который

0 после записи информации в младший байт устанавливается в Г и при повторном обращении к регистру засылает данные в старший байт.

Младшие 14 разрядов регистра цикла

5 говорят о количестве циклов обращения к памяти.

Один цикл - это однократная запись или считывание содержимого одной ячейки памяти.

0 Два старших разряда служат для указания направления информации (запись или считывание) при взаимодействии с внешней памятью.

Регистр начального адреса служит для

5 сообщения, с какой первоначальной ячейкой памяти будет взаимодействие (запись или считывание).

Первый канал контроллера 27 служит для организации считывания информации из памяти. Считанную информацию устройство транслирует в последовательный интерфейс. Информация из последовательного интерфейса с помощью второго канала контроллера 27 записывается в память.

При первом цикле обращения к памяти контроллером вырабатывается адрес ячейки памяти, равный начальному адресу, а в каждом последующем цикле адрес увеличивается на единицу до тех пор, пока число циклов обращений к памяти не станет равным заданному. В этом случае контроллером 27 вырабатывается сигнал КС.

Триггер 6 управления программируется, когда в последовательный интерфейс будет передаваться массив информации.

Если будет передаваться одно слово, триггер б управления останется в исходном состоянии.

Рассмотрим режим выдачи в последовательный интерфейс одного слова и приема из него ответного массива информации.

В этом случае программирующее устройство в регистр начального адреса и регистр циклов первого канала записывает нули, а в регистр начального адреса второго канала - адрес первой ячейки памяти, с которой начнется запись ответной информации, а в регистр циклов - количество циклов записи в память. Триггер 6 управления в этом случае остается в исходном состоянии, а в регистр 7 передачи записывается информация, которая будет передаваться в последовательный интерфейс.

Данные запишутся в регистр 7 передачи, если имеется разрешающий сигнал на выходе дешифратора 5, соединенного с регистром 7 передачи и блоком 12. и при наличии сигнала записи в порт на входе 17.

При наличии этих сигналов данные с шинных формирователей Т запишутся в регистр 7 передачи и одновременно установится в состояние Г триггер 56 блока 12, так как на элементе И-ИЛИ 55 произойдет совпадение сигналов, поступающих на первый синхровход и на первый вход логического условия блока 12. После установки триггера 56 в состояние 1 первым же импульсом на третьем синхровходе блока 12 формируется сигнал на выходе элемента И 57, который поступает на синхровход регистра 9, осуществляя перепись содержимого регистра 7 передачи в регистр 9 сдвига, и на С-вход триггера 58, устанавливая его в состояние 1. Нулевой сигнал с нулевого выхода триггера 58, проходя через элемент НЕ 59, И-ИЛИ-НЕ 60, устанавливает триггер 56 в исходное состояние, а единичный сигнал с единичного выхода триггера 58, поступая на вход 68 кодера-декодера 47, переводит его в режим передачи. Вход 66 приема последовательных данных кодера-декодера 47 соединен с информационным выходом регист ра 9 сдвига.

После установки сигнала 1 на входе 68 кодера-декодера 47 он переходит в режим передачи и самостоятельно формирует маркер, который выдается через выходы 73 (биполярного нуля) и 74 (биполярной единицы) на частоте 1 МГц. После выдачи маркера на

0 выходе 76 кодера-декодера 47 формируется сигнал 1, которым запрашиваются данные для передачи. Этот сигнал, поступая на элемент И 52, разрешает прохождение тактовых сигналов частотой 1 МГц с выхода 75 на выход

5 сдвига информации регистра 9 сдвига.

Когда содержимое регистра 9 сдвига будет передано в последовательный интерфейс через выходы 73, 74 кодера-декодера 47, сигнал 1 с выхода 76 снимается, сдвиг

0 информации в регистре 9 прекращается, а кодер-декодер 47 самостоятельно формирует и выдает контрольный разряд четности

На этом цикл выдачи одного слова заканчивается. В момент появления нулевого

5 сигнала на выходе 76 сбрасывается триггер 58 и на входе 68 устанавливается нулевой потенциал, который запрещает последующие циклы выдачи информации из устройства. Триггер 58 сбрасывает по тракту - выход

0 76, элемент НЕ 53, элемент И 54, элемент ИЛИ-НЕ 77 - нулевой вход триггера 58. Сброс триггера 58 сигналом с выхода 76 разрешен, так как на втором входе элемента И 54 присутствует сигнал 1, поступаюшу i

5 с элемента НЕ 61, на входе которого потенциал О, поступающий с единичного выхода триггера 6 управления. В режиме выдачи одного слова в последовательный интерфейс триггер 6 управления находится в нулевом

0 состоянии. Благодаря этому импульс, устанавливающий триггер 58 в единичное состояние, не проходит через элемент 62 и не устанавливает в 1 первый разряд регистра 11 запроса и блок 3 не организует запрос

5 памяти.

В ответ на переданное в последовательный интерфейс слово из него приходят данные, которые через входы 26 поступают на входы 63 биполярного нуля и 64 биполярной

0 единицы кодера-декодера 47 блока 12.

Принимаемые данные декодируются кодером-декодером 47 и при наличии достоверного маркера и двух последующих разрядов данных выдаются последовательным

5 кодом через выход 72 на информационный вход регистра 10 сдвига, на вход сдвига информации которого поступают импульсы сдвига с выхода элемента И 51 блока 12. Импульсы синхронизации принимаемой информации с выхода 71 кодера-декодера

47 проходят на выход элемента И 51, когда присутствует единичный сигнал на выходе 69 (посылка данных) кодера-декодера 47. Единичный сигнал на выходе 69 держится в течение времени выдачи последовательных данных с выхода 72. После приема данных кодер-декодер 47 анализирует принятую информацию, сравнивает с контрольным разрядом и по заднему фронту сигнала посылки данных (выход 69) выдает единичный сигнал на выходе 70, если произошло сравнение принятой информации с контрольным разрядом, а в противном случае - на выходе 70 нулевой потенциал. По заднему фронту сигнала посылки данных (выход 69) запускается одновибратор 48, на единичном выходе которого формируется короткий сигнал, который осуществляет перепись информации из регистра 10 сдвига в регистр 8 приема и устанавливает в 1 второй разряд регистра 11 запроса. Сигнал с выхода одновибратора 48 через элемент И 49 устанавливает в 1 первый разряд регистра 14 состояния, если принято искаженное слово. В этом случае на выходе 70 нулевой потенциал, который на выходе элемента НЕ 50 формирует единичный потенциал, разрешающий прохождение сигнала с одновибратора 48 в регистр 14 состояния.

Единичный сигнал с второго разряда регистра 11 запроса поступает на вход 38 контроллера 27 блока 3. Получив запрос на обращение к памяти (ЗПД2), контроллер 27 выставляет на выходе 20 сигнал запроса захвата магистрали с выхода 45. Если параллельный интерфейс свободен, то по входу21 на вход 39 контроллера 27 приходит разрешающий сигнал на взаимодействие с магистралью и контроллер 27 организует цикл записи содержимого регистра 8 в память. Для этого она формирует единичный сигнал на выходе 42 (РА), который, проходя через элемент ИЛИ 30, поступает на шинные формирователи 1,2 и переключает их в рабочее состояние. А так как отсутствует сигнал записи в порт на входе 17, то шинные формирователи 1,2 и 28 находятся в режиме трансляции информации из устройства в параллельный интерфейс и из контроллера 27 - на адресный выход блока 3 соответственно. После выдачи сигнала РА контроллер 27 через выходы 34, 33 выдает код младшего байта адреса, а через выход 36 - код старшего байта адреса, который поступает на информационные входы регистра 29 адреса и записывается в него по сигналу с выхода 35 контроллера 27. После записи старшего байта адреса в регистр 29 ми имеем на шинах 16 данных содержимое регистра 8 приема, на шинах адреса 15 - код адреса первой

ячейки памяти с регистра 29 адреса и выходов 33, 34 контроллера 27, Затем контроллер 27 на выходе 44 (ЗПП) формирует передний фронт сигнала записи в памяти,

который по выходу 28 поступает в ОЗУ ЭВМ. ОЗУ, получив сигнал с выхода 18, осуществляет запись данных с шины 16 в ячейку памяти, код которой задан на шинах 15 адреса и по входу 22 выдает сигнал подтверждения

исполнения команды, по переднему фронту которого сбрасывается регистр 11 запросов, а по заднему фронту контроллер 27 формирует задний фронт сигнала записи в память. На этом цикл обращения в память

заканчивается.

Одновременно с обращением в память устройство продолжает прием следующего слова из последовательного интерфейса в регистр 10 сдвига под управлением блока

12. После приема очередного слова в регистр 10 организуется новый цикл обращения в память по алгоритму, описанному выше. Данный процесс повторяется до тех пор, пока не придет последнее слово. Когда

последнее слово будет записано в память и по входу 22 придет сигнал, подтверждающий выполнение команды (запись в память), контроллер 27 на выходе 46 (КС) формирует сигнал окончания взаимодействия, который

устанавливает в состояние 1 второй разряд регистра 14 состояния. Тогда на входе прерывания появляется сигнал, говорящий параллельному интерфейсу об окончании взаимодействия с последовательным интерфейсом.

Для организации следующего взаимодействия с последовательным интерфейсом устройство должно быть перепрограммировано и приведено в исходное состояние.

Рассмотрим режим выдачи массива информации в последовательный интерфейс и получения из него одного ответного слова, В этом случае программируются триггер

6 управления, регистр начального адреса, регистр циклов первого канала контроллера 27, регистр начального адреса второго канала, а в регистр циклов второго канала заносятся нули. Последним программируется

регистр 7 передачи, после чего устройство осуществляет заданный режим обмена. Перепись информации из регистра 7 передачи в регистр 9 сдвига осуществляется так же, как описано выше. При этом сигнал с выхода

элемента И 57 устанавливает не только триггер 58, но и первый разряд регистра 11. Единичное состояние триггера 58 допускает кодер-декодер 47 на выдачу слова из регистра 9 сдвига в последовательный интерфейс.

В процессе выдачи слова в последовательный интерфейс единичный сигнал с первого разряда регистра 11, поступающий на вход 37 контроллера 27, заставляет контроллер выдать сигнал запроса магистрали ЗЗХВ с выхода 45. При получении сигнала подтверждения захвата с входа 21 контроллер 27 организует цикл обращения к памяти, Цикл обращения к памяти на чтение совпадает с описанным выше циклом обращения на запись и отличается от него только выдаваемой командой. Вместо сигнала записи в память (ЗПП) выдается сигнал чтения памяти с выхода 43 (ЧТП) контроллера 27. Одновременно с сигналом ЧТП контроллер 27 выдает сигнал записи ввода-вывода с выхода 32 (ЭПВ/В), который поступает на синх- ровход регистра 7 передачи и осуществляет запись содержимого шин 16 данных через формирователь 1 в регистр 7 передачи. После выдачи содержимого из регистра 9 сдвига на выходе 76 кодера-декодера 47 формируется задний фронт сигнала, по которому в режиме передачи массива через элемент И-ИЛИ 55 устанавливается в единичное состояние триггер 56 блока 12. В результате цикл выдачи содержимого регистра 7 передачи через регистр 9 сдвига в последовательный интерфейс повторяется. Этот цикл будет повторяться до тех пор, пока не будет записано в регистр 7 передачи последнее слово массива. Тогда контроллер 27 сформирует сигнал Конец взаимодействия на выходе 46, который поступает на вход элемента ИЛИ-НЕ 77 блока 12. Сбрасывает триггер 58, запрещая тем самым последующий цикл. Процесс выдачи в последовательный интерфейс последнего слова массива из регистра 7 передачи завершается при нахождении триггера 58 в исходном состоянии. Одновременно сигнал с выхода 46 контроллера 27 поступает в регистр 14 состояния на вход элемента И-Н Е 79 и устанавливает триггер 81 в состояние Г.

После выдачи последнего слова в последовательный интерфейс из него через некоторый интервал времени придет ответное слово, которое принимается блоком 12 управления в регистр 10 сдвига, переписывается в регистр 8 приема, содержимое которого блоком 3 засылается в память. Так как в регистре циклов второго канала контроллера 27 содержатся нули, то контроллером 27 на выходе 46 будет сформирован сигнал окончания взаимодействия, который, поступая на вход элемента И-ИЛИ 80 регистра 14 состояния, устанавливает в состояние 1 триггер 82, говоря программирующему устройству об окончании взаимодействия с последовательным интерфейсом.

Если в процессе приема информации из последовательного интерфейса произойдет несравнение принятого слова с его контрольным разрядом, на выходе 70 кодера- декодера 47 будет присутствовать нулевой потенциал, который разрешает сигналу с одновибратора 48 блока 12 управления установить в единичное состояние триггер 83 регистра 14 состояния.

0Единичный сигнал с триггера 83 по

выходу 23 прерывания поступает в параллельный интерфейс, предупреждая программирующее устройство об искажении принятого слова.

5 Формула изобретения

1. Устройство для сопряжения ЭВМ с каналом связи, содержащее шинные формирователи данных, регистр передачи, два регистра сдвига регистр приема, блок уп0 равления приемопередачей, дешифратор, регистр состояния, причем группы информационных входов и выходов блока управления приемопередачей образуют группы входов и выходов устройства для подключе5 ния к каналу связи, первый и второй выходы регистра состояния являются выходами устройства для подключения соответственно к первому и второму входам прерывания ЭВМ, входы-выходы шинных формировате0 лей данных образуют группу входов-выходов устройства для подключения к группе информационных входов-выходов ЭВМ, отличающееся тем, что, с целью повышения быстродействия, в устройство введены

5 блок прямого доступа в память, дешифратор порта, шинные формирователи адреса, триггер управления, генератор импульсов, регистр запроса магистрали, причем первый синхровход регистра передачи соединен

0 с первым синхровходом блика управления приемопередачей, с синхровходом триггера управления, с первыми управляющими входами шинных формирователей данных и шинных формирователей адреса, с синх5 ровходами блока прямого доступа в память и является входом устройства для подключения к синхровходу ЭВМ, входы- выходы шинных формирователей адреса образуют группу входов-выходов устрой0 ства для подключения к группе адресных входов-выходов ЭВМ, выходы записи, чтения, запроса захвата магистрали и вход подтверждения захвата магистрали блока прямого доступа в память являются выхода5 ми и входами устройства для подключения соответственно к входам записи, чтения, запроса захвата магистрали и к выходу подтверждения захвата магистрали ЭВМ, вход готовности блока прямого доступа в память соединен с установочным входом регистре

запроса магистрали и является входом устройства для подключения к выходу подтверждения выполнения команды ЭВМ, при этом информационные выходы шинных формирователей данных соединены с ин- формационными входами блока прямого доступа в память, триггера управления, регистра передачи, информационный выход регистра передачи соединен с информационным входом первого регистра сдвига, ин- формационный выход, синхровход и вход сдвига которых соединены соответственно с информационным входом, с первым и вторым выходами блока управления приемопе- редачей, первый вход логического условия которого соединен с входом записи регистра передачи и с первым выходом дешифратора, второй выход которого соединен с разрешающим входом триггера управления, единичный выход которого соединен с пер- вым установочным входом регистра состояния и с вторым входом логического условия блока управления приемопередачей, второй синхровход которого соединен с первым син- хровыходом генератора импульсов, второй синхровыход которого соединен с тактовым входом блока прямого доступа в память и с третьим синхровходом блока управления приемопередачей, третий вход логического условия которого соединен с выходом окон- чания взаимодействия блока прямого доступа в память и с вторым установочным входом регистра состояния, третий установочный вход которого соединен с третьим выходом блока управления приемопередачей, четвер- тый выход которого соединен с синхровходом регистра приема и с первым информационным входом регистра запроса магистрали, второй информационный вход которого соединен с пятым выходом блока управления приемопередачей, шестой и седьмой выходы которого соединены соответственно с входом сдвига и с информационным входом второго регистра сдвига, информационный выход которого соединен с информационным входом ре- гистра приема, информационные выходы которого соединены с информационными входами шинных формирователей данных, вторые управляющие входы которых соединены с вторыми управляющими входами шинных формирователей адреса и сразрешаю- . щим выходом блока прямого доступа в память адресные выходы которого соединены с информационными входами шинных формирователей адреса, первые информационные выходы которых соединены с информационными входами дешифратора порта, выход которого соединен с разрешающим входом дешифратора, третий выход которого соединен с разрешающим входом блока прямого

доступа в память, адресные входы которого соединены с информационными входами дешифратора и с вторыми информационными выходами шинных формирователей адреса, стробирующий выход, первый и второй входы запроса магистрали блока прямого доступа в память соединены соответственно с вторым синхровходом регистра передачи, с первым и вторым выходами регистра запроса магистрали.

2. Устройство по п. 1,отличающее- с я тем, что блок управления приемопередачей содержит кодер-декодер, одновибра- тор, два триггера, шесть элементов И, четыре элемента НЕ, элемент ИЛИ-НЕ, элемент И-ИЛИ. элемент И-ИЛИ-НЕ, причем группа информационных входов и выходов кодера-декодера образует соответственно группы информационных входов и выходов блока, информационные вход и выход кодера-декодера являются соответственно информационными входом и выходом блока, первый вход элемента И-ИЛИ и первый синхровход кодера-декодера являются соответственно первым и вторым синхров- ходами блока, второй синхровход кодера- декодера соединен с первым входом первого элемента И и является третьим синхровходом блока, второй вход элемента И- ИЛИ является первым входом логического условия блока, третий вход элемента И- ИЛИ соединен с входом первого элемента НЕ, с первым входом второго элемента И и является вторым входом логического условия блока, первый вход элемента ИЛИ-НЕ является третьим входом логического условия блока, выход первого элемента И соединен с синхровходом первого триггера, с вторым входом второго элемента И и является первым выходом блока, выходы третьего и четвертого элементов И являются соответственно вторым и третьим выходами блока, выход одновибратора соединен с первым входом четвертого элемента И и является четвертым входом блока, выход второго элемента И соединен с первым входом элемента И-ИЛИ-НЕ и является пятым выходом блока, выход пятого элемента И является шестым выходом блока, при этом в блоке управления приемопередачей второй вход четвертого элемента И соединен с выходом второго элемента НЕ, вход которого соединен с выходом признака контроля кодера- декодера, выход признака данных которого соединен с входом запуска одновибратора и с первым входом пятого элемента И, второй вход которого соединен с выходом синхронизации приема кодера-декодера, выход синхронизации передачи которого соединен с первым входом третьего элемента И,

второй вход которого соединен с выходом запроса кодера-декодера, с четвертым входом элемента И-ИЛИ и с входом третьего элемента НЕ, выход которого соединен с первым входом шестого элемента И, выход которого соединен с вторым входом элемента ИЛИ-НЕ, выход которого соединен с нулевым входом первого триггера, нулевой выход которого соединен с входом четвертого элемента НЕ. выход которого соединен с вторым входом элемента И-ИЛИ-НЕ, выход которого соединен с нулевым входом

второго триггера, синхровход и единичный выход которого соединены соответственно с выводом элемента И-ИЛИ и с вторым входом первого элемента И, выход первого элемента НЕ соединен с третьим входом элемента И-ИЛИ-НЕ и с вторым входом шестого элемента И, единичный выход первого триггера соединен с входом запуска кодера-декодера, первый и второй информационные входы первого и второго триггеров подключены соответственно к шинам единичного и нулевого потенциалов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1684799A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Электронная вычислительная машина с прямым доступом в память | 1990 |

|

SU1751776A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| Устройство для сопряжения процессора с устройствами ввода-вывода | 1987 |

|

SU1456964A1 |

| Устройство для обмена информацией между ЦВМ и внешними устройствами | 1989 |

|

SU1689961A1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

Изобретение относится к вычислительной технике и цифровой автоматике и может быть использовано в системах передачи данных для адаптации периферийного интерфейса связи с двунаправленным параллельным интерфейсом. Целью изобретения является повышение быстродействия. Устройство содержит блок управления приемо- передачей, блок прямого доступа в память, шинные формирователи данных, шинные формирователи адреса, регистр передачи, регистр приема, два регистра сдвига, регистр запроса магистрали, регистр состояния, дешифратор порта, дешифратор, генератор импульсов, триггер управления. 4 ил.

(pusi

фигА

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Устройство для обмена данными между параллельным и последовательным интерфейсами | 1985 |

|

SU1295403A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-15—Публикация

1988-10-24—Подача