Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах обработки и подготовки данных, для согласования интерфейсов устройств ввода-вывода и процессора, имеющих различный набор сигналов и протокол обмена информацией.

Цель изобретения - расширение класса сопрягаемых устройств за счёт увеличения длины формируемых последовательностей управляющих сигналов М повышение помехозащищенности при работе в режиме опроса.

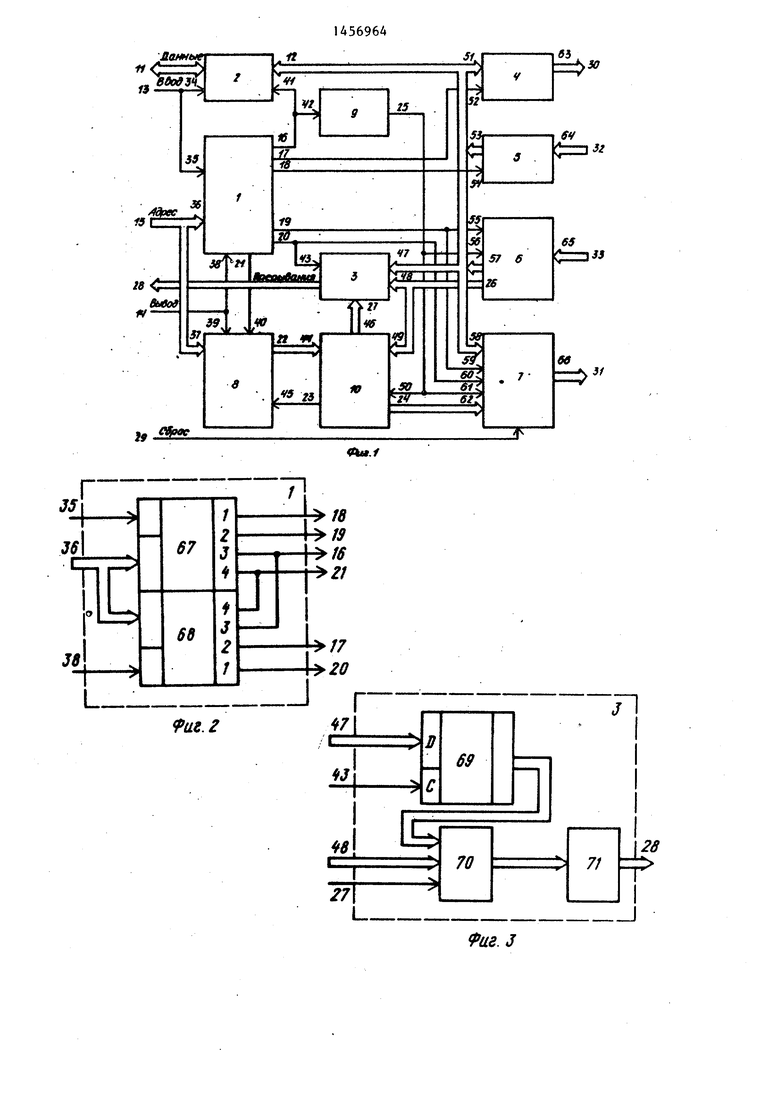

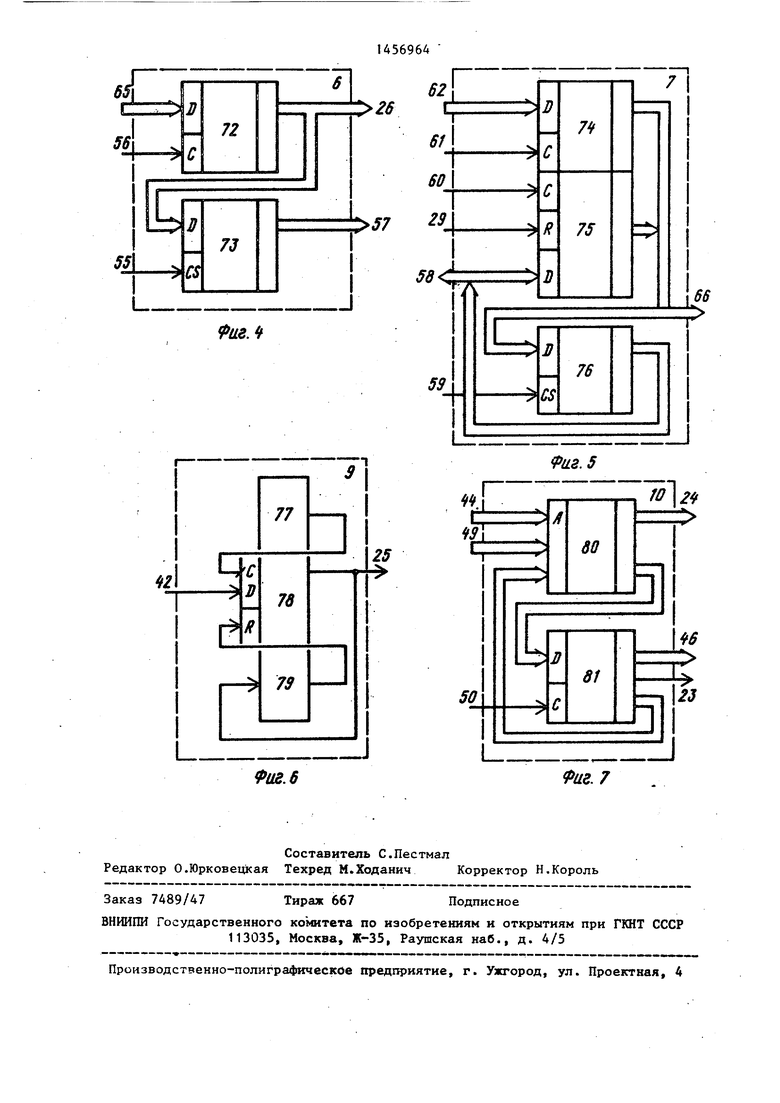

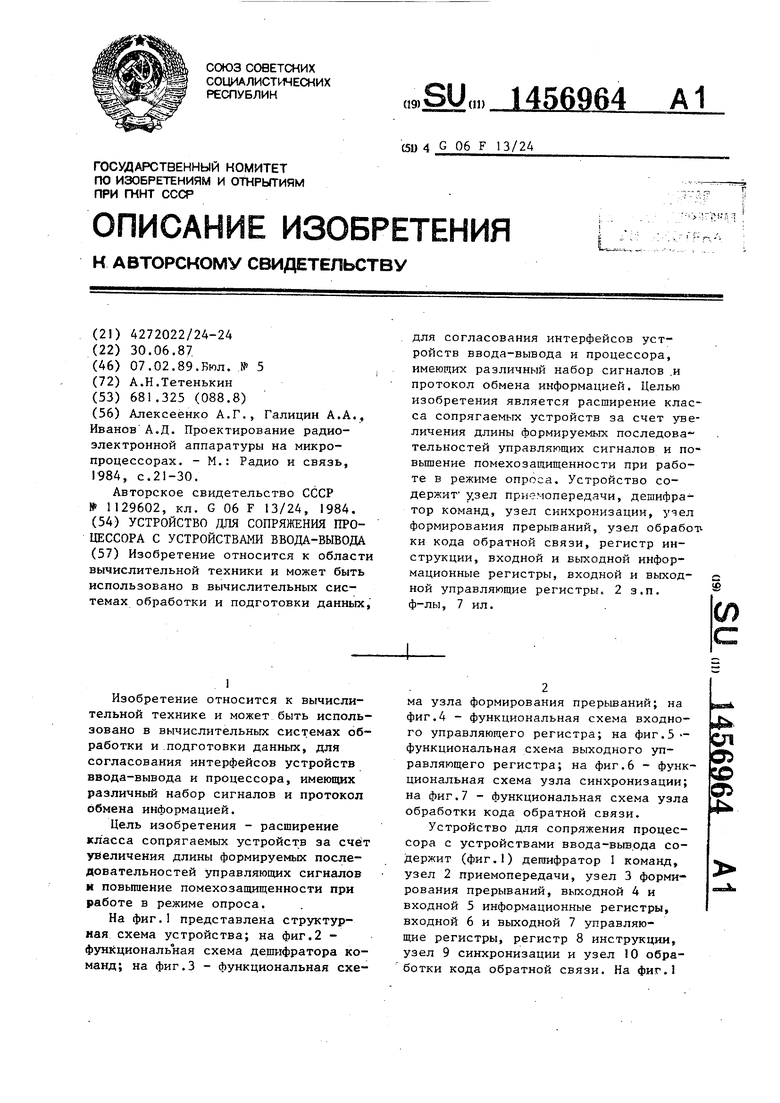

На фиг.1 представлена структурная схема устройства; на фиг.2 - функциональная схема дещифратора команд; на фиг.З - функциональная схема узла формирования прерьшаний; на фиг.4 - функциональная схема входного управляющего регистра; на фиг.5 - функциональная схема выходного управляющего регистра; на фиг.6 - функциональная схема узла синхронизации; на фиг.7 - функциональная схема узла обработки кода обратной связи.

Устройство для сопряжения процессора с устройствами ввода-вывода содержит (фиг.1) дешифратор I команд, узел 2 приемопередачи, узел 3 формирования прерываний, выходной 4 и входной 5 информационные регистры, входной 6 и выходной 7 управляющие регистры, регистр 8 инструкции, узел 9 синхронизации и узел 10 обработки кода обратной связи. На фиг.1

.

сд

О)

с&

обозначены также двунаправленная пгана 11 данных интерфейса процессора, внутренняя двунаправленная шина 12 данных устройства, входы и выходы 13-66 устройства и его узлов.

Дешифратор 1 команд предназначен для идентификации адресов портов ввода и портов вьшода устройства в командах процессора и формирования соответствующих управляющих сигналов для внутренних узлов устройства. Де i шифратор i содержит (фиг.2) постоянную память 67 дешифрации адресов пор-- тов ввода и постоянную память 68 дешифрации адресов портов вывода.

Узел 2 приемопередачи предназначен для согласования двунаправленной шины 11 данных интерфейса процессора с внутренней двунаправленной шиной 12 данных- устройства. Узел 2 состоит из двунаправленных шинных формирователей (ШФ), выбор которьк определяется сигналом на входе А1 узла, формируемым при 14аждом обращении процессора к портам устройства, а направление передачи зависит от уровня сигнала на входе Ввод 13 интерфейса процессора.

Узел 3 формирования прерываний предназначен для: маскирования ных запросов прерывания, поступающих по входам 48 и 27 и коммутации их их на выход 28 прерываний для интерфейса процессора. Узел 3 (фиг.З) содержит регистр 69 маски, группу элементов И 70 и группу элементов ИЛИ 71

Выходной информационный регистр 4 предназначен для фиксации информации, передаваемой по внутренней шине 12 данньк, и трансляции ее на выход 30 в интерфейс устройства вво- да-вьгоода.

Входной информационный регистр 5 предназначен для фиксации информации, поступающей с входа 32 из интерфейса устройства ввода-вывода, и трансляции ее на внутреннюю шину 1 данных устройства при наличии сигнала чтения на входе 54. Регистр 5 представляет собой регистр, имеющий выходы с тремя состояниями. При отсутствии сигнала чтения на входе 54 информация с входа 32 постоянно заносится в регистр 5, но не трансли- руется в шину 12 устройства. При появлении сигнала чтения на входе 54 занесение информации в регистр 5

145

i --нх 1

,

10

4569644

прекращается и она транслируется в - шину 12.

Входной управляющий регистр 6 предназначен для фиксации управляющих сигналов, поступающих от устройства ввода-вьшода по входу 33, и трансляции их в шину 12 данных устройства при при наличии сигнала считывания на вхо- входе 55; на выход 26 кода обратной связи узла. Регистр 6 содержит (фиг.4) триггер 72 и шинный формирователь 73.

Выходной управляющий регистр 7 15 предназначен для фиксации информации, постзтанмцей по шине 12 данных и группе входов 62f к трансляции ее на выход 31 в интерфейс устройства ввода- вывода при наличии сигнала считыва- 20 ния на входе 59. Регистр 7 содержит (фиг.5) триггеры 74 и 75 и шинный формирователь 76.

Регистр 8 инструкции предназначен для фиксации комбинации сигналов на- 25 входах 37 и 39 из интерфейса процессора в виде кода инструкции, определяющей выбор формируемой последовательности управляющих сигналов.

Узел 9 синхронизации предназначен 30 для организации работы регистров 6 и 7 и узла 10 в процессе формирования последовательностей управляющих сигналов обратной связи, а также для блокирования сигналов синхронизации при обращении процессора к портам ввода и вьшода устройства. Узел 9 содержит (фиг.6) генератор 77 импульсов, триггер 78 и элемент 79 задержки .

Узел 10 обработки кода обратной связи предназначен для формирования последовательностей выходных управляющих сигналов обратной связи на выходе 24, сигналов запросов прерьша- 45 3 выходе 46 и сигнала установки в исходное состояние регистра инструкция на выходе 23 в зависимости от кода инструкции на входе 44 и последовательностей входных управляющих сигналов обратной связи на входе 49. Узел 10 содержит (фиг.7) постоянную память 80 и регистр 81.

Устройство работает следующим образом.

Устройство приводится в исходное состояние сигналом Сброс интерфейса процессора, поступающим на вход Сброс 29 устройства и устанавливающим в исходное состояние триггер

35

40

50

55

75 регистра 7, при этом на выход 31 формируется сигнал начальной установки устройства ввода-вывода, которое в ответ прекращает формирование управляющих сигналов на вход 33, транслируемых через группу выходов 26 регистра 6 на вход кода обратной связи узла 10, который, в свою очередь, прекращает формирование управляющих сигналов на групле выходов 24 и одновременно формирует на выходе 23 импульс установки в исходное состояние регистра 8.

При адресации со стороны процессора устройства представляет собой ряд независимо адресуемых портов ввода и портов вывода. В командах вывода информации в порт устройства информация с щины 11 данных интерфейса процессора транслируется через узел 2 в шину 12 данных и записьшается либо в регистр 4, либо одновременно в регистр 69 узла 3 и триггер 75.регистра 7. В командах ввода информации из порта устройства информация либо с выходов регистра 5, либо одновременно с выходов шинного формирователя 73 регистра 6 и шинного формирователя 76 регистра 7 поступает на на шину 12 данных и через узел 2 транслируется в шину 1 данных интерфейса .процессора.

Перед началом обмена информацией в зависимости от подключаемого устройства ввода-вывода процессор настраивает узел 3 и регистр 7, осуществляя ввод информации в порт настройки, при этом в триггер 75 регистра 7 записывается неизменяемая в процессе обмена комбинация управляющих сигналов на выходе 31 интерфейса устройства ввода-вывода, а в регистр 69 маски узла 3 записывается код, управляющий выбором в качестве сигналов прерывания, поступающих на выход 28 в интерфейс процессора, управляющих сигналов на входе 33 из интерфейса устройства ввода-вывода, транслируемых через регистр 6, и сигналов запросов прерываний с выхода 46 узла 10, формируемых в процессе обмена информацией. По сравнению с известным процесс начальной настройки предлагаемого устройства значительно сокращается или может быть исключен вообще (в зависимости от интерфейса устройства ввода-вывода), так как информация о формируемых в процессе обме10

15

20

25

569646

на управляющих сигналах хранится в постоянной памяти .80 узла 10.

При реализации вывода слова инфор- мап.ии в устройство ввода-вывода процессор осуществляют вывод слова информации в порт вывода устройства, при этом информация заносится в регистр 4 и транслируется на выход 30 в устройство ввода-вывода, а адрес порта на входе 15 адреса и логическое значение сигнала на входе Вывод 14 из интерфейса процессора записываются в регистр 8 в качестве кода инструкции, который через выход 22 поступает на соответствующую группу входов узла 10, на выходе 24 которого формируется комбинация (последовательность комбинаций) управляющих сигналов, транслируемых через триггер 74 регистра 7 на выход 31 в интерфейс устройства ввода-вьшода. Формирование последовательности комбинаций управляющих сигналов обеспечивается наличием в узле 10 регистра 81. Устройство ввода-вывода, получив необходимые управляющие сигналы на выходе 31, вводит информацию с выхода 30 и формирует на входе 33 управляющие сигналы подтвержения ввода, которые через выход 26 регистра 6 транслируются на вход кода обратной связи узла 10 и вызывают формирование ответной комбинации (последовательности комбинаций) на выходе 24 узла 10 и, соответственно, на выходе 31 в интерфейс устройства ввода-вьшода.- Одновременно на выходах 23 и 46 узла 10 формируются импульс установки регистра 8 в исходное состояние и сигнал запроса на прерьгоание, сигнализирующий процессору о завер- щении вывода слова информации в устройство ввода-вьшода. Процессор,либо получив сигнал прерьшания на выходе 28 прерываний устройства (режим работы по прерьшаниям), либо путем опроса порта состояния устройства (режим опроса),считывает содержимое триггера 72 регистра 6 и триггеров 74 и 75 регистра 7.

При реализации ввода слова инфор мации из устройства ввода-вывода посг леднее формирует на входе 32 слово gg информации, а на входе 33 - комбинацию управляющих сигналов, которая через выход 26 регистра 6 транслируется на входы узлов 10 и 3. При этом , на выходе узла 3 в интерфейс процес30

35

40

45

50

сора формируется сигнал прерьюания, а на выходе 24 узла 10 - комбинация управляющих сигналов, транслируемая через регистр 7 на выход 31 в интерфейс устройства ввода выэода, которая сообщает устройству ввода-вьгоода о занятии устройства. Процессор, получив сигнал прерывания (режим рабоФормула изобретения

1. Устройство для сопряжения процессора с устройствами ввода-вьгоода, i содержащее дешифратор команд, узел приемопередачи, узел формирования прерьшаний, узел обработки кода обратной связи, выходной и входной ИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1987 |

|

SU1425685A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1984 |

|

SU1180911A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Устройство прерывания | 1982 |

|

SU1084795A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1982 |

|

SU1132282A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах обработки и подготовки данных. для согласования интерфейсов устройств ввода-вывода и процессора, имеющих различный набор сигналов .и протокол обмена информацией. Целью изобретения является расширение класса сопрягаемых устройств за счет увеличения длины формируемых последова-- тельностей управляющих сигналов и по- вьппение помехозащищенности при работе в режиме опроса. Устройство содержит у.зел при- мопередачи, дешифратор команд, узел синхронизации, учел формирования прерываний, узел обработки кода обратной связи, регистр инструкции, входной и выходной информационные регистры, входной и выходной управляющие регистры. 2 з.п. ф-лы, 7 ил. Р.

тй по прерьшаниям), либо опросив порт ю Формационные регистры, выходной и

состояния устройства (режим работы по опросу), осуществляет обращение . к порту Бзода устройства, при этом информация на входе 32 фиксируется в регистре 5 и транслируется в ганку 11 данных процессора. Одновременно адрес порта на входе 15 адреса.и логическое значение сигнала на вхрде Вывод 14 интерфейса процессору фиксируются в регистре 8 в качестве кода инструкции. При этом с выхода 24 узла 10 через выход 3 в интерфейсе устройства ввода-вывода формируется комбинация управляющих сигналов (последовательность комбинаций), сообщающая устройству ввода-вывода о вводе процессором слова информации. По окончании ввода информации на выходе 23 узла 10 формируется импульс установки регистра 8 в исходное состояние.

Обращение со стороны процессора к порту настройки и порту состояния устройства не приводит к изменению состояния регистра 8 и не влияет на работу узла 10 в процессе ввода шш вывода информации. В процессе обращения процессора к портам устройства узлом 9 осуществляется блокирование синхронизирующего сигнала на выходе 25, при этом состояние регистров 6 и 7 и узла 10 не нэменяется, если даже обращение происходит в процессе формирования последовательности управляющих сигналов, что позволяет избежать искажения информации, передаваемой между процессором, устройством и устройством ввода-вывода.

Если в процессе обмена информахщ- ей происходит нарущение формируемой последовательности управляющих сигналов или устройство ввода-вьшода формирует комбинацию управляющих сигналов окончания обмена на выходе 28 узла 3 в интерфейс процессора формируется сигнал прерывания с другим уровнем приоритетности, чем сигналы прерьшайия, формируемые в процессе нормальной работы устройства.

15

20

входной управляющие регистры, причем группа информационных входов-в ходов узла приемопередачи образует группу входов-выходов устройства для подключения к группе информаци ных входов-выходов процессора, пер вый, второй разрещающие входы и гр па информационных входов дешифрато команд образуют входы устройства д подключения соответственно к выход Bвoд, Вьшод и группе выходов а реса процессора, группа выходов уз формирования прерываний образует г пу выходов, устройства для подключе

25 ния к группе входов прерывания про цессора, группы информационных вых дов выходного информационного реги ра и информационных входов входног информатхионного регистра образуют,

30 группы выходов и входов устройства для подключения соответственно к . группам информационных входов и вы дов устройств ввода-вывода, группы информационных выходов выходного управляющего регистра и информационных входов входного управляющего регистра образуют группы выходов и входов устройства,для подключения ответственно к группам управляющих

Q входов и выходов устройства ввода- вывода, при этом вторая группа информационных входов-выходов узла п емопередачи соединена с группой ин формационных входов выходного инфо

45 мационного регистра, с группой инф мационных выходов входного информа ционного регистра, с первой группо информационных выходов входного уп равляющего регистра, с первой гру пой информационных входов узла фор мирования прерьшаний, с группой информационных входов-выходов выхо ного управляющего регистра, группа информационных входов которого сое

gg динена с первой группой информацио ных выходов узла обработки кода об ратной связи, вторая группа информ ционных выходов которого соединена второй группой информационных вход

35

50

входной управляющие регистры, причем группа информационных входов-выходов узла приемопередачи образует группу входов-выходов устройства для подключения к группе информационных входов-выходов процессора, первый, второй разрещающие входы и группа информационных входов дешифратора команд образуют входы устройства для подключения соответственно к выходам Bвoд, Вьшод и группе выходов адреса процессора, группа выходов узла формирования прерываний образует груп-; пу выходов, устройства для подключения к группе входов прерывания процессора, группы информационных выходов выходного информационного регистра и информационных входов входного информатхионного регистра образуют,

группы выходов и входов устройства для подключения соответственно к . группам информационных входов и выходов устройств ввода-вывода, группы информационных выходов выходного управляющего регистра и информационных входов входного управляющего регистра образуют группы выходов и входов устройства,для подключения со ответственно к группам управляющих

входов и выходов устройства ввода- вывода, при этом вторая группа информационных входов-выходов узла приемопередачи соединена с группой информационных входов выходного информационного регистра, с группой информационных выходов входного информационного регистра, с первой группой информационных выходов входного управляющего регистра, с первой группой информационных входов узла формирования прерьшаний, с группой информационных входов-выходов выходного управляющего регистра, группа информационных входов которого соединена с первой группой информационных выходов узла обработки кода обратной связи, вторая группа информационных выходов которого соединена с второй группой информационных входов

узла формирования прерьшаний, первая группа информационных входов узла обработки кода обратной связи соеди- нена с второй группой информационных выходов входного управляющего регистра, первый вьпсод дешифратора команд соединен с входом записи выходного информационного регистра, вто- рой выход дешифратора команд соединен с входами записи узла формирования прерываний и выходного управляющего регистра, отличающее- с я тем, что, с целью расширения класса сопрягаемых устройств за счет увеличения длины формируемых последовательностей управляющих сигналов и повышения помехозащищенности при работе в режиме опроса, в него введены узел синхронизации и регистр инструкции, причем информационный вход и группа информационных входов регистра инструкции соединены соответственно с вторым разрешающим входом и группой информационных входов дешифратора команд, вход направления передачи узла приемопередачи соединен с первым разрешающим входом дешифратора команд, установочный вход выходного управляющего регистра является входом устройства .для подключения к выходу Сброс процессора, при этом третья группа информационных входов узла формирования прерываний соединена с второй группой информационных выходов входного угравляющего регистра, группа информационных выходов регистра инструкции соединена с второй группой информационных входов узла обработки кода обратной связи, установочный выход которого соединен с установочным входом регистра инструкции, вход записи которого соединен с третьим выходом дешифратора команд, четвертый выход которого соединен с входом чтения входного информационного регистра, пятый, выход дешифратора команд соединен с входами чтения входного и выходного управляющих регистров, шестой выход дешифратора команд

соединен с разрешающим входом узла приемопередачи и с входом запуска узла синхронизации синхровыход которого соединен с синхровходами узла обработки кода обратной связи входного и выходного управляющих регистров.

2, Устройство по П.1, о тли- чающееся тем, что узел обработки кода обратной связи содержит постоянную память и регистр, причем первая и вторая группы адресных входов постоянной памяти образуют соответственно, первую и вторую группы информационных входов узла, первая rpynrffe информационных выходов постоянной памяти и первая группа информационных выходов регистра образуют соответственно первую и вторую группы информационных выходов узла, синхровход и информационный выход регистра являются соответственно синхровходом и ус ановочньм выходом узла, при этом в узле обработки кода обратной связи вторая группа информационных выходов регистра соединена с третьей группой адресных входов Постоянной памяти, вторая группа информационных выходов которой соединена с группой информационных входов регистра.

гистр маски, группу элементов И, группу элементов ИЛИ, причем группа информационных входов регистра маски образует первую группу информационных входов узла, первые и вторые входы элементов И группы образуют соответственно вторую и третью группы информационных входов узла, синхровход регистра маски является входом записи узла, выходы элементов ИЛИ группы образуют группу выходов узла, при этом в узле формнрова-. кия прерываний группа выходов регист- . ра маскн соединена с третьими входами элементов И группы, выходы которых соединены с входами элементов ИЛИ группы.

UOfiMbt

fas. J

| Алексеенко А.Г., Галицин А.А., Иванов А,Д | |||

| Проектирование радиоэлектронной аппаратуры на микропроцессорах | |||

| - М.: Радио и связь, 1984, с.21-30 | |||

| Устройство для сопряжения процессора с устройствами ввода-вывода | 1983 |

|

SU1129602A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-07—Публикация

1987-06-30—Подача