Изобретение относится к вычислительной технике, в частности к устройствам сопряжения ЭВМ с абонентом, и может быть использовано в качестве устройства буферной памяти.

Целью изобретения является сокращение аппаратурных затрат.

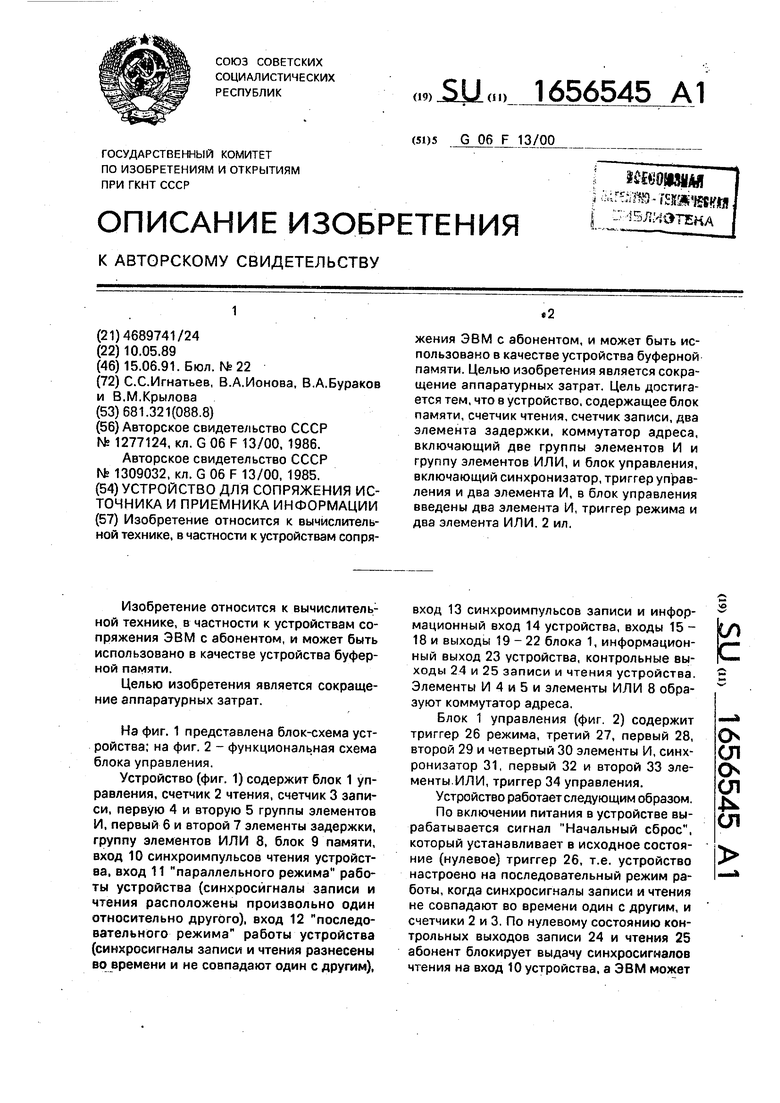

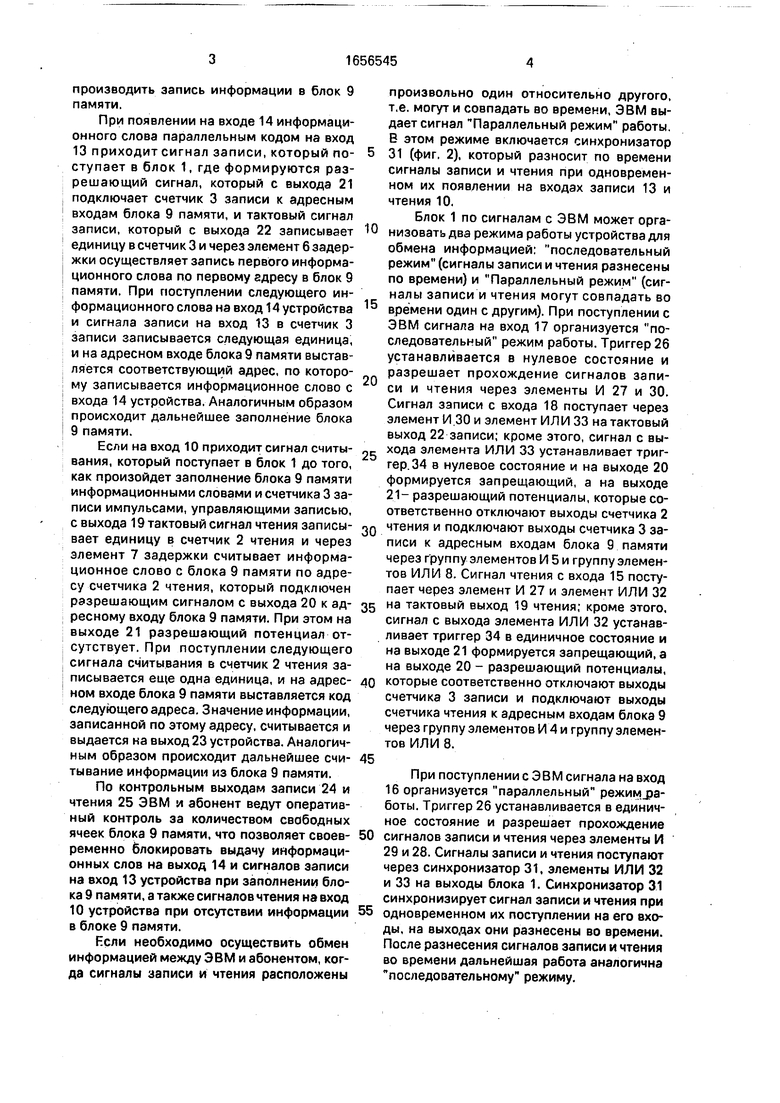

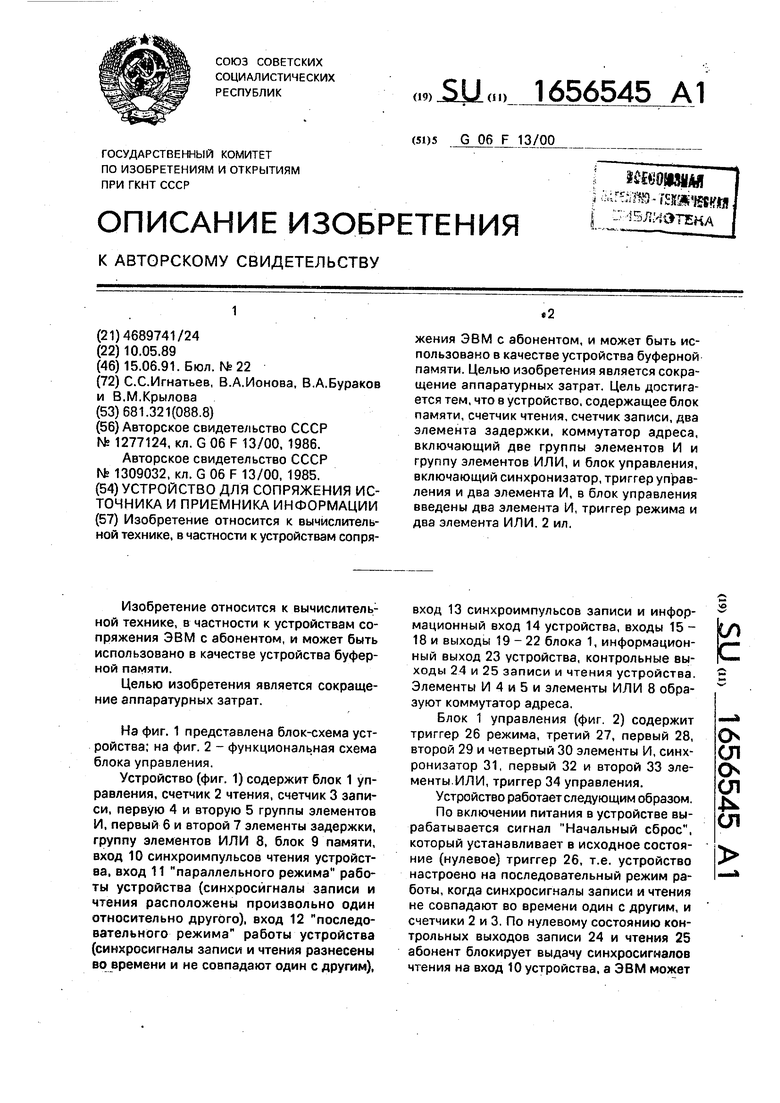

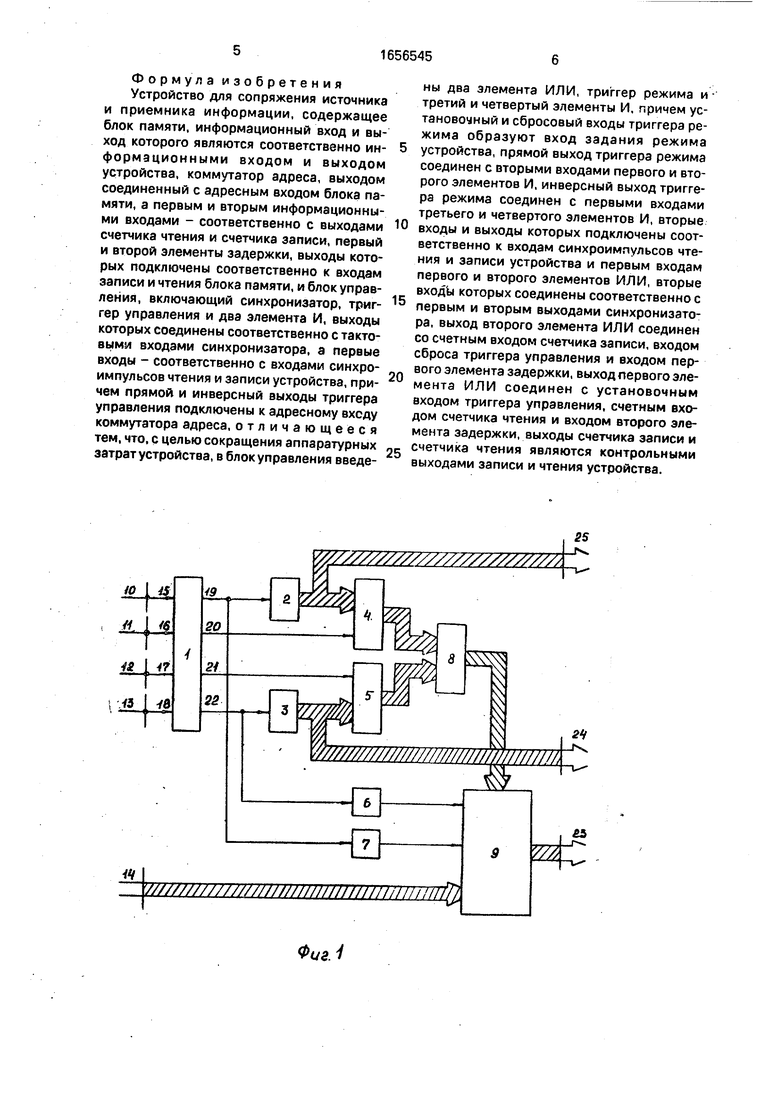

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - функциональная схема блока управления.

Устройство (фиг. 1) содержит блок 1 управления, счетчик 2 чтения, счетчик 3 записи, первую 4 и вторую 5 группы элементов И, первый 6 и второй 7 элементы задержки, группу элементов ИЛИ 8, блок 9 памяти, вход 10 синхроимпульсов чтения устройства, вход 11 параллельного режима работы устройства (синхросигналы записи и чтения расположены произвольно один относительно другого), вход 12 последовательного режима работы устройства (синхросигналы записи и чтения разнесены во времени и не совпадают один с другим).

вход 13 синхроимпульсов записи и информационный вход 14 устройства, входы 15 - 18 и выходы 19-22 блока 1, информационный выход 23 устройства, контрольные выходы 24 и 25 записи и чтения устройства. Элементы И 4 и 5 и элементы ИЛИ 8 образуют коммутатор адреса.

Блок 1 управления (фиг. 2) содержит триггер 26 режима, третий 27, первый 28, второй 29 и четвертый 30 элементы И, синхронизатор 31, первый 32 и второй 33 элементы ИЛИ, триггер 34 управления.

Устройство работает следующим образом.

По включении питания в устройстве вырабатывается сигнал Начальный сброс, который устанавливает в исходное состояние (нулевое) триггер 26, т.е. устройство настроено на последовательный режим работы, когда синхросигналы записи и чтения не совпадают во времени один с другим, и счетчики 2 и 3. По нулевому состоянию контрольных выходов записи 24 и чтения 25 абонент блокирует выдачу синхросигналов чтения на вход 10 устройства, а ЭВМ может

СО

с

о ел о ел ел

производить запись информации в блок 9 памяти.

При появлении на входе 14 информационного слова параллельным кодом на вход 13 приходит сигнал записи, который поступает в блок 1, где формируются разрешающий сигнал, который с выхода 21 подключает счетчик 3 записи к адресным входам блока 9 памяти, и тактовый сигнал записи, который с выхода 22 записывает единицу в счетчик 3 и через элемент 6 задержки осуществляет запись первого информационного слова по первому адресу в блок 9 памяти. При поступлении следующего информационного слова на вход 14 устройства и сигнала записи на вход 13 в счетчик 3 записи записывается следующая единица, и на адресном входе блока 9 памяти выставляется соответствующий адрес, по которому записывается информационное слово с входа 14 устройства. Аналогичным образом происходит дальнейшее заполнение блока

9памяти.

Если на вход 10 приходит сигнал считывания, который поступает в блок 1 до того, как произойдет заполнение блока 9 памяти информационными словами и счетчика 3 записи импульсами, управляющими записью, с выхода 19 тактовый сигнал чтения записывает единицу в счетчик 2 чтения и через элемент 7 задержки считывает информационное слово с блока 9 памяти по адресу счетчика 2 чтения, который подключен разрешающим сигналом с выхода 20 к адресному входу блока 9 памяти. При этом на выходе 21 разрешающий потенциал отсутствует. При поступлении следующего сигнала считывания в счетчик 2 чтения записывается еще одна единица, и на адресном входе блока 9 памяти выставляется код следующего адреса. Значение информации, записанной по этому адресу, считывается и выдается на выход 23 устройства. Аналогичным образом происходит дальнейшее считывание информации из блока 9 памяти.

По контрольным выходам записи 24 и чтения 25 ЭВМ и абонент ведут оперативный контроль за количеством свободных ячеек блока 9 памяти, что позволяет своевременно блокировать выдачу информационных слов на выход 14 и сигналов записи на вход 13 устройства при заполнении блока 9 памяти, а также сигналов чтения на вход

10устройства при отсутствии информации в блоке 9 памяти.

Ясли необходимо осуществить обмен информацией между ЭВМ и абонентом, когда сигналы записи и чтения расположены

0

5

0

5

0

5

0

5

0

5

произвольно один относительно другого, т.е. могут и совпадать во времени, ЭВМ выдает сигнал Параллельный режим работы. В этом режиме включается синхронизатор 31 (фиг. 2), который разносит по времени сигналы записи и чтения при одновременном их появлении на входах записи 13 и чтения 10.

Блок 1 по сигналам с ЭВМ может организовать два режима работы устройства для обмена информацией: последовательный режим (сигналы записи и чтения разнесены по времени) и Параллельный режим (сигналы записи и чтения могут совпадать во времени один с другим). При поступлении с ЭВМ сигнала на вход 17 организуется последовательный режим работы. Триггер 26 устанавливается в нулевое состояние и разрешает прохождение сигналов записи и чтения через элементы И 27 и 30. Сигнал записи с входа 18 поступает через элемент И 30 и элемент ИЛИ 33 на тактовый выход 22 записи; кроме этого, сигнал с выхода элемента ИЛИ 33 устанавливает триггер. 34 в нулевое состояние и на выходе 20 формируется запрещающий, а на выходе 21- разрешающий потенциалы, которые соответственно отключают выходы счетчика 2 чтения и подключают выходы счетчика 3 записи к адресным входам блока 9 памяти через группу элементов И 5 и группу элементов ИЛИ 8. Сигнал чтения с входа 15 поступает через элемент И 27 и элемент ИЛИ 32 на тактовый выход 19 чтения; кроме этого, сигнал с выхода элемента ИЛИ 32 устанавливает триггер 34 в единичное состояние и на выходе 21 формируется запрещающий, а на выходе 20 - разрешающий потенциалы, которые соответственно отключают выходы счетчика 3 записи и подключают выходы счетчика чтения к адресным входам блока 9 через группу элементов И 4 и группу элементов ИЛИ 8.

При поступлении с ЭВМ сигнала на вход 16 организуется параллельный режим боты. Триггер 26 устанавливается в единичное состояние и разрешает прохождение сигналов записи и чтения через элементы И 29 и 28. Сигналы записи и чтения поступают через синхронизатор 31, элементы ИЛИ 32 и 33 на выходы блока 1. Синхронизатор 31 синхронизирует сигнал записи и чтения при одновременном их поступлении на его входы, на выходах они разнесены во времени. После разнесения сигналов записи и чтения во времени дальнейшая работа аналогична последовательному режиму.

Формула изобретения Устройство для сопряжения источника и приемника информации, содержащее блок памяти, информационный вход и выход которого являются соответственно информационными входом и выходом устройства, коммутатор адреса, выходом соединенный с адресным входом блока памяти, а первым и вторым информационными входами - соответственно с выходами счетчика чтения и счетчика записи, первый и второй элементы задержки, выходы которых подключены соответственно к входам записи и чтения блока памяти, и блок управления, включающий синхронизатор, триггер управления и два элемента И, выходы которых соединены соответственно с тактовыми входами синхронизатора, а первые входы - соответственно с входами синхроимпульсов чтения и записи устройства, причем прямой и инверсный выходы триггера управления подключены к адресному входу коммутатора адреса, отличающееся тем, что, с целью сокращения аппаратурных затрат устройства, в блок управления введе0

5

0

5

ны два элемента ИЛИ, триггер режима и третий и четвертый элементы И, причем установочный и сбросовый входы триггера режима образуют вход задания режима устройства, прямой выход триггера режима соединен с вторыми входами первого и второго элементов И, инверсный выход триггера режима соединен с первыми входами третьего и четвертого элементов И, вторые входы и выходы которых подключены соответственно к входам синхроимпульсов чтения и записи устройства и первым входам первого и второго элементов ИЛИ, вторые входы которых соединены соответственно с первым и вторым выходами синхронизатора, выход второго элемента ИЛИ соединен со счетным входом счетчика записи, входом сброса триггера управления и входом первого элемента задержки, выход первого элемента ИЛИ соединен с установочным входом триггера управления, счетным входом счетчика чтения и входом второго элемента задержки, выходы счетчика записи и счетчика чтения являются контрольными выходами записи и чтения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронно-вычислительной машины с абонентом | 1985 |

|

SU1277124A1 |

| Устройство для обмена информацией между абонентом и ЭВМ | 1986 |

|

SU1314346A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1278869A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1989 |

|

SU1615729A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1302289A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1236491A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1437871A1 |

Изобретение относится к вычислительной технике, в частности к устройствам сопря.2 жения ЭВМ с абонентом, и может быть использовано в качестве устройства буферной памяти. Целью изобретения является сокращение аппаратурных затрат. Цель достигается тем, что в устройство, содержащее блок памяти, счетчик чтения, счетчик записи, два элемента задержки, коммутатор адреса, включающий две группы элементов И и группу элементов ИЛИ, и блок управления, включающий синхронизатор, триггер управления и два элемента И, в блок управления введены два элемента И, триггер режима и два элемента ИЛИ. 2 ил.

Ю

ц Iу/шмш/мннш}Ш/1/1ин;1И1пШц

Фиг. 1

Л

27

46

88

У7

ев

18

30

Фие.2

32

/9

го

И

3

г/

33

ei

| Устройство для сопряжения электронно-вычислительной машины с абонентом | 1985 |

|

SU1277124A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1309032A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-15—Публикация

1989-05-10—Подача