1

Изобретение относится к щ)еобразовательной технике и может быть испопьзсьвано в устройствах для управления преобразователями натфяжения, а также во втс5 «чкых источниках питания электр и радиоаппаратуры..

Известны устройства для управления многофазными стабилизаторами, содержащне генератяр тактовых импульсов, делитель частоты, распределитель тактовыхимпульсов, измерительный орган с усилителем сигнала рассогласования и ш ротно-импульсные модуляторы по числу преобразовательных ячеек ll.

Недостатком известных устройств является невысокая надежность, обусловленная увеличением уровня пульсааий, нафяжения на выходе стабилизатора при отказе одной из ячеек.

Наиболее близким к хфедлагаемому является устройство для управления мвеогофазным импульсным регулятором, сондержащее широтно-импульсные мопулято ры по числу ячеек, выход каждого из оTqpbix подсоединен через соответствующую феобразовательную ячейку ко входу канального датчика работоспособности и входы соединены соответственно с выходом измерительного элемента, подсоединенного своим входом к Выходам щреобразовательных ячеек и с выходами О - триггеров расгфепелятеля импульсов, первые входы подсоединены через делитель частоты к выходу генератора

10 тактовых импульсов, и блок логики

Недостатком извествюго устройства является невысокая надежность, обусловленная ухудшением стабильности выходного нащ}яжения в случае отказа двух и более п;}еобразоватепьных ячеек.

Цель изо ютеняя - повышенве надежнсюти yctpoficTBa.

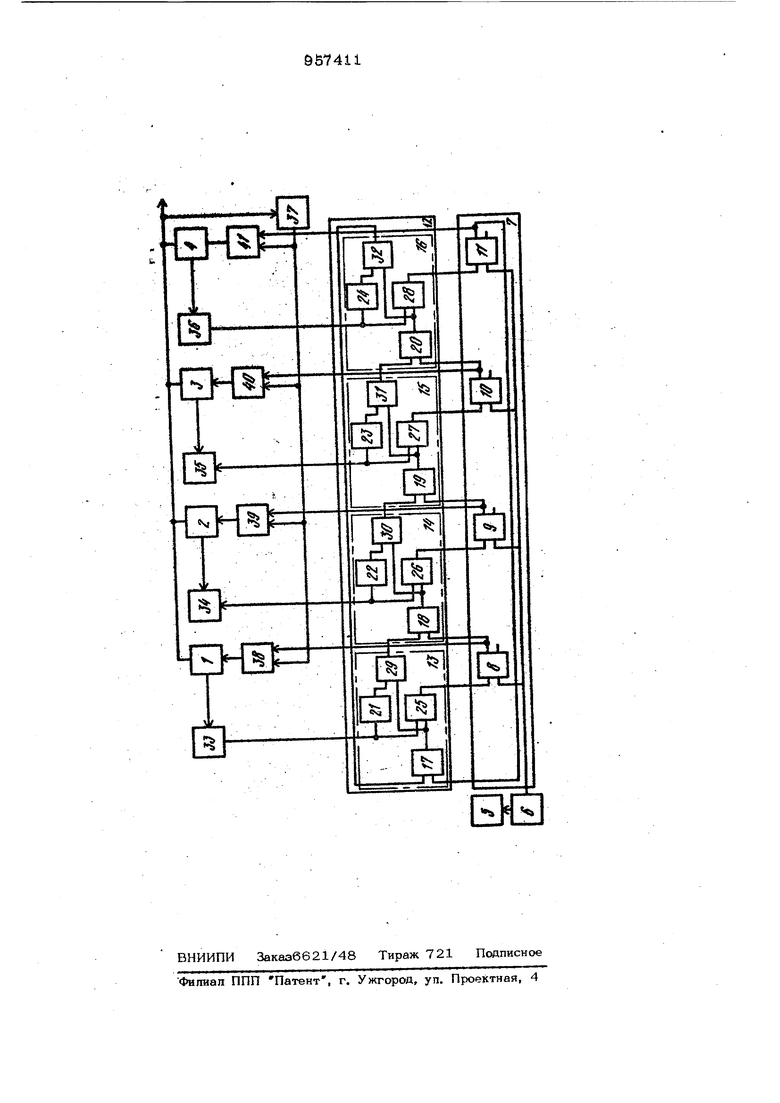

Поставленная цель дост«гается тем, что в устройстве блок логика выполвен ш основе ячеек переклк 1еш(я, каждая 8 которых содержит алемент ИЛИ, два элемеага И в эпемел НЕ, прячем вхоаы элемента ИЛИ поасоедиоевы соответстве но к выходу Второго элемента И преды дущей ячейки переключения и к выходу предыдущего D триггера, выход элемента ИЛИ соед1шен с первыми входами первого и второго элементов И соответствующей ячейки переключения, вторые входы первого и второго элементов И по соединены к выходу канального датчика работоспособности, причем вход первого элемента И непосредственно и второго элемента И через элемент НЕ, а выходы первого и второго элементов И соединены соответственно со вторым входом соответствующего D -триггера и первым входом элемента ИЛИ последующей ячей ки переключения. На чертеже приведена принципиальная электрическая схема устройства для упра вления многофазным импульсный регулятором. Устройство для управления стабилизатором из четырех преобразовательных ячеек 1-4 содержит генератор 5 тактовых импульсов, делитель 6 частоты, распределитель 7 тактовых импульсов с четырьмя выходами на основе кольцевой сдвигающей схемы, содержащей О триггеры 8-11, блок 12 логики, со-, держащий четьфе ячейки 13-16 пере ключения. Каждая ячейка переключения содержит элемент ИЛИ17 (18 - 20), элемент НЕ 21 (22 - 24) и два элемента И, первый 25 (26 - 28) и второй - 29 (30 - 32) соответственно. Устройство включает таклсе четьфе датчика 33 - 36 работоспособности, измерительный орган с усилителем 37 сиг нала рассогласования и четьфе щиротноимпульсных модулятора 38 - 41. Выход генератора 5 подключен через делитель 6 частоты ко входу распредели теля 7. Выходы распределителя подключены к широтно-импульсным модулятора соответствующих ячеек. Одновременно выход каждого /i -го триггера распределителя 7 подключен через один из входов элемента ИЛИ последующей ячей ки переключения к одному из входов первого и второго элементов И, другой вход каждого из которых подключен к выходу датчика работоспособности соответствующей ячейки, причем вход первого элемента И подключен непосредствен но, а второй - через элемент НЕ. Выхо первого элемента И соединен со входом 1риггера соответствующей ячейки, выхо второго элемента И соединен с другим ВХОДОМ элемента ИЛИ последующей ячейки переключения. Работа устройства рассматривается при режиме запуска и работы стабилизатора с исправными ячейками и режиме работы стабилизатора при отказе одной или нескольких преобразовательных ячейках. В режиме запуска устройство работает следующим образом. В исходном состоянии при исправных ячейках выходное напряжение датчиков работоспособности всех ячеек имеет уровень логической единицы, который сохраняется в течение всего времени исправной работы ячейки. Напряжение на входах первых элементов И 25 - 28, соединенных с выходами датчиков непосредственно, равно напряжению логической единицы, а. на входах вторых элементов И 29 - 32, соединенных с выходами датчиков через элементы НЕ, равно напряжению логического нуля. Один из триггеров распределителя 7, например триггер 11 ячейки 4, через установочный вход переводится в состояние единица, при этом напряжение с единичным уровнем поступает через элемент ИЛИ 17 ячейки 13 переключения на вход элементов И 25 и 29 через элемент И 25 на управляющий вход триггера 8. Первый тактовый импульс, поступивший на тактовые входы триггеров 8-11, переводит триггер 11 в нулевое, а триггер 8 в единичное состояние. На первом выходе распределителя 7 (выходе триггера 8) появляется импульс, поступающий на широтно-импульсный модулятор 38 ячейки 1. Одновременно напряжение с уровнем логической единицы поступает на вход триггера 9 второй ячейки через элемент ИЛИ 18 и элемент И 26 ячейки 14 переключения. Череа время Т/ п на тактовые входы триггеров распределителя 7 поступает второй импульс, который переводит в нулевое состояние триггер 8 и в единичное триггер 9. На втором выходе распределителя появляется импульс напряжения. Поступающий на щиротно-импульсный модулятор 39 второй ячейки. Одновременно появляется напряжение и на управляющем входе триггера 10, поступившее через элемент ИЛИ 19 и элемент И 27 ячейки 15 переключения. Третий тактовый импульс, поступающй. через время Т/ П после второго импульса переводит триггер 9 в нулевое, а триггер 10 в единичное состояние. На третьем в;

5. 9SV411 6

ходе распределителя 7 появляется переключешш на управляющий вход

рульс напряжения. Одновременно через эле- триггера 8. На входе триггера 11 отмент И 28 на вход триггера 11 поступа- казавшей ячейки со фаняется напряжеет напряжение с выхода триггера Ю.ние логического Нуля. Очередной тактоОчередной, четвертый, импульс перево дит триггер 1О в нулевое, а триггер 11 в единичное состояние. Импульс напряжения появляется на четвертом выходе распределителя 7 я на управляющем входе триггера 8, поступая через элемент ИЛИ 17 li элемент И 25. Далее весь цикл работы устройства пр исщзавных ячейках повторяется. В режиме отказа одной или нескольки преобразовательных ячеек устройство работает следующим образом. При- отказе одной из преобразовательных ячеек, например ячейки 2, датчик 3 работоспособности переводится в нулевое состояние. Напряжение на входе элемента И 26 равно напряжению логического нуля, а на входе элемента И 30 - на1фяжешсю логической единицы в течение всего времени работы стабилизатора с отказавшей ячейкой. Тогда напряжение с выхода триггера 8 поступает через элемент ИЛИ 18, элемент И ЗО.ячейки 14 переключения, элемент ИЛИ 19, элемент И 27 на управляющий вход триггера 10. На входе триггера 9 сохраняется нулевой уровень напряжения. Следовательно, очередной тактовый импульс переводит триггер 8 в нулевое состояние, а в единичное переводится триггер 10, На третьем выходе распределителя 7 появляется импульс напряжения, а затем при поступлении очередных тактовых импульсов - на четвертом и первому Далее цикл работы при отказе одной ячейки повторяется. Таким образом, при отка зе ячейки 2 соответствующий ей триггер 9 выводится из работы, а вместо не го подключается следующий по порядку триггер 10. Отказ еще одной ячейки, нагфимер ячейки 4, вызывает переход в нулевое состояние датчика 36. Напряжение на соединенном с датчиком входе элемента И 28 соответствует уровню логическ го нуля, а на соединенном с датчиком через элемент НЕ 24 входе элемента И 32 -. напряжению логической единицы в течение всего времени работы стабилизатора с отказавшей ячейкой 4. При этом нагфяжение с выхода триггера lO поступает через элемент ИЛИ 2О, элемент И 32 ячейки 16 переключения, элемент ИЛИ 17 и элемент И 25 ячейк вый импульс, следовательно, переводит в единичное состояние триггер 8 первой ячейки, Щ)К этом появляется импульс напряжения на первом выходе распределителя 7. Выходное напряжение триггера 8 поступает на вход триггера 1О ячейки 3. Следующий тактовый импульс переводит в нулевое состояние триггер 8 и в единичное триггер Ю;-- На третьем выходе рас1фёделителя появляется импульс напряжения, прк этом импульс единичного нагрян ения поступает на вход триггера 8, минуя триггер 11 отказавшей ячейки 4. Далее цикл работы устройства при двух отказавших ячейках повторяется. Таким образом, отказ любой ячейки вызывает отключение соответствующего триггера распределителя и передачу напряжения с выхода триггера исправной ячейки на уг завляющий вход триггера следукэщей за ней работоспособной ячейки, минуя триггеры отказавших ячеек. Использование изобретения обеспечивает работоспособность стабилизатора прк отказе всех, за исключением двух, гфеобразовательных ячеек, при этом провалы в Выходном напряжении стабилизатора исключаются, что обеспечивает высокую надежность устройства. Формула, изобретения 1. Устройство для угфавления многофазным импульсным регулятором с п параллельно соединенными преобразова тельными ячейками, содержащее широтноимпульсные модуляторы по числу ячеек, выход каждого из которых подсоединен через соответствующую 15)еобразовательную ячейку к входу канального датчика работоспособности и входы соединены соответственно с Выходом измерительного элемента, подсоединенного своим входом к выходам преобразовательных ячеек, я с выходами О -триггеров рас- гфеделителя импульсов, первые входы которьк подсоедкневы через делитель, частоты к выходу генератора тактовых импульсов, и блок логики, отличающееся тем, что, с целью повышения надежности, в нем блок логики вьшолнен на основе h ячеек переключе. НИН, каждая нз которых содержш эле-.

мент ИЛИ, два элемента И я элемент НЕ, причем вхоАы элемента ИЛИ подсоединены соответственно к выходу второго элемента И лредьшущейячейки переключения и к выходу предыдущего D «птера, выход элемента ИЛИ соединен с первыми входами первого и второго элементен И соответствующей ячейки переключения, вторые входы первсох) и второго элемент- тов И подсоединены к выходу канального датчика работоспособности, причем вход первого элемента И непосредственно и второго элемента И через элемент НЕ, , а выходы первого и второго элемешюв

И соединены соответственно с вторым входом соответствуюшегю С -триггера и с первым, входом элемента ИЛИ последующей ячейки переключения.

Источники информации, принятые во внимание при экспертизе

1.Юрченко А. И. и др. Многофазный импульсный стабилизатор постоянного напряжения. - Сб., Электронная техника в автоматике , вып. Ю. М., 1978,

с. 109, рис. 1.

2.Авторское свидетельство СССР № 758468, кл. Н 02 Р 13/18, 1980.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935914A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1561068A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1985 |

|

SU1348801A1 |

| Многофазный параметрический стабилизатор постоянного напряжения | 1989 |

|

SU1658130A1 |

| Многофазный параметрический стабилизатор напряжения постоянного тока | 1988 |

|

SU1628057A1 |

| Многофазный импульсный стабилизаторпОСТОяННОгО НАпРяжЕНия | 1979 |

|

SU824161A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1386977A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1386976A1 |

| Многофазный импульсный стабилизатор постоянного напряжения (его варианты) | 1984 |

|

SU1157532A1 |

Авторы

Даты

1982-09-07—Публикация

1981-03-03—Подача