113

Изобретение относится к вычислительной технике и может быть использовано в устройствах автоматического управления, обработки информации и в системах автоматизации научных исследований.

Целью изобретения является повышение быстродействия за счет параллельного вычисления среднего арифметического хранящихся в памяти чисел за время, не зависящее от их количества.

На чертеже представлена структурная схема устройства.

Устройство содержит вход 1 запуска регистра сдвига 2, элемент ИЛИ 3, регистр сдвига 4, регистр 5, регистр 6, триггер 7, генератор 8 тактовых импульсов, элемент задержки 9, регистр 10, элемент задержки 11, блок 12 ассоциативной памяти, разрядные вькоды блока 12, комбинационный сумматор 14, сумматор 15,элементы ИЛИ 16, выходы которых связаны со входами вычитателя 17, коммутатор 18, элемент 19 задержки, элементы И 20 - 22, счетчик 23, вход 24 начальной установки разрядности среднего арифметического устройства, выход 25 устройства, пороговый элемент 26.

Устройство работает следующим образом.

Перед началом работы по входу 24 в счетчик 23 заносится код М-требуе- мой разрядности результата (получаемого среднего арифметического).

Сигнал запуска, подаваемый по входу 1, устанавливает в ноль разряды регистров 2,5,4,10, устанавлийа- ет в единичное состояние триггер 7 и разряды регистра 6, запускает генератор 8 тактовых импульсов, через первый элемент задержки 9 заносит единицу в младший разряд регистра 2. Импульс с генератора 8 через элемент задержки 11 инициирует опрос блока 12, на выходах которого формируются сигналы совпадения для всех слов, младший разряд которых равен единице. Информация с вы- .ходов 13 подается на входы сумматора 14, на выходе которого формируется двоичный код суммы числа совпадений . Полученное число поступает на первый вход сумматора 15, где складывается со сдвинутым на один разряд содержимым регистра 10 (предварительно обнуленного сигналом за08402

пуска через элементы ИЛИ 3) так,что i-й разряд регистра 10 соответствует при сложении (1 + 1)-му разряду второго входа сумматора 15. Резуль5 тат заносится на регистр 10, причем младший разряд (п-й) регистра 10 заносится со сдвигом влево на регистр 4, начиная.с т-го разряда.

Импульс, сформированный генерато 0 ром импульсов 8, пройдя через элемент задержки 19, вызывает сдвиг влево содержимого регистра 2 и, пройдя через открытый единичным сигналом с выхода триггера 7 элемент И 21,вы 5 зывает сдвиг влево содержимого регистра 4. С формирование m генератором В следующего сигнала осуществляется следующее обращение к блоку 12 и устройство работает аналогично

20 описанному способу до тех пор, пока на выходе переполнения сдвига регистра 2 не будет сформирован сигнал единичного уровня (соответствует 1-му циклу опроса блока 12, где 1 разрядность чисел, хранящихся в блоке 12), который устанавливает триггер 7 в ноль. Сигнал с инверсного выхода триггера 7 поступает на элементы И 20, 22, разрешая работу вы читателя 17 и сдвиг содержимого регистра 4 вправо.

Код числа, хранящегося в регистре 10, подается через элементы ИЛИ 16 на вход порогового элемента 26 и вы35 читателя 17. Если это число меньше количества К чисел в блоке 12, то в (т+1)-й разряд регистра 4 заносится ноль, а в регистр 5 через коммутатор 18 - исходное число. Если это

40 число больше или равно К, то в (т+ Ч-1)-й разряд регистра 4 заносится единица, а в регистр 5 через коммутатор 18 заносится разность между числом, поступившим на вход вычитателя 17 и

45 числом К. Работа вычитателя 17 синхронизируется тактовым сигналом,задержанным элементом 11 задержки через элемент И 20. Этот же сигнал, дополнительно задержанный элементом

50 19 задержки,формирует на входе элемента И 22 сигнал, по которому, производится сброс в ноль регистра 10 и запись кода в регистр 5, а также запись сигнала в (т+1)-й разряд ре55 гистра 4, выполняемая одновременно со сдвигом вправо содержимого последнего. Кроме того, импульс с выхода элемента 11 задержки через элемент И 20 поступает на счетчик 23,

3

где происходит вычитание единицы из содержимого счетчика 23. В дальнейшем на каждый (j-1)-й вход (,3,. .., п-1) вычитателя 17 поступает сигнал с j-ro выхода регистра 5, а на (з-1)-й вход узла вычитателя 17 - сигнал с выхода регистра 4.

Описанная последовательность операции повторяется до тех пор, пока содержимое счетчика 23 не станет равно нулю. При этом в регистре сдвига 4 будет сформировано среднее арифметическое с точностью до М разрядов, причем старший разряд среднего будет располагаться справа.

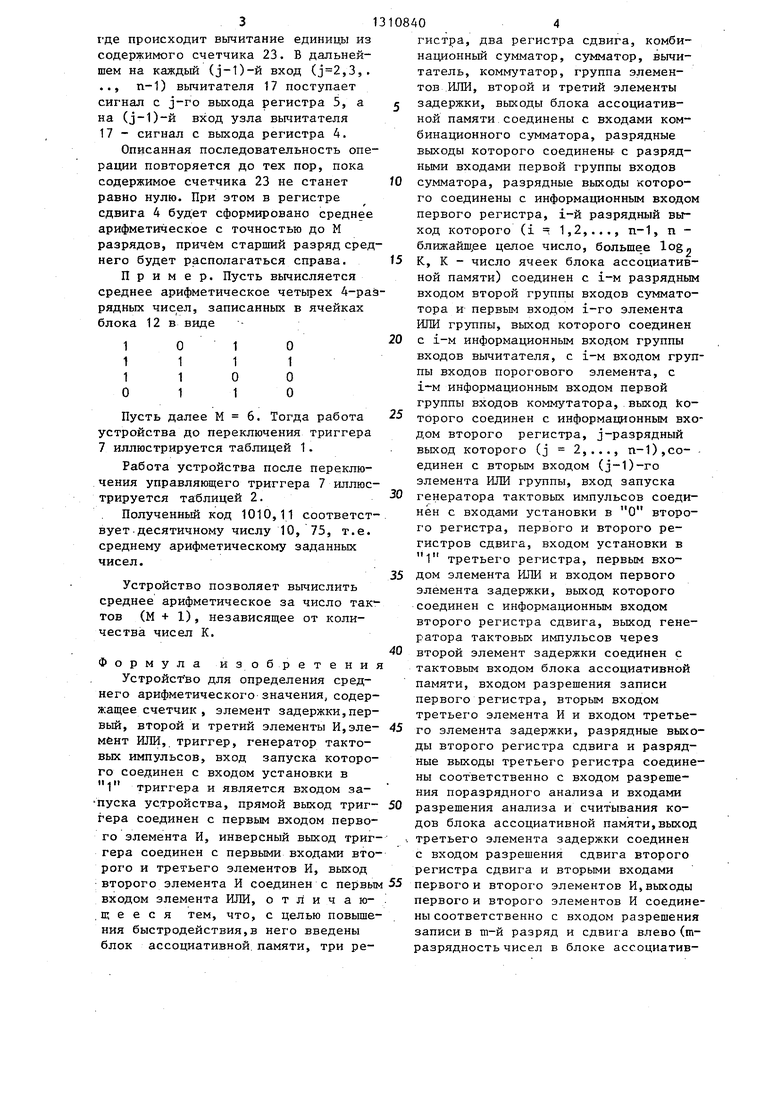

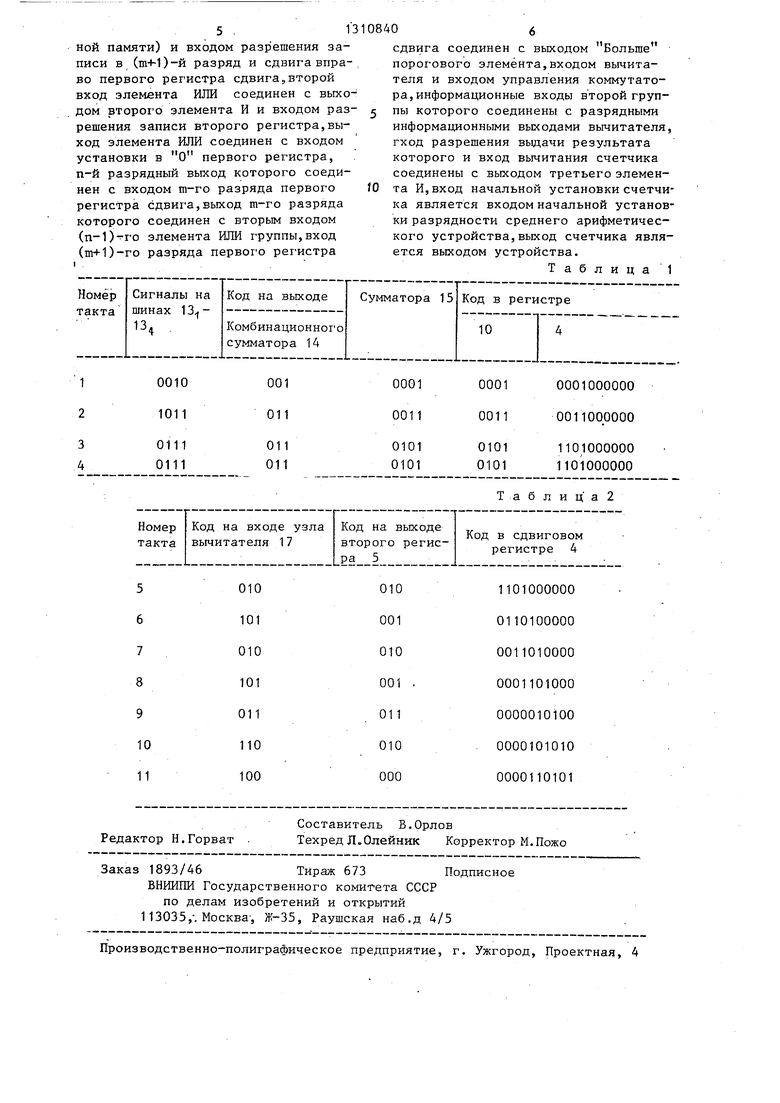

Пример. Пусть вычисляется среднее арифметическое четьфех 4-рарядных чисел, записанных в ячейках блока 12 в виде

Пусть далее М 6. Тогда работа устройства до переключения триггера 7 иллюстрируется таблицей 1.

Работа устройства после переключения управляющего триггера 7 иллюстрируется таблицей 2.

Полученный код 1010,11 соответствует десятичному числу 10, 75, т.е. среднему арифметическому заданных чисел.

Устройство позволяет вычислить среднее арифметическое за число тактов (М + 1), независящее от количества чисел К.

Формула изобретени

Устройст во для определения среднего арифметического значения, содержащее счетчик , элемент задержки,пер- вьй, второй и третий элементы И,элемент ИЛИ, триггер, генератор тактовых импульсов, вход запуска которого соединен с входом установки в триггера и является входом за 1-пуска устройства, прямой выход триггера соединен с первым входом первого элемента И, инверсный выход триггера соединен с первыми входами второго и третьего элементов И, выход второго элемента И соединен с первым входом элемента ИЛИ, отличающееся тем, что, с целью повышения быстродействия,в него введены блок ассоциативной, памяти, три ре

404

гистра, два регистра сдвига, комбинационный сумматор, сумматор, вычи- татель, коммутатор, группа элементов ИЛИ, второй и третий элементы

задержки, выходы блока ассоциативной памяти соединены с входами комбинационного сумматора, разрядные выходы которого соединены- с разрядными входами первой группы входов сумматора, разрядные выходы которого соединены с информационным входом первого регистра, i-й разрядный выход которого (i т 1,2,..., п-1, п - ближайщее целое число, большее 1 К, К - число ячеек блока ассоциативной памяти) соединен с i-м разрядным входом второй группы входов суммато- тора и первым входом i-ro элемента ИЛИ группы, выход которого соединен с i-M информационным входом группы входов вычитателя, с i-м входом группы входов порогового элемента, с i-M информационным входом первой группы входов коммутатора, выход hoторого соединен с информационным входом второго регистра, j-разрядный выход которого (J 2,..., п-1),со- единен с вторым входом (j-l)-ro элемента ИЛИ группы, вход запуска генератора тактовых импульсов соединён с входами установки в О второго регистра, первого и второго ре

гистров сдвига, входом установки в третьего регистра, первым вхоЧ

дом элемента ИЛИ и входом первого элемента задержки, выход которого соединен с информационным входом второго регистра сдвига, выход генератора тактовых импульсов через второй элемент задержки соединен с тактовым входом блока ассоциативной памяти, входом разрешения записи первого регистра, вторым входом третьего элемента И и входом третьего элемента задержки, разрядные выходы второго регистра сдвига и разрядные выходы третьего регистра соединены соответственно с входом разрешения поразрядного анализа и входами разрешения анализа и считывания кодов блока ассоциативной памяти,выход третьего элемента задержки соединен с входом разрешения сдвига второго регистра сдвига и вторьми входами первого и второго элементов И,выходы первого и второго элементов И соединены соответственно с входом разрешения записи в тп-й разряд и сдвига влево (т- разрядность чисел в блоке ассоциатив5 .13

ной памяти) и входом разрешения записи в (т+-1)-й разряд и сдвига вправо первого регистра сдвига„второй вход элемента ИЛИ соединен с выходом второго элемента И и входом разрешения записи второго регистра,выход элемента ИЛИ соединен с входом установки в О первого регистра, п-й разрядный выход которого соединен с входом т-го разряда первого регистра сдвига,выход т-го разряда которого соединен с вторым входом (n-l)-ro элемента ИЛИ группы,вход (m+D-ro разряда первого регистра

0010 1011

0111 0111

001 011

011 011

Редактор Н.Горват .

Составитель В.Орлов

Техред Л.Олейник Корректор М.Пожо

Заказ 1893/46Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035,-. Москва, Ж-35, Раушская наб.д 4/5

Производственно-полиграфическое предприятие, г. Ужгород, Проектная, 4

06

сдвига соединен с выходом Больше порогового элемента,входом вычита- теля и входом управления коммутатора, информационные входы второй группы которого соединены с разрядными информационными выходами вычитателя, гход разрешения выдачи результата которого и вход вычитания счетчика соединены с выходом третьего элемента И, вход начальной установки счетчика является входом начальной установки разрядности среднего арифметического устройства,выход счетчика является выходом устройства.

Таблица 1

т а б л и ц а 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения среднего арифметического значения | 1989 |

|

SU1658169A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕЙ НАРАБОТКИ НА ПОЛНЫЙ ОТКАЗ СТРУКТУРНО-СЛОЖНОЙ СИСТЕМЫ | 1992 |

|

RU2041493C1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1652982A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1985 |

|

SU1283752A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обработки результатов измерений. Цель изобретения - повышение быстродействия.Устройство позволяет повысить скорость вычисления среднего арифметического значения за счет распараллеливания вычислений во времени. Устройство содержит регистры 2,4,5,6,10, элементы ИЛИ 3,16, триггер 7, генератор 8 тактовых импульсов, элементы 9,11, 19 задержки, блок 12 ассоциативной памяти, сумматоры 14, 15, вычитатель 1.7, коммутатор 18, элементы И 20, 21, 22, счетчик 23, пороговый элемент 26. 1 ил., 2 табл. (Л 00 00 4

| Механизм для фиксации исходного положения измерительного устройства в автоматах для контроля твердости | 1950 |

|

SU93363A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для вычисления текущей оценки среднего значения | 1977 |

|

SU619924A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для определения среднего арифметического значения | 1981 |

|

SU1008751A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-15—Публикация

1986-01-13—Подача