И

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой нерекурсивный фильтр | 1989 |

|

SU1665502A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Устройство для выполнения дискретных ортогональных преобразований | 1984 |

|

SU1233168A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| Цифровой нерекурсивный фильтр | 1988 |

|

SU1566472A1 |

| Конвейерный аналого-цифровой преобразователь | 1986 |

|

SU1381706A1 |

| СПОСОБ ЦИФРОВОЙ РЕКУРСИВНОЙ ПОЛОСОВОЙ ФИЛЬТРАЦИИ И ЦИФРОВОЙ ФИЛЬТР ДЛЯ РЕАЛИЗАЦИИ СПОСОБА | 2014 |

|

RU2579982C2 |

| Устройство для адаптивного скользящего сглаживания | 1986 |

|

SU1387017A1 |

| ВОКОДЕРНАЯ ИНТЕГРАЛЬНАЯ СХЕМА ПРИКЛАДНОЙ ОРИЕНТАЦИИ | 1995 |

|

RU2183034C2 |

Изобретение относится к радиотехнике, в частности к цифровой обработке радио-, гидро- и звуколокационных сигналов, и может быть применено для цифровой фильтрации в реальном масштабе времени сигналов с высокой частотой дискретизации. Цель изобретения - повышение быстродействия. Рекурсивный цифровой фильтр содержит регистры 1-3 сдвига, блоки 4 задержки, блоки 5 элементов И, группы 6 элементов И, блок 7 памяти коэффициентов, конвейерный преобразователь 8 многострочного кода и сумматор 9. На вход 10 подается входной сигнал, на вход 11 - последовательность тактовых импульсов, а на вход 12 - адрес, осуществляющий выбор импульсной характеристики. Повышение быстродействия достигается за счет выполнения преобразователя 8 многострочного кода конвейерным. 1 з.п. ф-лы, 6 ил.

Фиг.1

О

ел

00 GJ XJ О

13

Изобретение относится к радиотехнике, в частности к цифровой обработке сигналов, и может быть применено в радиолокации, связи и других областях техники для согласованной фильтрации сигналов с высокой частотой дискретизации.

Цель изобретения - повышение быстродействия.

На фиг. 1 приведена электрическая структурная схема рекурсивного цифрового фильтра; на фиг. 2 - электрическая структурная схема конвейерного преобразователя многострочного кода: на фиг. 3 и 4 - матрица частичных произведений, формирующихся на выходной шине одной из групп элементов И и одного из блоков элементов И при разрядности входных данных и коэффициентов импульсной характеристики, равной 4; на фиг. 5 - результирующая матрица частичных произведений на входе конвейерного устройства грузового суммирования; на фиг. 6 - процесс преобразования многострочного кода в ступенях преобразования конвейерного преобразователя много- строчного кода.

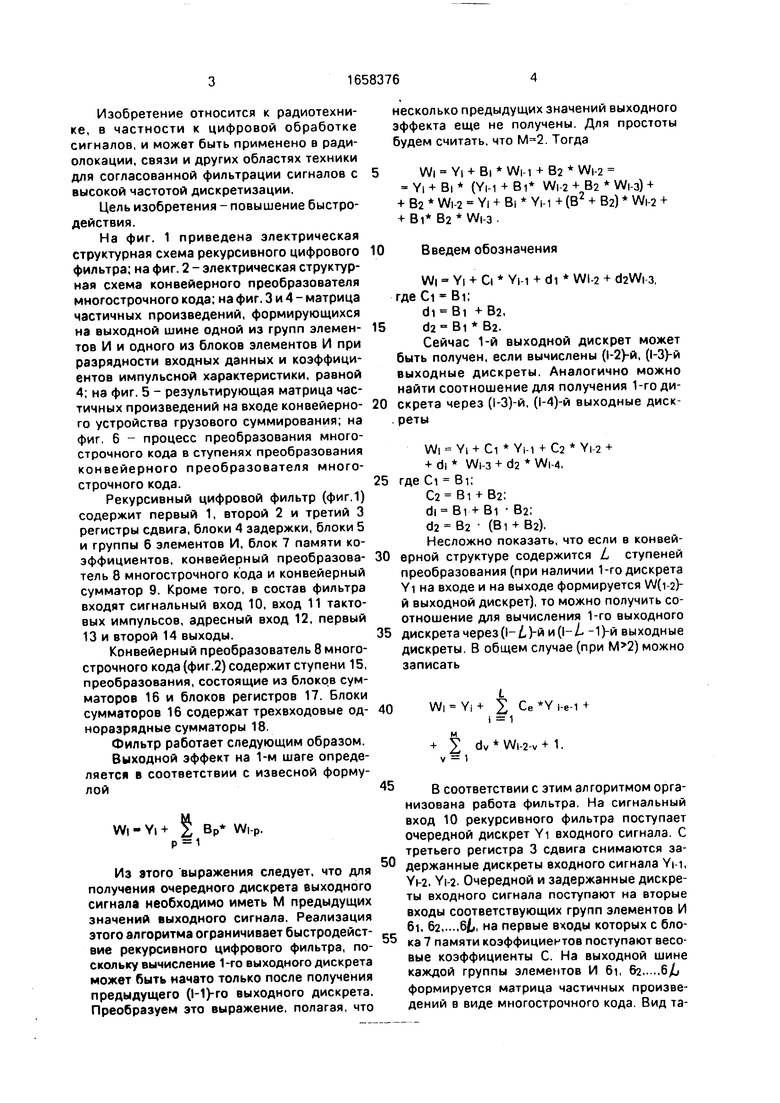

Рекурсивный цифровой фильтр (фиг.1) содержит первый 1, второй 2 и третий 3 регистры сдвига, блоки 4 задержки, блоки 5 и группы 6 элементов И, блок 7 памяти коэффициентов, конвейерный преобразователь 8 многострочного кода и конвейерный сумматор 9. Кроме того, в состав фильтра входят сигнальный вход 10, вход 11 тактовых импульсов, адресный вход 12, первый 13 и второй 14 выходы.

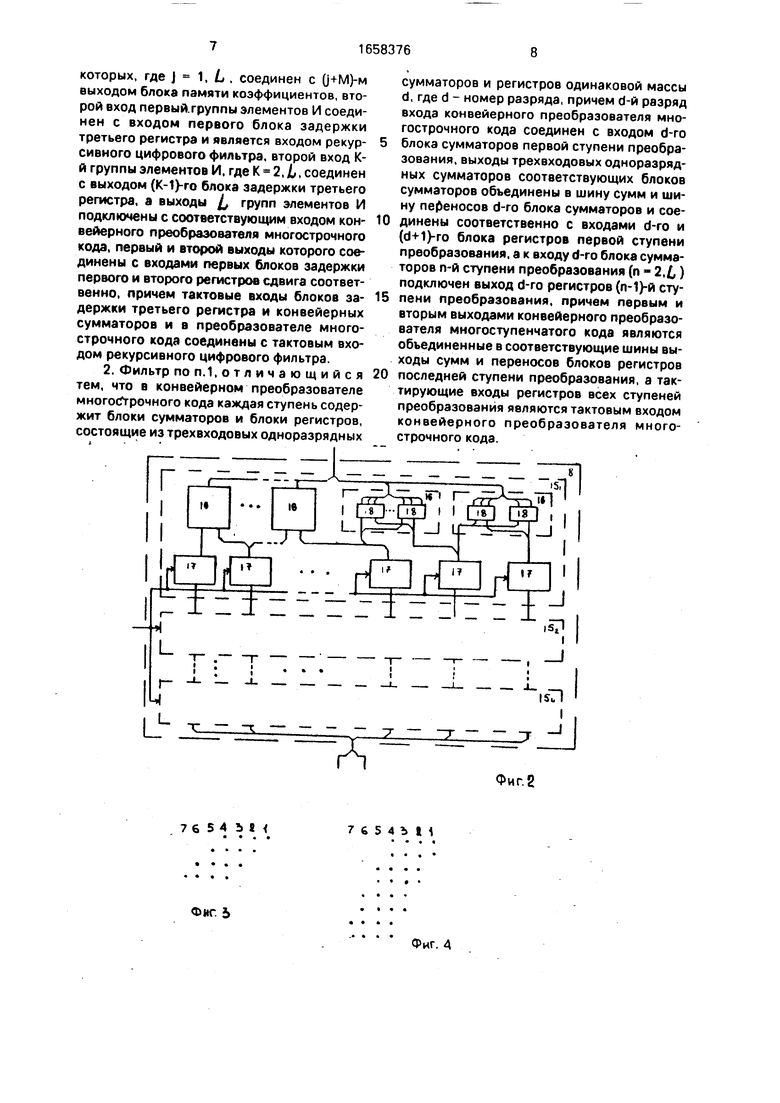

Конвейерный преобразователь 8 многострочного кода (фиг.2) содержит ступени 15, преобразования, состоящие из блоков сумматоров 16 и блоков регистров 17. Блоки сумматоров 16 содержат трехвходовые одноразрядные сумматоры 18.

Фильтр работает следующим образом. Выходной эффект на 1-м шаге определяется в соответствии с извесной формулой

WI-YI+ §

р 1

W|-r

Из этого выражения следует, что для получения очередного дискрета выходного сигнала необходимо иметь М предыдущих значений выходного сигнала. Реализация этого алгоритма ограничивает быстродействие рекурсивного цифрового фильтра, поскольку вычисление 1-го выходного дискрета может быть начато только после получения предыдущего (1-1)-го выходного дискрета. Преобразуем это выражение, полагая, что

несколько предыдущих значений выходного эффекта еще не получены. Для простоты будем считать, что . Тогда

Wi YI + Bi Wi-i + 82 Wi-2 Yi -i- Bi (Yi-i + Bi Wi-2 + 82 Wi-з) + + 82 Wi-2 Yi + Bi YM + (B2 + 62) Wi-2 + + 81 62 Wi-3.

Введем обозначения

Wi - YI + Ci YM + di WI-2 + d2Wi-3. где Ci Bi;

di Bi +82, .

Сейчас 1-й выходной дискрет может

быть получен, если вычислены (1-2)-й, (1-3}-й

выходные дискреты. Аналогично можно

найти соотношение для получения 1-го дискрета через (-3)-й, (-4)-й выходные дискреты

Wi Yi + Ci YM + Сг YI-Z +

+ di Wi-з + d2 Wi-4, гдеС1 В1;

C2 Bi + 82:

di Bi + Bi 82;

d2 82 (81 + 82).

Несложно показать, что если в конвей- ерной структуре содержится L ступеней преобразования (при наличии 1-го дискрета YI на входе и на выходе формируется W(i-2)- й выходной дискрет), то можно получить соотношение для вычисления 1-го выходного дискретачерез(1-Ј}-йи(1-Л -1)-й выходные дискреты. В общем случае (при ) можно записать

40

W| - Yi + J Се Y i-e-1 +

i 1

+ 2 dv W|-2-v + 1.

v 1

ц соответствии с этим ал горитмом организована работа фильтра. На сигнальный вход 10 рекурсивного фильтра поступает очередной дискрет Yi входного сигнала. С третьего регистра 3 сдвига снимаются задержанные дискреты входного сигнала YM, Yh2, Yi-2. Очередной и задержанные дискреты входного сигнала поступают на вторые входы соответствующих групп элементов И 6i, 626(1, на первые входы которых с бло«а 7 памяти коэффициентов поступают весовые коэффициенты С. На выходной шине

каждой группы элементов И 6i, 626/j

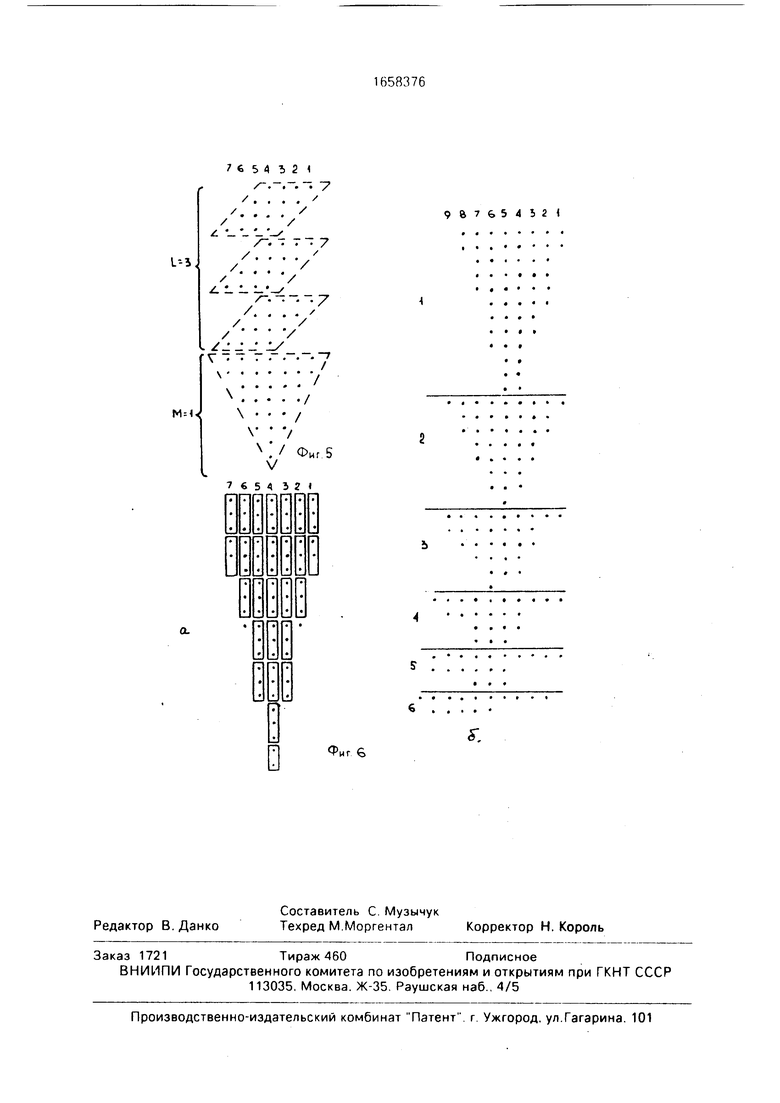

формируется матрица частичных произведений в виде многострочного кода. Вид такого кода для разрядности входных данных и коэффициентов, равной четырем, представлен на фиг. 3. На фиг. 3 точками обозначены двоичные цифры, сверху проставлены номера разрядов.

С конвейерного преобразователя 8 многострочного кода снимается выходной дискрет, представленный двухстрочным кодом, причем первая и вторая строки этого кода поступают на первые блоки 4 задержки, соответствующих регистров 1 и 2 сдвига. На входы блоков 5i, 625М элементов И поступают с соответствующей задержкой с первого 1 и второго 2 регистров сдвига предшествующие выходные дискреты, представленные двухстрочными кодами. При этом первая и вторая строки этого кода поступают соответственно на второй и третий входы блоков 5 элементов И, на первые входы которого поступают весовые коэффициенты с блока 7 памяти коэфэфициентов. На выходе каждого блока 5 элементов и формируется матрица частичных произведений в виде многострочного кода. Вид такого кода для разрядности входных данных и коэффициентов; равной четырем, представлен на фиг. 4.

Операция суммирования результатов умножений выполняется в конвейерном преобразователе 8 многострочного кода следующим образом.

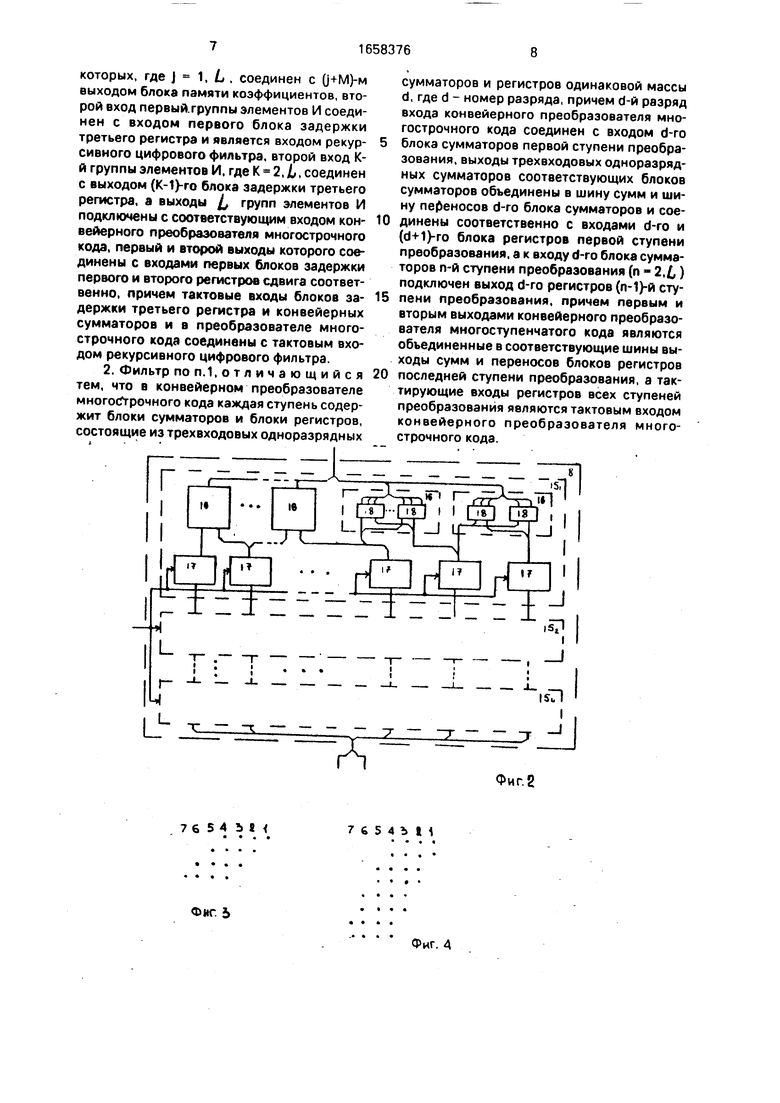

Многострочные коды с блоков 5 и групп 6 элементов И образуют на входе конв эйер- ного преобразователя 8 многострочного кода результирующий многострочный код, вид которого при оговоренных условиях для и if 3 представлен на фиг. 5. В конвейерном преобразователе 8 многострочного кода за тактов (в /,, ступенях преобразования) осуществляется последовательное преобразование многострочного кодч в двухстрочный. В момент ступени 15 преобразования многострочный код поступает на блоки трехвходовых одноразрядных сумматоров 16, а результаты преобразования запоминаются в блоках регистров 17 этой же ступени 15 преобразования. На фиг. 6 показан процесс преобразования многоступенчатого кода, изображенного на фиг. 5, в двухстрочный код, причем рамками на фиг. ба обведены числа, подаваемые на вход одного трехвходового одноразрядного сумматора 18. Как следует из анализа фиг. 6, исходный многострочный код за шесть тактов (номера тактов обозначены цифрами слева) будет преобразован в двухстрочный код. Таким образом, для указанных условий конвейерный преобразователь многострочного кода должен содержать jL. 6 ступеней 15 преобразования.

Двухстрочный код с конвейерного преобразователя 8 многострочного кода, соот5 ветствующий (I- Ь)-му выходному дискрету Wi-2, может быть снят с второго выхода фильтра 14, при необходимости представления результата фильтрации традиционным однострочным кодом используется первый

0 выход фильтра 13, являющийся выходом конвейерного сумматора 9. Последний обеспечивает преобразование двухстрочного кода в однострочный код. Синхронная циркуляция информации в конвейерной

5 структуре фильтра обеспечивается тактовыми импульсами, поступающим на вход 11 тактовых импульсов фильтра.

Формула изобретения

0 выходом которого являются вторые входы элементов И первой и второй групп и выходы элементов И обоих групп соответственно, преобразователь многострочного кода, входы которого соединены с выходами

5 блоков элементов И, конвейерный сумматор, первый и второй входы которого соединены с первым и вторым выходами преобразователя многострочного кода, и блок памяти коэффициентов, 1-й выход ко0 торого, где i 1,-М, соединен с первым входом i-ro блока элементов И, второй вход которого, за исключением второго входа первого блока элементов И, соединен с выходом (1-1)-го блока задержки пер5 вого регистра сдвига, а второй вход первого блока элементов И соединен с входом первого блока задержки первого регистра сдвига, причем тактовые входы блоков задержки первого и второго регистров сдви0 га и блока памяти коэффициентов являются тактовым входом рекурсивного цифрового фильтра, отличающийся тем, что, с целью повышения быстродействия, преоба- эователь многострочного кода выполнен

5 конвейерным, содержащим ступеней преобразования,/, 1, и введены третий регистр сдвига, содержащий/j -1 последовательно соединенных блоков задержки и /j групп элементов И, первый вход J-й из

которых, где J 1, L , соединен с Q+MJ-м выходом блока памяти коэффициентов, второй вход первый группы элементов И соединен с входом первого блока задержки третьего регистра и является входом рекурсивного цифрового фильтра, второй вход К- й группы элементов И, где К 2, L, соединен с выходом (К-1)-го блока задержки третьего регистра, а выходы /, групп элементов И подключены с соответствующим входом конвейерного преобразователя многострочного кода, первый и второй выходы которого соединены с входами первых блоков задержки первого и второго регистров сдвига соответ- венно, причем тактовые входы блоков задержки третьего регистра и конвейерных сумматоров и в преобразователе многострочного кода соединены с тактовым входом рекурсивного цифрового фильтра.

76 54 Ь 8

сумматоров и регистров одинаковой массы d, где d - номер разряда, причем d-й разряд входа конвейерного преобразователя многострочного кода соединен с входом d-ro

блока сумматоров первой ступени преобразования, выходы трехвходовых одноразрядных сумматоров соответствующих блоков сумматоров объединены в шину сумм и шину переносов d-ro блока сумматоров и соединены соответственно с входами d-ro и (d+1)-ro блока регистров первой ступени преобразования, а к входу d-ro блока сумматоров n-й ступени преобразования (п - 2,Ј,) подключен выход d-ro регистров (п-1)-й ступени преобразования, причем первым и вторым выходами конвейерного преобразователя многоступенчатого кода являются объединенные в соответствующие шины выходы сумм и переносов блоков регистров

последней ступени преобразования, а тактирующие входы регистров всех ступеней преобразования являются тактовым входом конвейерного преобразователя многострочного кода.

7 6 5 4 Ъ I 1

7654521

/-.-,-. - /....

//

/ S

/-.- т т 7

ij // / /

у

/- ----7 /....

//

/ ; ; ; v

.-.-.7 ч...... v

:::../

н . . . / - ; /

V

1 в 5 4 з г

I

Риг 6

9&7&54521

Р

Ј

| Авторское свидетельство СССР Nt 1390782 | |||

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-06-23—Публикация

1989-07-27—Подача