Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки информации с высокими требованиями к частотной избирательности выполнения фильтрации для выделения полезного сигнала в условиях действия мощных широкополосных помех.

Известны способы цифровой рекурсивной фильтрации сигналов, позволяющие выделять полезный сигнал в условиях действия помех (Патент РФ №2188499, от 07.04.2000, и патент РФ №2187883, от 19.06.2000].

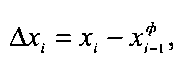

Указанные способы цифровой фильтрации основаны на сравнении фильтруемого цифрового сигнала xi с выходным сигналом  путем определения разностного сигнала

путем определения разностного сигнала  а выходной сигнал

а выходной сигнал  формируют в виде суммы предыдущего значения

формируют в виде суммы предыдущего значения  и дополнительного сигнала Δi, причем дополнительный сигнал Δi выбирают равным значению Δ, если ΔxI≥Δ, значению (-Δ), если ΔxI≤Δ, и нулю, если -Δ<Δi<Δ, где Δ соответствует максимально допустимому превышению сигнала помехи над полезным сигналом (патент №2188499) или цене единицы младшего разряда цифрового кода xi (патент №2187883).

и дополнительного сигнала Δi, причем дополнительный сигнал Δi выбирают равным значению Δ, если ΔxI≥Δ, значению (-Δ), если ΔxI≤Δ, и нулю, если -Δ<Δi<Δ, где Δ соответствует максимально допустимому превышению сигнала помехи над полезным сигналом (патент №2188499) или цене единицы младшего разряда цифрового кода xi (патент №2187883).

Недостатком этих способов является невозможность выполнения цифровой рекурсивной полосовой фильтрации, так как в них используют преобразования сигналов первого порядка на основе формирования первых разностей xi-xi-1 задержками на один период частоты дискретизации. Такое преобразование обеспечивает сглаживание фильтруемого сигнала на фоне помех, лежащих в более низкочастотной области, чем полезный сигнал, и не решает задачи полосовой фильтрации, для которой в самом простейшем варианте требуется выполнение преобразования в соответствии с разностным управлением второго порядка.

В том случае, когда требуется высокая избирательность полосовой фильтрации для выделения полезного сигнала из помех, используется преобразование более высокого порядка.

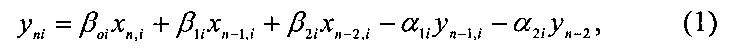

Известен способ цифровой фильтрации, использующий последовательное (каскадное) преобразование фильтруемого сигнала (Л.М. Гольденберг, Б.М. Матюшкин, М.Н. Полян. Цифровая обработка сигналов. Справочник. М.: Радио и связь, 1985, стр. 52, 144, 145). Указанный способ цифровой рекурсивной фильтрации включает r последовательных ступеней преобразования фильтруемого сигнала, в каждой из которых выполняют весовое суммирование задержанных значений входного (xn) и выходного (yn) сигналов так, что отфильтрованный сигнал i-й ступени фильтрации (i=0,1,…r) является входным сигналом для (i+1)-й ступени преобразования. Преобразование сигнала i-ой ступени в этом способе выполняют по правилу

где xni, yni - значение входного и выходного сигналов i-й ступени преобразования;

β1i, α1i - значения весовых коэффициентов i-й ступени преобразования.

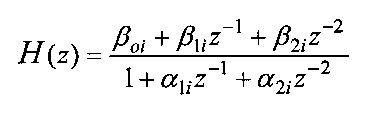

Преобразованию (1) соответствует передаточная функция

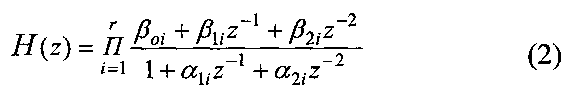

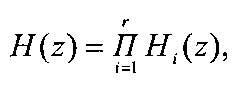

Для фильтра с числом ступеней преобразования, равном r, передаточная функции фильтра:

Недостатком известного способа является низкое быстродействие при выполнении полосовой фильтрации из-за необходимости выполнять в каждом i-м звене преобразование вида: β1ixn-1,i, α1iyn-1,i, причем увеличение времени при выполнении фильтрации тем больше, чем выше требования к избирательности полосовой фильтрации (чем больше требуется число ступеней преобразования r). Так, например, при выполнении полосовой рекурсивной фильтрации известным способом с четырьмя ступенями преобразования (r=4), при котором каждая ступень выполняет преобразование сигнала по правилу (1), крутизна скатов амплитудно-частотной характеристики (АХЧ) составляет 40 децибел на октаву. При этом требуется выполнение двадцати операций умножения многоразрядных чисел и шестнадцати операций арифметического сложения, из-за чего быстродействие известного способа фильтрации оказывается низким.

Известен программно-управляемый цифровой фильтр (Авторское свидетельство СССР №1338006, от 22.07.1985), реализующий приведенный выше способ фильтрации.

Фильтр содержит блок задания коэффициентов, два блока памяти, арифметический блок, два мультиплексора, сумматор, выходной регистр, блок управления, счетный триггер, инвертор, элементы И и ИЛИ. Программно-управляемый цифровой фильтр выполнен в соответствии с каскадной формой реализации цифровых рекурсивных фильтрах на звеньях второго порядка. Каждое звено этого фильтра производит преобразование сигнала в соответствии с разностным уравнением (1). Фильтр, в зависимости от загружаемых в его память весовых коэффициентов, может выполнять фильтрацию нижних частот, верхних частот и полосовую фильтрацию.

Недостаткам этого фильтра является большой объем необходимого оборудования для его реализации. Кроме того, при реализации полосовой фильтрации быстродействие фильтра оказывается низким, так как при этом используется последовательное включение звеньев нижних и верхних частот, что приводит к необходимости выполнения большего числа арифметических операций.

Известен также программируемый цифровой фильтр (Авторское свидетельство СССР №1224980, от 13.12.1984), реализующий описанный выше способ цифровой фильтрации.

Этот фильтр содержит регистр хранения текущего значения входного сигнала, четыре блока умножения, четыре сумматора, два элемента задержки, два мультиплексора, четыре преобразователя кода, дешифратор, блок вычисления коэффициента передачи, регистр хранения состояния фильтра, два инвертора и блок синхронизации, обеспечивающий управление работой фильтра. Фильтр перед началом выполнения фильтрации настраивается на фильтрацию нижних частот, полосовую и режекторную фильтрацию путем выбора одного их четырех уравнений второго порядка. Фильтр также реализует описанный выше известный способ цифровой фильтрации.

Недостатком фильтра является низкая избирательность при выполнении полосовой фильтрации. Кроме того, фильтр сложен в реализации и имеет низкое быстродействие.

Наиболее близким к предлагаемому способу является способ цифровой рекурсивной полосовой фильтрации (Патент РФ №2460130, от 13.04.2011), принимаемый в качестве прототипа предлагаемого способа. Этот известный способ цифровой рекурсивной полосовой фильтрации включает r последовательных ступеней преобразования фильтруемого сигнала, в каждой из которых выполняют весовое суммирование задержанных значений входного (xni) и выходного (yni) сигналов так, что отфильтрованный сигнал i-й ступени фильтрации (i=0,1,…r) является входным сигналом для (i+1)-й ступени, а преобразование сигнала i-й ступени формируют по правилу

yni=К0(xni-2xn-2,i+xn-4,i)-K1yn-2,i-K2yn-4,i,

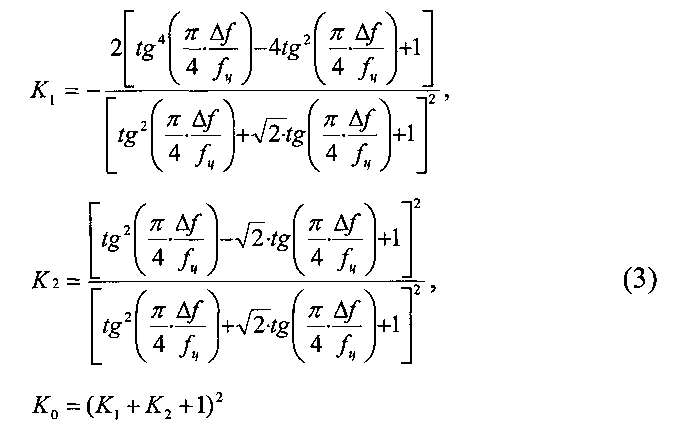

причем предварительно вычисленные весовые коэффициенты фильтрации выбирают, исходя их требуемых значений полосы пропускания Δf и центральной полосы пропускания fц, а значения частоты дискретизации задают в четыре раза больше центральной частоты полосы пропускания, при этом весовые коэффициенты фильтрации вычисляют по формулам:

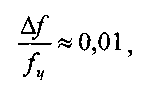

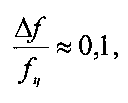

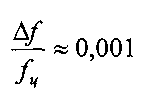

Недостатком известного способа является низкая избирательность при выполнении цифровой фильтрации, которая тем ниже, чем уже ширина полосы пропускания. Для выполнения фильтрации с требуемыми значениями прямоугольности и крутизны скатов амплитудно-частотной характеристики (АЧХ) в известном способе требуется увеличение числа ступеней преобразования фильтруемого сигнала. Это приводит к значительному снижению быстродействия известного способа фильтрации.

Так, например, при относительной ширине полосы пропускания  для обеспечения тех же значений крутизны скатов, которые получены, например, при

для обеспечения тех же значений крутизны скатов, которые получены, например, при  число ступеней преобразования должно быть увеличено в два раза, что приводит к снижению быстродействия выполнения фильтрации вдвое. Более узкие полосы пропускания порядка

число ступеней преобразования должно быть увеличено в два раза, что приводит к снижению быстродействия выполнения фильтрации вдвое. Более узкие полосы пропускания порядка  с использованием известного способа фильтрации не могут быть вообще реализованы так, как при увеличении числа ступеней преобразования ширина полосы пропускания перестает изменяться.

с использованием известного способа фильтрации не могут быть вообще реализованы так, как при увеличении числа ступеней преобразования ширина полосы пропускания перестает изменяться.

Наиболее близким к предлагаемому цифровому рекурсивному полосовому фильтру является цифровой фильтр, реализующий способ цифровой рекурсивной полосовой фильтрации (Патент РФ №2460130, от 13.04.2011].

Цифровой рекурсивный полосовой фильтр содержит три блока умножения, два сумматора, два блока хранения выборочных значений сигнала, блок хранения коэффициентов, умножитель на два, мультиплексор, три регистра и блок управления. В цифровом фильтре-прототипе входом фильтра является информационный вход первого регистра, вход записи которого подключен к первому выходу блока управления, а выход соединен с первым входом мультиплексора. Второй вход мультиплексора соединен с выходом второго регистра, входами второго блока хранения выборочных значений сигнала и третьего регистра. Управляющий вход мультиплексора соединен со вторым выходом блока управления. Выход мультиплексора соединен с первым входом сумматора и информационным входом первого блока хранения выборочных значений сигнала, управляющий вход которого объединен с управляющим входом второго блока хранения выборочных значений сигнала и подключен к третьему выходу блока управления, четвертый выход которого соединен с входом записи первого блока хранения выборочных значений сигнала. Первый выход первого блока хранения выборочных значений сигнала через умножитель на два связан со вторым входом первого сумматора, третий вход которого соединен со вторым выходом первого блока хранения, а выход - со вторым входом первого блока умножения, подключенного первым входом ко второму выходу блока хранения коэффициентов, первый и третий выходы которого соединены с первыми входами второго и третьего блоков умножения соответственно, а вход соединен с пятым выходом блока управления. Вторые входы второго и третьего блоков умножения соединены с первым и вторым выходами второго блока хранения выборочных значений сигнала. Выходы первого, второго и третьего умножителей соединены соответственно со вторым, первым и третьим входами второго сумматора, выход которого соединен с информационным входом второго регистра, подключенного входом записи к шестому выхода блока управления. Вход блока управления является входом установки номера фильтра. Седьмой и восьмой выходы блока управления соединены соответственно с входами записи второго блока хранения выборочных значений сигнала и третьего регистра, выход которого является выходом фильтра.

В первом сумматоре первый и третий входы суммирующие, а второй вход вычитающий.

Во втором сумматоре первый и третий входы вычитающие, а второй вход суммирующий.

Недостатком фильтра-прототипа является его низкая избирательность при выполнении цифровой фильтрации, которая тем ниже, чем уже необходимая ширина полосы пропускания фильтра. Полосы пропускания  с использованием фильтра-прототипа не могут быть реализованы.

с использованием фильтра-прототипа не могут быть реализованы.

Кроме того, фильтр-прототип сложен в реализации.

Технический результат изобретения заключается в создании способа цифровой рекурсивной полосовой фильтрации и цифрового фильтра для реализации этого способа, обеспечивающих повышение избирательности цифровой полосовой фильтрации без снижения быстродействия выполнения фильтрации, а также в упрощении фильтра без снижения его быстродействия.

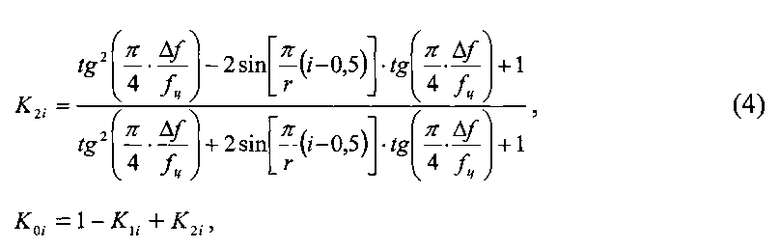

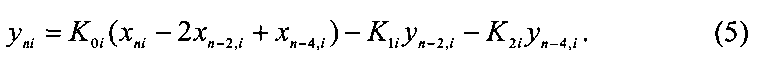

Указанный технический результат достигается тем, что в способе цифровой рекурсивной полосовой фильтрации, включающем r последовательных ступеней преобразования фильтруемого сигнала, в каждой из которых выполняют весовое суммирование задержанных значений входного (xni) и выходного (yni) сигналов так, что отфильтрованный сигнал i-й ступени фильтрации (i=1,…r) является входным сигналом для (i+1)-й ступени, при этом весовые коэффициенты определяют исходя из требуемых значений полосы пропускания Δf и центральной частоты полосы пропускания fц, значение частоты дискретизации задают в четыре раза больше центральной частоты полосы пропускания, в соответствии с изобретением, весовые коэффициенты фильтрации определяют независимо для каждой ступени преобразования фильтруемого сигнала, по формулам:

а преобразование фильтруемого сигнала i-й степени формируют по правилу

Указанный технический результат также достигается тем, что в цифровой рекурсивный полосовой фильтр, содержащий блок умножения, сумматор, блок хранения выборочных значений сигнала, блок хранения коэффициентов, мультиплексор, три регистра и блок управления, вход которого является входом установки параметров фильтрации, а первый, второй и третий выходы соединены соответственно с входом записи первого регистра, управляющим входом блока хранения выборочных значений сигнала и управляющим входом мультиплексора, вход первого регистра является информационным входом фильтра, а выход соединен с первым входом мультиплексора, второй вход которого соединен с выходом второго регистра и информационным входом третьего регистра, четвертый выход блока управления соединен с информационным входом блока хранения коэффициентов, выход которого соединен с первым входом блока умножения, пятый выход блока управления соединен с входом записи второго регистра, подключенного информационным входом к выходу сумматора, шестой выход блока управления соединен с входом записи третьего регистра, выход которого является выходом фильтра, в соответствии с изобретением введен четвертый регистр, соединенный информационным входом с выходом блока умножения, а выходом - с третьим входом мультиплексора, первый вход которого соединен с первым информационным входом блока хранения выборочных значений сигнала, выход мультиплексора соединен со вторым входом блока умножения и первым входом сумматора, второй вход которого соединен с выходом второго регистра и вторым информационным входом блока хранения выборочных значений сигнала, первый, второй, третий, четвертый, пятый и шестой выходы блока хранения выборочных значений сигнала соединены соответственно с четвертым, пятым, шестым, седьмым, восьмым и девятым входами мультиплексора, седьмой, восьмой, девятый, десятый и одиннадцатый выходы блока управления соединены соответственно с входами установки режима запись-чтение, адреса и разрешения адреса блока хранения коэффициентов, входом записи четвертого регистра и входом установки в ноль второго регистра.

Таким образом, сущность заявляемой группы изобретений состоит в создании нового способа цифровой фильтрации и новом построении схемы цифрового рекурсивного полосового фильтра, обеспечивающих реализацию последовательно включенных ступеней фильтрации четвертого порядка, причем каждая ступень фильтрации реализует новое правило, предложенное в заявленном способе, имеет свой набор весовых коэффициентов, хранящихся в блоке хранения коэффициентов, рассчитанных предварительно по формулам, предложенным в заявляемом способе полосовой фильтрации, что обеспечивает более высокую частотную избирательность без снижения быстродействия, а структура фильтра при его реализации требует меньшего оборудования по сравнению с прототипом.

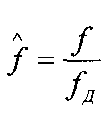

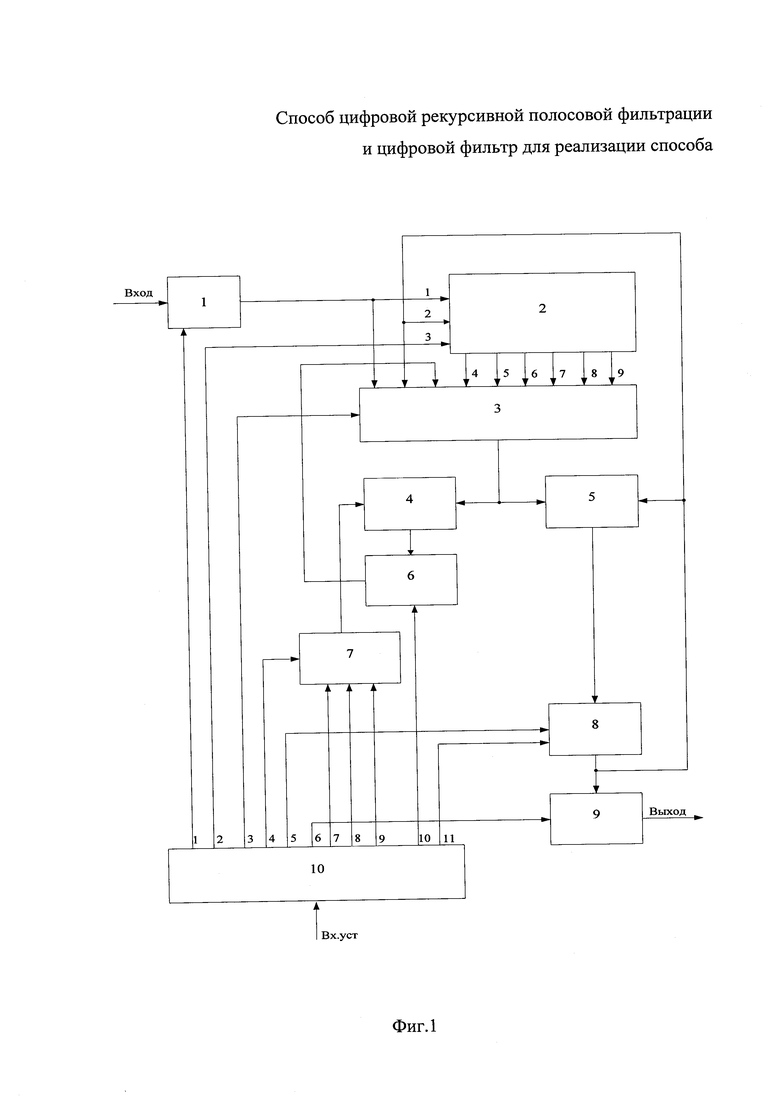

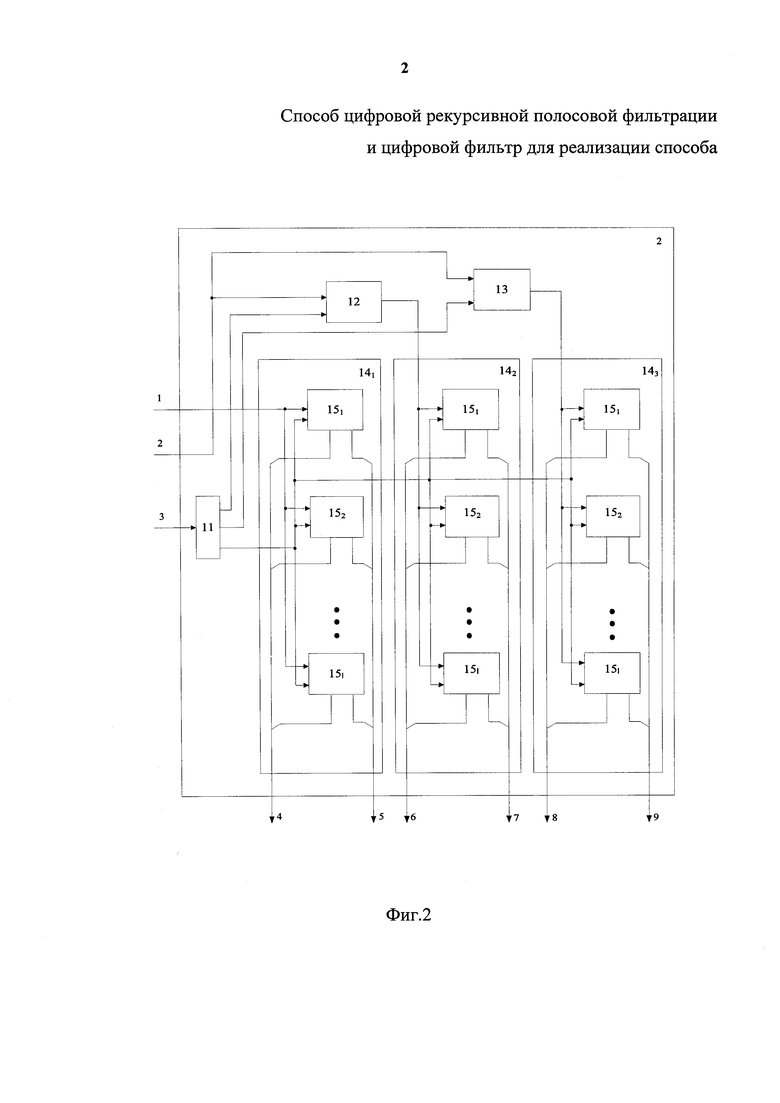

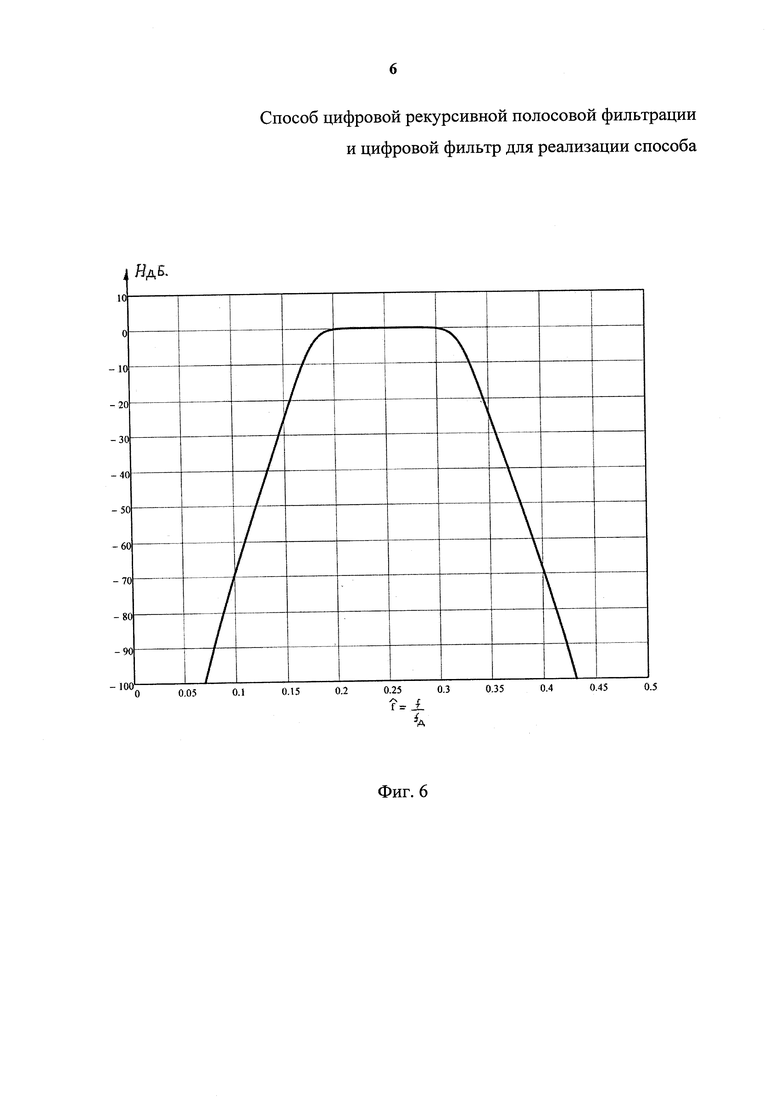

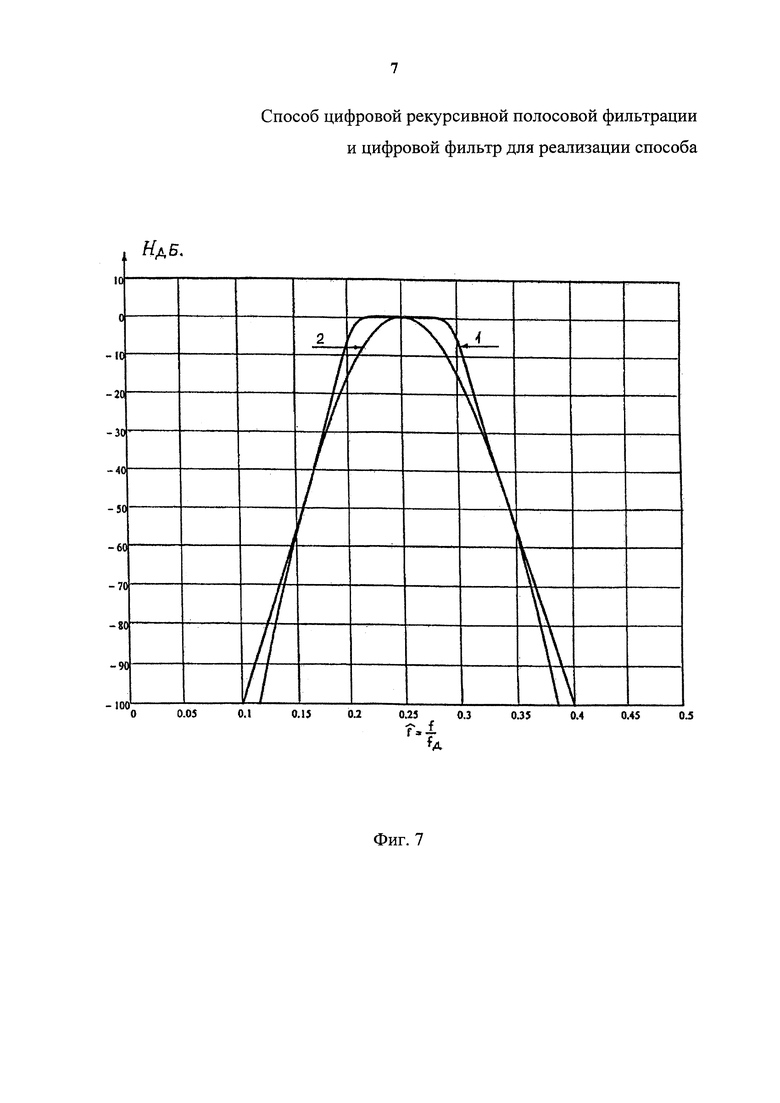

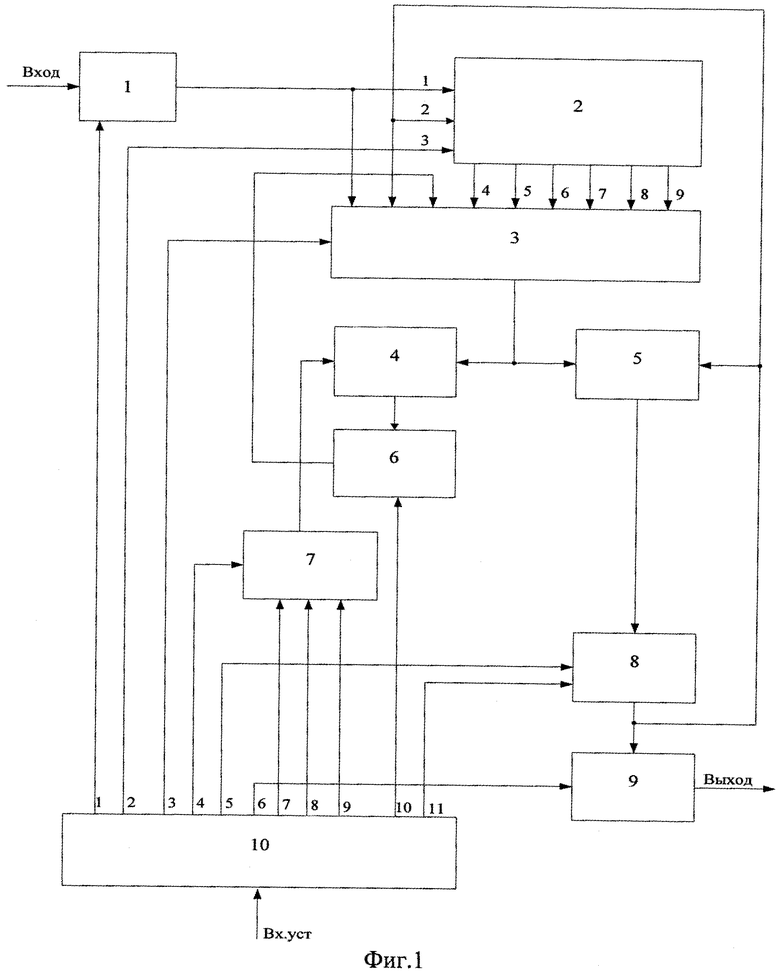

На фиг. 1 представлена структурная схема цифрового рекурсивного полосового фильтра, на фиг. 2 - структурная схема блока хранения выборочных значений сигнала, на фиг. 3 - структурная схема блока управления, на фиг. 4 - временная диаграмма работы цифрового фильтра. На фиг. 5 и фиг. 6 приведены АЧХ заявляемого цифрового фильтра, состоящего из четырех ступеней преобразования для узкой и широкой полос пропускания.

На фиг. 7 приведены примеры АЧХ для предложенного способа при четырех ступенях преобразования фильтруемого сигнала (график 1) и для способа-прототипа при восьми ступенях преобразования (график 2).

На фиг. 1 обозначены:

1, 6, 8, 9 - регистры;

2 - блок хранения выборочных значений сигнала;

3 - мультиплексор;

4 - блок умножения;

5 - сумматор;

7 - блок хранения коэффициентов;

10 - блок управления.

На фиг. 2 обозначены:

11 - демультиплексор;

12, 13 - регистры;

141, 142, 143 - блоки регистров сдвига;

151-15l - регистры сдвига.

На фиг. 3 обозначены:

16 - генератор импульсов;

17 - делитель частоты;

18 - элемент задержки;

19 - контролер интерфейса;

20, 23 - регистры;

21, 25 - счетчики;

22 - постоянное запоминающее устройство (ПЗУ);

24 - блок вычитания;

26 - дешифратор нуля;

27 - элемент ИЛИ.

На фиг. 4 обозначены:

а - сигнал записи/чтения коэффициентов фильтра в блок 7 хранения коэффициентов;

б - последовательность записи/чтения коэффициентов фильтра в блок 7 хранения коэффициентов;

в - последовательность смены адресов в блоке 7 хранения коэффициентов;

г - сигнал разрешения записи коэффициентов в блок 7/из блока 7 хранения коэффициентов;

д - сигнал записи в регистр 1;

е - четырехразрядный (цифровой) сигнал управления мультиплексором 3;

ж - сигнал записи в регистр 8;

з - сигнал записи в регистр 6;

и - сигнал установки в ноль регистра 8;

к - двухразрядный (цифровой) сигнал управления блоком 2 хранения выборочных значений сигнала;

л - сигнал записи в регистр 9.

Цифровой рекурсивный полосовой фильтр (фиг. 1) содержит регистр 1 хранения текущего значения входного сигнала, информационный вход которого является входом фильтра, вход записи подключен к первому выходу блока 10 управления, а выход соединен с первым информационным входом блока 2 хранения выборочных значений сигнала и первым входом мультиплексора 3. Второй вход мультиплексора 3 соединен со вторым информационным входом блока 2 хранения выборочных значений сигнала, вторым входом сумматора 5, выходом регистра 8 и входом регистра 9. Управляющий вход блока 2 хранения выборочных значений сигнала подключен к второму выходу блока 10 управления, третий выход которого соединен с управляющим входом мультиплексора 3.

Первый, второй, третий, четвертый, пятый и шестой выходы блока 2 хранения выборочных значений сигнала соединены соответственно с четвертым, пятым, шестым, седьмым, восьмым и девятым входом мультиплексора 3, третий вход которого подключен к выходу регистра 6.

Выход мультиплексора 3 соединен с первым входом сумматора 5 и вторым входом блока 4 умножения, первый вход которого соединен с выходом блока 7 хранения коэффициентов, а выход - с информационным входом регистра 6. Выход сумматора 5 соединен с информационным входом регистра 8, подключенным входом записи к пятому выходу блока 10 управления. Четвертый выход блока 10 управления соединен с информационным входом блока 7 хранения коэффициентов. Шестой вход блока 10 управления соединен с входом записи регистра 9, выход которого является выходом фильтра. Седьмой, восьмой, девятый, десятый и одиннадцатый выходы блока 10 управления соединены соответственно с входами установки режима запись/чтение, адреса и разрешения адреса блока 7 хранения коэффициентов, входом записи регистра 6 и входом установки в ноль регистра 8. Вход блока 10 управления (Вх. уст.) является входом установки параметров фильтрации.

Блок 2 хранения выборочных значений сигнала (фиг. 2) содержит демультиплексор 11, вход которого является управляющим входом блока 2. Три выхода демультиплексора 11 соединены соответственно с входом записи регистра 12, входом записи регистра 13 и объединенными входами синхронизации регистров 151-15l сдвига, входящими в три группы блоков 141-143 сдвига. Каждый блок 14 сдвига содержит l четырехразрядных регистров сдвига (l - разрядность двоичных чисел при выполнении фильтрации). Информационные входы регистров 151-15l в блоках 141, 142, 143 объединены и подключены соответственно к первому информационному входу блока 2 хранения выборочных значений сигнала и к выходам регистров 12 и 13. Информационные входы регистров 12 и 13 объединены и подключены к второму информационному входу блока 2. Выходы второго и четвертого разрядов регистров 151-15l блоков 141, 142, 143 сдвига образуют попарно соответствующие l - разрядные выходы блоков 141, 142 и 143: (в блоке 141 - выходы 4 и 5, в блоке 142 - выходы 6 и 7, в блоке 143 - выходы 8 и 9).

В блоке 10 управления (фиг. 3) выход генератора 16 импульсов соединен с тактовым входом делителя частоты 17. Вход коэффициента деления делителя 17 частоты соединен с выходом младших разрядов регистра 20. Выход делителя 17 частоты соединен со счетным входом счетчика 21, тактовым входом контроллера интерфейса 19 и через элемент 18 задержки подключен к входу записи регистра 23. Выход счетчика 21 соединен с адресным входом постоянного запоминающего устройства 22, выход которого соединен с информационным входом регистра 23. Выход первого разряда регистра 23 соединен с входом записи регистра 20, второй информационный вход которого подключен к третьему выходу контроллера интерфейса 24. Выходы второго, третьего и четвертого разрядов регистра 23 являются соответственно первым, вторым и третьим выходами блока 10 управления. Первый выход контроллера интерфейса 19 является четвертым выходом блока 10 управления. Второй выход контроллера интерфейса 19, соединенный с входом младшего разряда постоянного запоминающего устройства 22, является седьмым выходом устройства 10 управления. Пятый, шестой, седьмой, восьмой, девятый и десятый выходы регистра 23 являются соответственно пятым, шестым, восьмым, девятым, десятым и одиннадцатым выходами блока 10 управления.

Выход одиннадцатого разряда регистра 23 соединен со счетным входом счетчика 25, вход установки в ноль которого соединен с выходом элемента ИЛИ 27, а выход - с первым входом блока 24 вычитания. Второй вход блока 24 вычитания соединен со вторым выходом регистра 20. Выход блока 24 вычитания подключен через дешифратор нуля 26 к первому входу элемента ИЛИ 29, второй вход которого соединен с выходом двенадцатого разряда регистра 23 и входом установки в ноль счетчика 21.

Вход контроллера интерфейса 19 является входом установки параметров фильтрации блока 10 управления.

Цифровой фильтр реализует заявляемый способ цифровой рекурсивной полосовой фильтрации. В фильтре обеспечено последовательное подключение необходимого числа ступеней преобразования фильтруемого сигнала, обеспечивающего требуемую частотную избирательность. Каждая ступень преобразования в фильтре работает по правилу, определенному разностным уравнением четвертого порядка (5).

Работа цифрового фильтра, реализующего заявляемый способ цифровой рекурсивной полосовой фильтрации, осуществляется следующим образом.

В цифровом фильтре обеспечена возможность задания работы с необходимыми полосой пропускания, центральной частотой полосы пропускания и крутизной скатов АЧХ фильтра. Необходимые для этого параметры содержатся в информационных словах, поступающих на вход установки параметров (Вх. уст) блока 10 управления. В информационных словах содержатся следующие данные:

1. Значения коэффициентов фильтрации Kij, определенных независимо для каждой ступени преобразования фильтруемого сигнала по формулам (4).

2. Число, определяющее количество ступеней фильтрации r. На практике r≤4, что обеспечивает реализацию фильтра до 16 порядка включительно и позволяет получить требуемое высокое значение крутизны скатов АЧХ фильтра.

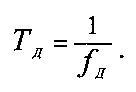

3. Число, определяющее во сколько раз частота дискретизации фильтра меньше максимально возможной - коэффициент деления (КДЕЛ), задающий требуемое значение частоты дискретизации фильтра, которое в четыре раза выше центральной частоты полосы пропускания.

4. Признак режима записи/чтения.

Работа цифрового фильтра состоит из нескольких циклов, выполняемых в каждом периоде частоты дискретизации  Число циклов работы фильтра определяется значением параметра r и равно числу ступеней преобразования фильтруемого сигнала. Временная диаграмма (на фиг. 4), поясняющая последовательность выполнения фильтрации, приведена для фильтра восьмого порядка, для которого r=2. Фильтр восьмого порядка реализуется последовательным включением двух ступеней преобразования соответствии с разностными уравнениями:

Число циклов работы фильтра определяется значением параметра r и равно числу ступеней преобразования фильтруемого сигнала. Временная диаграмма (на фиг. 4), поясняющая последовательность выполнения фильтрации, приведена для фильтра восьмого порядка, для которого r=2. Фильтр восьмого порядка реализуется последовательным включением двух ступеней преобразования соответствии с разностными уравнениями:

где xn2=yn1 - значение входного сигнала второй ступени фильтрации, равное значению выходного сигнала первой ступени.

Работа фильтра проводится под управлением блока 10 управления, формирующего управляющие сигналы, представленные на фиг. 4. Принцип формирования сигналов управления следующий.

Импульсы, генерируемые генератором импульсов 16, поступают через делитель частоты 17 в счетчик 21. Число на выходе счетчика 21 является адресом постоянного запоминающего устройства 22. Число разрядов постоянного запоминающего устройства 22 зависит от числа формируемых сигналов управления, а количество ячеек определяется минимальным интервалом между формируемыми импульсами. В ячейках постоянного запоминающего устройства записаны сигналы логической единицы в тех разрядах, для которых соответствующее значение сигнала управления принимает высокий уровень. В остальных разрядах ячеек записаны сигналы логического нуля. Содержимое ячеек постоянного запоминающего устройства 22 последовательно записывается в регистр 23 сигналом, поступающим с делителя частоты 17, задержанным элементом 18 задержки. После записи содержимого последней ячейки в регистр 23 на выходе его последнего разряда появляется сигнал логической единицы, которым производится установка счетчика 21 в исходное состояние, после чего процесс формирования управляющих сигналов повторяется.

Перед началом фильтрации выполняется запись параметров фильтра.

Последовательность записи параметров фильтрации представлена в левой части временной диаграммы (фиг. 4).

Управление записью производится контроллером интерфейса 19 блока 10 управления. Для установки режима записи параметров в контроллер интерфейса 19 записывается признак записи - сигнал логического нуля (сигнал а на фиг. 4).

Параметры фильтра r, КДЕЛ записываются в регистр 20 блока управления. Коэффициенты фильтрации записываются в блок 7 хранения коэффициентов в определенной последовательности (сигнал 6 на фиг. 4). При записи коэффициенты фильтра поступают на вход блока 7 хранения коэффициентов с четвертого выхода блока 10 управления. При этом формируются: сигнал записи с седьмого выхода блока 10 управления (сигнал а на фиг. 4), адреса (с нулевого по седьмой), по которым записываются коэффициенты - с восьмого выхода блока 10 (сигнал в на фиг. 4), а сигнал разрешения записи - с девятого выхода блока 10 (сигнал г на фиг. 4).

Чтобы обеспечить формирование только тех управляющих сигналов, которые нужны в режиме записи, сигнал логического нуля подается на вход младшего разряда адреса постоянного запоминающего устройства 22, обеспечивая запрет выдачи на выход блока 10 управления сигналов, которые не используются в режиме записи. После окончания записи параметров фильтрации контроллер интерфейса 19 блока 10 памяти устанавливает на седьмом выходе блока 10 режим чтение (сигнал логической единицы) (сигнал а на фиг. 4). Фильтр готов к приему фильтруемого сигнала. Начинается циклическая работа фильтра в соответствии с разностными уравнениями (6).

Значение входного сигнала xn1 поступает с входа фильтра и записывается в регистр 1 сигналом с первого выхода блока 10 управления (сигнал д на фиг. 4). Одновременно производится обнуление регистра 8 сигналом установки нуля, поступающим с одиннадцатого выхода блока 10 управления (сигнал и на фиг. 4). На управляющем входе мультиплексора 3 устанавливается число 1, поступающее с третьего выхода блока 10 управления, обеспечивающее поступление входного сигнала xn1 с выхода регистра 1 на выход мультиплексора 3 и вход сумматора 5 (сигнал е на фиг. 4). Значение входного сигнала xn1 складывается в сумматоре 5 с нулевым значением, поступающим с регистра 8, и записывается в регистр 8 по сигналу записи, поступающему с пятого выхода блока 10 управления (сигнал ж на фиг. 4). С седьмого выхода блока 10 управления поступает нулевой адрес в блок 7 хранения коэффициентов (сигнал в на фиг. 4). Все время фильтрации блок 7 хранения находится в режиме чтения (сигнал а на фиг. 4). Одновременно производится чтение из блока 7 хранения коэффициентов числа - 2, хранящегося по нулевому адресу (сигнал б на фиг. 4) и поступление значения сигнала xn-2,1 из блока 2 хранения выборочных значений сигнала, хранящегося в регистрах сдвига 151-15l блока 141 регистров сдвига. При этом открыто четвертое направление мультиплексора 3 сигналом управления, поступающим с третьего выхода блока 10 управления на управляющий вход мультиплексора (е на фиг. 4). На входах блока умножения 6 появляются значения -2 и xn-2,1. Образующееся произведение -2xn-2,1, записывается в регистр 6 сигналом записи, поступающим с десятого выхода блока 10 управления. Мультиплексор 3 открывается на третье направление, для чего на его управляющий вход поступает число 3 с третьего выхода блока 10 управления. Число -2xn-2,1 поступает с выхода регистра 6 на вход сумматора 5, на втором входе которого действует значение входного сигнала xn1, хранящееся в регистре 8. На выходе сумматора 5 образуется число xn1-2xn-2,1, которое записывается в регистр 8 сигналом записи, поступающим с пятого выхода блока 10 управления (сигнал ж на фиг. 4). Значение входного сигнала xn-4,1, хранящееся в регистрах сдвига 151-15l блока 141 регистров сдвига поступает с пятого выхода блока 2 хранения выборочных значений сигнала через пятый вход мультиплексора 3, на управляющем входе которого установлено число 5, поступающее с третьего выхода блока 10 управления (сигнал е на фиг. 4), на вход сумматора 5. На другом входе сумматора 5 действует значение xn1-2xn-2,1, поступающее с выхода регистра 8 так, что на выходе сумматора 5 образуется число xn1-2xn-2,1+xn-4,1, которое записывается в регистр 8 сигналом записи, поступающим с пятого выхода блока 10 управления (сигнал ж на фиг. 4). На управляющем входе мультиплексора 3 устанавливается число 2 (сигнал е на фиг. 4). Записанное в регистре 8 число xn1-2xn-2,1+xn-4,1, поступает на вход блока 4 умножения, на другой вход которого поступает значение коэффициента К01 из блока 7 хранения коэффициентов фильтра. При этом на входах блока 7 действуют следующие сигналы: на адресном входе адрес 1 (сигнал в на фиг. 4), сигнал чтения - на входе установки режима записи/чтения (сигнал а на фиг. 4) и сигнал логического приема на входе разрешения записи коэффициентов (сигнал г на фиг. 4). Указанные сигналы поступают на соответствующие входы блока 7 хранения коэффициентов с седьмого, восьмого и девятого выходов блока 10 управления, обеспечивая режим чтения коэффициента К01. На выходе блока 4 умножения оказывается сформированным значение сигнала К01(xn1-2xn-2,1+xn-4,1), которое записывается в регистр 6 сигналом, поступающим с десятого выхода блока 10 управления. Выполняется установка в ноль регистра 8 сигналом, поступающим с одиннадцатого выхода блока 10 управления (сигнал и на фиг. 4). Устанавливается число 3 на управляющем входе мультиплексора 3 (сигнал е на фиг. 4), поступающее с третьего выхода блока 10 управления. Значение сигнала, хранящееся в регистре 6, поступает через мультиплексор 3 на вход сумматора, на другом входе которого действует сигнал логического нуля, поступающий с выхода регистра 8. Значение сигнала Κ01(xn1-2xn-2,1+xn-4,1) записывается в регистр 8 сигналом, поступающим с пятого выхода блока 10 управления (сигнал ж на фиг. 4). На управляющем входе мультиплексора 3 устанавливается число 6, поступающее с третьего выхода блока 10 управления (сигнал е на фиг. 4).

Значение сигнала yn-2,1, хранящееся в регистрах сдвига 151-15l блока 142 регистров сдвига, поступает с шестого выхода блока 2 хранения выборочных значений сигнала на вход блока 4 умножения. На другой вход блока 4 умножения поступает значение коэффициента - К11 (сигнал б на фиг. 4). При этом в блоке 7 хранения коэффициентов, устанавливается адрес 2 (в на фиг. 4), поступающий с восьмого выхода блока 10 управления. Значение сигнала - K11xn-2,1 с выхода блока 4 умножения записывается в регистр 6 по сигналу, поступающему с десятого выхода блока 10 управления. На управляющем входе мультиплексора 3 устанавливается число 3 по сигналу, поступающему с третьего выхода блока 10 управления (сигнал е на фиг. 4).

Значение сигнала -K11yn-2,1 с выхода регистра 6 поступает на вход сумматора 5, на другом входе которого действует значение сигнала K01(xn1-2xn-2,1+xn-4,1), поступающее с выхода регистра 8. Образовавшееся значение сигнала К01(xn1-2xn-2,1+xn-4,1)-K11yn-2,1 записывается в регистр 8 по сигналу, поступающему на вход записи с пятого выхода блока 10 управления (сигнал ж на фиг. 4). На управляющем входе мультиплексора 3 устанавливается число 7 по сигналу, поступающему с третьего выхода блока 10 управления (сигнал е на фиг. 4).

Значение сигнала yn-4,1, хранящееся в регистрах сдвига 151-15l блока 142 регистров сдвига, поступает с седьмого выхода блока 2 хранения выборочных значений сигнала на вход блока 4 умножения. На другой вход блока 4 умножения поступает значение коэффициента - К21 (сигнал 6 на фиг. 4). При этом в блоке 7 хранения коэффициентов устанавливается адрес 3 (сигнал в на фиг. 4), поступающий с восьмого выхода блока 10 управления. Значение сигнала - K21yn-4,1 с выхода блока 4 умножения записывается в регистр 6 по сигналу, поступающему с десятого входа блока 10 управления. На управляющем входе мультиплексора 3 устанавливается число 3 по сигналу, поступающему с третьего выхода блока 10 управления (сигнал е на фиг. 4).

Значение сигнала -K21yn-4,1 с выхода регистра 6 поступает на вход сумматора 5, на другом входе которого действует значение К01(xn1-2xn-2,1+xn-4,1)-K11yn-2,1, поступающее с выхода регистра 8.

Образовавшееся значение сигнала yn1=K01(xn1-2xn-2,1+xn-4,1)-K11yn-2,1-K21yn-4,1, являющееся результатом фильтрации первой ступени преобразования, записывается в регистр 8 по сигналу, поступающему с пятого выхода блока 10 управления.

На управляющий вход блока 2 хранения выборочных значений сигнала, являющийся входом демультиплексора 11, со второго выхода блока 10 управления поступает число 1 (сигнал к на фиг. 4). На первом входе демультиплексора 11 появляется сигнал логической единицы, по которому сформированный сигнал yn1, поступающей с выхода регистра 8 на второй информационный вход блока 2 хранения выборочных значений сигнала, записывается в регистр 12 блока 2. На этом первый цикл работы фильтра заканчивается.

На втором цикле работа фильтра данного периода дискретизации происходит аналогично.

При этом входным сигналом второй ступени преобразования является выходной сигнал первой ступени yn1, уже хранящийся в регистре 8, поэтому работа второй ступени преобразования начинается с формирования произведения -2xn-2,2=-2yn-2,1 в блоке 4 умножения. Затем в сумматоре 5 формируется сигнал xn2-2xn-2,2=yn1-2yn-2,1 и так далее. При этом управление мультиплексором 3 производится, как показано на фиг. 4е, а последовательность смены адресов блока 7 хранения коэффициентов и чтения коэффициентов - как показано на фиг. 4б и фиг. 4в.

В конце второго цикла работы фильтра последовательно формируются числа 2 и 3 на управляющем входе блока 2 хранения выборочных значений сигнала (сигнал к на фиг. 4), по которым сначала производится запись отфильтрованного сигнала yn2 в регистр 13, а затем одновременный ввод сигналов xn1, yn1 и yn2 в соответствующие регистры 151-15l блоков 141, 142, 143 регистров сдвига по сигналу, формируемому на третьем выходе мультиплексора 11.

При переходе от цикла к циклу в счетчике 25 блока 10 управления добавляется единица по сигналу, поступающему с выхода регистра 23. В последнем цикле число в счетчике 25 становится равным r. На выходе блока 24 вычитания формируется число, равное нулю, означающее, что данный цикл последний. На выходе дешифратора нуля 26 формируется сигнал, который через элемент 27 ИЛИ устанавливает счетчик 25 в нулевое состояние.

В конце второго цикла отфильтрованный сигнал из регистра 8 записывается сигналом, поступающим с шестого выхода блока 10 управления (сигнал л на фиг. 4), в регистр 9, выход которого является выходом цифрового фильтра.

В последующих периодах частоты дискретизации работа фильтра происходит аналогично.

По сравнению с известными техническими решениями предложенный способ и цифровой фильтр для реализации этого способа обеспечивают повышение избирательности цифровой полосовой фильтрации без снижения быстродействия, при этом цифровой фильтр оказывается проще в реализации.

В отличие от известного способа-прототипа преобразование сигнала в i-й ступени формируют по новому правилу (5), в котором весовые коэффициенты фильтрации принимают новые значения в каждой из ступеней в соответствии с формулами (4). В результате предлагаемый способ цифровой фильтрации при одинаковом с прототипом числе ступеней преобразования обеспечивает более высокую частотную избирательность без снижения быстродействия. Эффективность предлагаемого способа особенно велика при выполнении фильтрации сигнала в узкой полосе частот.

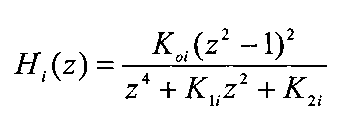

Действительно, в предлагаемом способе и фильтре для его реализации преобразованию сигнала (5) при выполнении фильтрации соответствует передаточная функция, получаемая путем применения z-преобразования к (5):

где  - передаточная функция i-й ступени преобразования сигнала.

- передаточная функция i-й ступени преобразования сигнала.

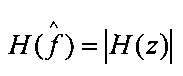

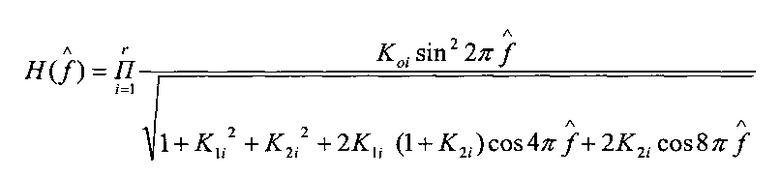

АЧХ цифрового фильтра с такой передаточной функцией, определяемая как  при z=ei2πf, представляется следующим выражением:

при z=ei2πf, представляется следующим выражением:

где  - нормированная частота;

- нормированная частота;

f - частота сигнала;

fД=4fц - частота дискретизации;

fц - центральная частота полосы пропускания;

Koi - коэффициент нормировки i-й ступени преобразования;

K1i, K2i - коэффициенты i-й ступени преобразования, определяющие значения полосы пропускания и центральной частоты полосы пропускания, вычисляются по формулам (4).

На фиг. 7 приведены примеры АЧХ для предложенного способа при четырех ступенях преобразования фильтруемого сигнала (график 1) и для способа-прототипа при восьми ступенях преобразования (график 2) с примерно одинаковыми значениями крутизны спада АЧХ.

Из сравнения АХЧ на фиг. 7 следует, что предложенный способ фильтрации позволяет существенно повысить частотную избирательность при одинаковом числе ступеней преобразования без снижения быстродействия.

Таким образом, предлагаемый способ при одинаковом с прототипом числе ступеней преобразования позволяет обеспечить более высокую частотную избирательность полосовой фильтрации без снижения быстродействия выполнения фильтрации сигнала. Кроме того, при необходимости выполнения узкополосной фильтрации для обеспечения требуемой частотной избирательности в предлагаемом способе требуется вдвое меньшее число ступеней преобразования, чем в способе-прототипе.

При этом структура фильтра, реализующего новый способ фильтрации, требует меньшего оборудования по сравнению с прототипом.

Цифровой фильтр для реализации предложенного способа выполняется на стандартной элементной базе для вычислительной техники, выпускаемой серийно отечественной промышленностью.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ЦИФРОВОЙ РЕКУРСИВНОЙ ПОЛОСОВОЙ ФИЛЬТРАЦИИ И ЦИФРОВОЙ ФИЛЬТР ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 2011 |

|

RU2460130C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| Рекурсивный цифровой фильтр | 1990 |

|

SU1732433A1 |

| Программно-управляемый цифровой фильтр | 1979 |

|

SU877787A1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| Адаптивный цифровой фильтр | 1982 |

|

SU1080245A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Программируемый цифровой фильтр | 1986 |

|

SU1374244A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки информации с высокими требованиями к частотной избирательности выполнения фильтрации. Техническим результатом является повышение частотной избирательности полосовой фильтрации без снижения быстродействия. Устройство содержит блок умножения, сумматор, блок хранения выборочных значений сигнала, блок хранения коэффициентов, мультиплексор, четыре регистра, блок управления. 7 ил.

Цифровой рекурсивный полосовой фильтр, содержащий блок умножения, сумматор, блок хранения выборочных значений сигнала, блок хранения коэффициентов, мультиплексор, три регистра и блок управления, вход которого является входом установки параметров фильтрации, а первый, второй и третий выходы соединены соответственно с входом записи первого регистра, управляющим входом блока хранения выборочных значений сигнала и управляющим входом мультиплексора, вход первого регистра является информационным входом фильтра, а выход соединен с первым входом мультиплексора, второй вход которого соединен с выходом второго регистра и информационным входом третьего регистра, четвертый выход блока управления соединен с информационным входом блока хранения коэффициентов, выход которого соединен с первым входом блока умножения, пятый выход блока управления соединен с входом записи второго регистра, подключенного информационным входом к выходу сумматора, шестой выход блока управления соединен с входом записи третьего регистра, выход которого является выходом фильтра, отличающийся тем, что в него введен четвертый регистр, соединенный информационным входом с выходом блока умножения, а выходом - с третьим входом мультиплексора, первый вход которого соединен с первым информационным входом блока хранения выборочных значений сигнала, выход мультиплексора соединен со вторым входом блока умножения и первым входом сумматора, второй вход которого соединен с выходом второго регистра и вторым информационным входом блока хранения выборочных значений сигнала, первый, второй, третий, четвертый, пятый и шестой выходы блока хранения выборочных значений сигнала соединены соответственно с четвертым, пятым, шестым, седьмым, восьмым и девятым входами мультиплексора, седьмой, восьмой, девятый, десятый и одиннадцатый выходы блока управления соединены соответственно с входами установки режима записи/чтения, адреса, разрешения адреса блока хранения коэффициентов, входом записи четвертого регистра и входом установки в ноль второго регистра.

| СПОСОБ ЦИФРОВОЙ РЕКУРСИВНОЙ ПОЛОСОВОЙ ФИЛЬТРАЦИИ И ЦИФРОВОЙ ФИЛЬТР ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 2011 |

|

RU2460130C1 |

| Цифровой рекурсивный полосовой фильтр | 1984 |

|

SU1224980A1 |

| US 4317092 A, 23.02.1982 | |||

| US 4356559 A, 26.10.1982 | |||

| US 4521866 A, 04.06.1985. | |||

Авторы

Даты

2016-04-10—Публикация

2014-08-06—Подача