fj

О5

1

о о

О1

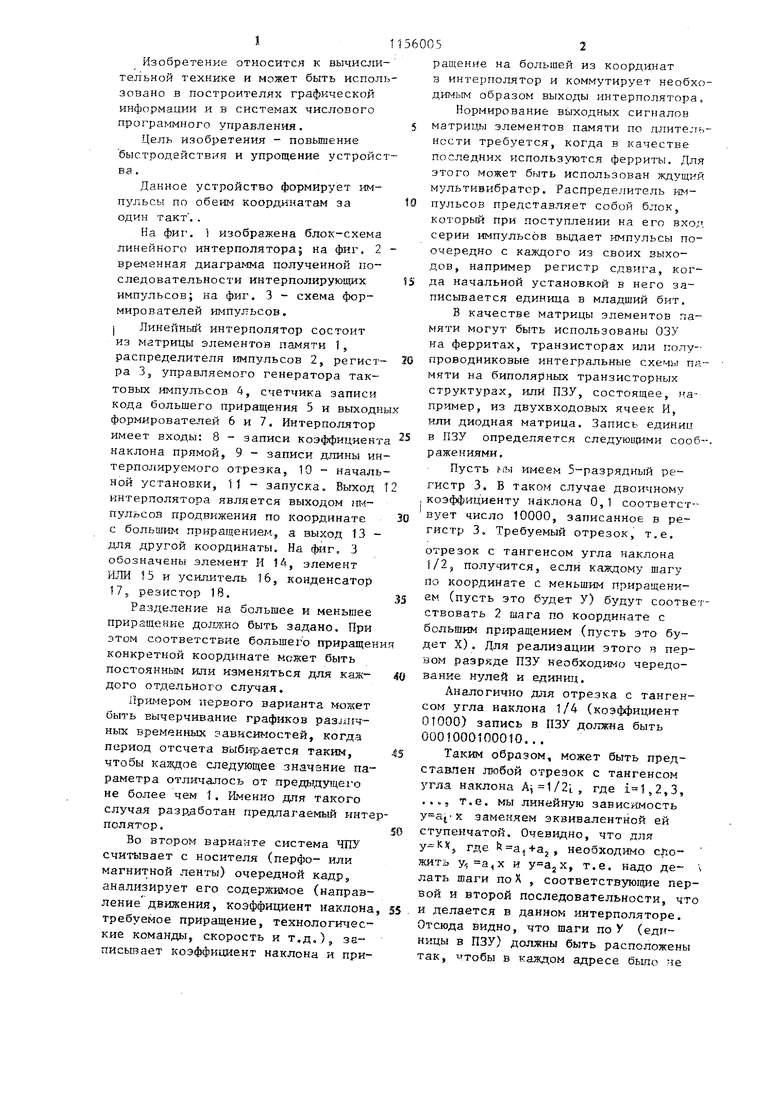

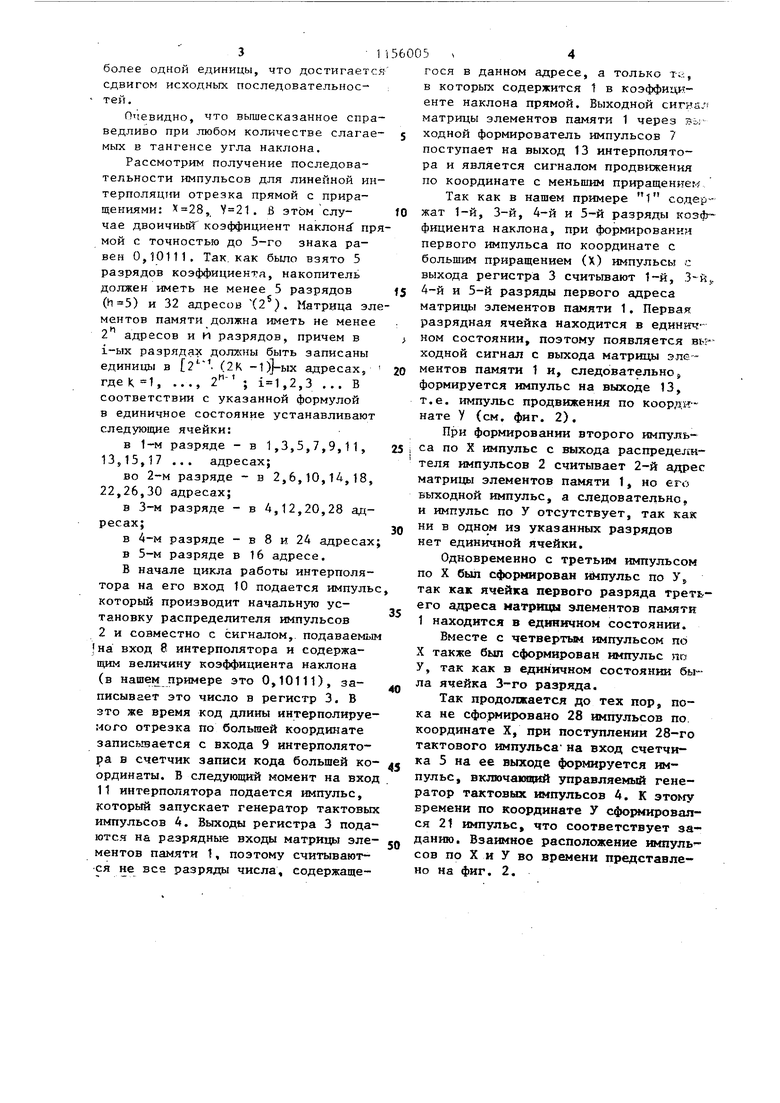

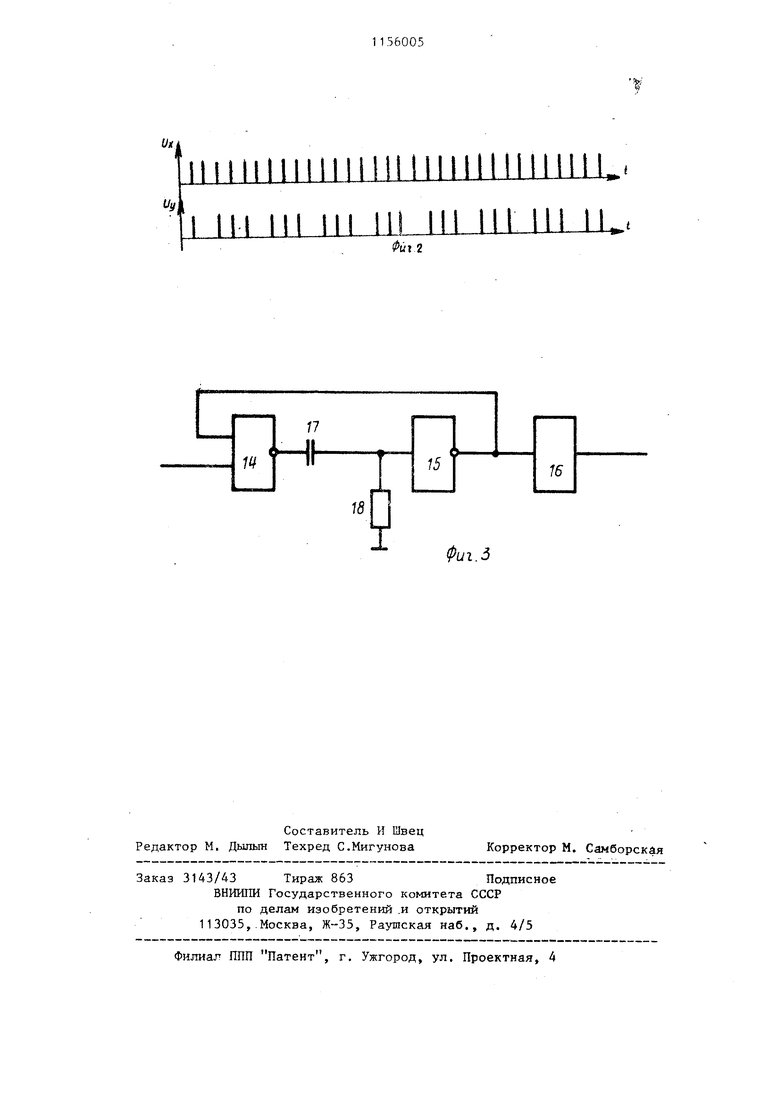

Фиг Изобретение относится к вычислительной технике и может быть испол зовано в построителях графической информации и в системах числового программного управления. Цель изобретения - повышение быстродействия и упрощение устройс ва , Данное устройство формирует импульсы по обеим координатам за один такт . . , I изображена блок-схема На фиг линейного интерполятора; на фиг, 2 временная диаграмма полученной последовательности интерполирующих импульсов; на фиг. 3 - схема формирователей импульсов. I Линейный интерполятор состоит из матрицы элементов памяти 1, распределителя импульсов 2, регист ра 3j управляемого генератора тактовых импульсов 4, счетчика записи кода большего приращения 5 и выходн формирователей 6 и 7, Интерполятор имеет входы: 8 - записи коэффициент наклона прямой, 9 записи длины ин TepnoJiHpyeMoro отрезка, 10 - началь ной установки, 11 - . Выход интерполятора является выходом гшпульсов продвижения по координате с больши 1 приращением, а выход 13 для другой координаты. На . 3 обозначены элемент И 14, элемент ИЛИ 15 и усилитель 16, конденсатор 17, резистор 18. Разделение на большее и меньшее приращение должно быть задано. При этом соответствие большего приращен конкретной координате может быть постоянным или изменяться для каждого отдельного случая. Примером первого варианта может быть вычерчивание графиков pa3Jii{4ных временных зависимостей, когда период отсчета выбирается таким, чтобы каждое следующее значание параметра отличалось от предыдущего не более чем 1. Именно для такого случая разработан предлагаемый инте полятор. Во втором варианте система ЧПУ считывает с носителя (перфо- или магнитной ленты) очередной кадр, анализирует его содержимое (направление движения, коэффициент наклона требуемое приращение, технологические команды, скорость и т.д.) записывает коэффициент наклона и при52 на большей из координат 3 интерполятор и коммутирует необходимым образом выходы интерполятора. Нормирование выходных сигналов матрицы элементов памяти по длите;1ьности требуется, когда в качестве последних используются ферриты. Для этого Может быть использован ждущий мультивибратор. Распределитель импульсов представляет собой блок, который при поступлении на его вхо; серии импульсов выдает импульсы поочередно с каждого из своих выходов, например регистр сдвига, когда начальной установкой в него записьгеается единица в младший бит. В качестве матрицы элементов памяти могут быть использованы ОЗУ на ферритах, транзисторах или полупроводниковые интегральные схемы памяти на биполяр1ных транзисторных структурах, или ПЗУ, состоящее, например, из двухвходовых ячеек И, или диодная матрица. Запись единиц в ПЗУ определяется следующими сооб--. ражениями. Пусть иь имеем 5-разрядный регистр 3. Б таком случае двоичному коэффициенту наклона О,1 соответствует число 10000, записанное в регистр 3. Требуемый отрезок, т.е. отрезок с тангенсом угла наклона 1/2, получится, если каждому шагу по координате с меньшим приращением (пусть это будет У) будут соответствовать 2 шага по координате с большим лр1фащением .(пусть это будет X). Для реализации этого в первом разряде ПЗУ необходимо чередование нулей и единшд. Аналогично для отрезка с тангенсом угла наклона 1/4 (коэффициент 01000) запись в ПЗУ должна быть 0001000100010,.. Таким образом, может быть представлен любой отрезок с тангенсом угла наклона , где ,2,3, .,„, т.е. мы линейную зависимость заменяем эквивалентной ей ступенчатой. Очевидно, что для где , необходимо сЛожить у, а,х и , т.е. надо де- лать шаги по X , соответствующие первой и второй последовательности, что и делается в данном интерполяторе. Отсюда видно, что шаги по У (единицы в ПЗУ) должны быть расположены так, ггтобы в каждом адресе было не 3 1 более одной единицы, что достигаетс сдвигом исходных последовательностей. Очевидно, что вышесказанное спра ведливо при любом количестве слагае мых в тангенсе угла наклона. Рассмотрим получение последовательности импульсов для линейной ин терполяции отрезка прямой с приращениями: , . В этом случае двоичныйГ коэффициент наклон пр мой с точностью до 5-го знака равен 0,10111, Так. как было взято 5 разрядов коэффициента, накопитель должен иметь не менее 5 разрядов (И 5) и 32 адресов (2 ). Матрица эл ментов памяти должна иметь не менее 2 адресов и п разрядов, причем в i-ых разрядах долхгаы быть записаны единицы в . (2К -1)-ых адресах, где К 1, ,,,. ; ,2,3 ,,. В соответствии с указанной формулой в единичное состояние устанавливают следующие ячейки: в 1-м разряде - в 1,3,5,7,9,11, 13,15,17 .,. адресах; во 2-м разряде - в 2,6,10,1А,18, 22,26,30 адресах; в 3-м разряде - в 4,12,20,28 адресах;в 4-м разряде - в 8 и 24 адресах в 5-м разряде в 16 адресе, В начале цикла работы интерполятора на его вход 10 подается импуль который производит начальную установку распределителя импульсов 2 и совместно с сигналом, подаваемы на вход 8 интерполятора и содержащим величину коэффициента наклона (в нашем примере это 0,10111), записывает это число в регистр 3, В это же время код длины интерполируе мого отрезка по большей координате записьшается с входа 9 интерполятора в счетчик записи кода большей ко ординаты. В следующий момент на вхо 11 интерполятора подается импульс, который запускает генератор тактовы импульсов 4. Выходы регистра 3 пода ются на разрядные входы матрицы эле ментов памяти 1, поэтому считываются не все разряды числа, содержаще5 4 гося в данном адресе, а только та, в которых содержится 1 в коэффициенте наклона прямой. Выходной сигнал матрицы элементов памяти 1 через зы ходной формирователь импульсов 7 поступает на выход 13 интерполятора и является сигналом продвижения по координате с меньшим приращением Так как в нашем примере 1 содержат 1-й, 3-й, 4-й и 5-й разряды коэффициента наклона, при формирования первого импульса по координате с большим приращением (Х) импульсы с выхода регистра 3 считьшают 1-й, З-й. -й и 5-й разряды первого адреса матрицы элементов памяти 1. Первая разрядная ячейка находится в единитеном состоянии, поэтому появляется вь ходной сигнал с выхода матрицы эле-ментов памяти 1 и, следовательно, формируется импульс на выходе 13, т,е, импульс продвижения по координате У (см, фиг. 2), При формировании второго импульса по X импульс с выхода распределителя импульсов 2 считывает 2-й адрес матрицы элементов памяти 1, но его выходной импульс, а следовательно, и импульс по У отсутствует, так как ни в одном из указанных разрядов нет единичной ячейки. Одновременно с третьим импульсом по X был сформирован импульс по % так как ячейка первого разряда третьего а,цреса матрицы элементов памяти 1 находится в единичном состоянии. Вместе с четвертым импульсом по X также бып сформирован импульс по У, так как в единичном состоянии была ячейка разряда. Так продолжается до тех пор, пока не сформировано 28 импульсов по. координате X, при поступлении 28-го тактового импульса на вход счетчика 5 на ее выходе формируется импульс, включающий управляемый генератор тактовых импульсов 4. К этому времени по координате У сформировался 21 импульс, что соответствует заДанию. Взаимное расположение импульсов по X и У во времени представлено на фиг. 2.

Ux

JlLUiJililiilllUlllllllllllllL

Uy

I III III III II iiLLLLilLll

Фи.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1989 |

|

SU1659986A1 |

| Генератор векторов для системы отображения графической информации | 1974 |

|

SU525980A1 |

| Линейный интерполятор | 1985 |

|

SU1298714A1 |

| Генератор символов | 1987 |

|

SU1550572A1 |

| Устройство поворота изображения на экране телевизионного приемника | 1989 |

|

SU1755298A1 |

| Программное задающее устройство | 1981 |

|

SU991376A1 |

| Линейный интерполятор | 1979 |

|

SU888073A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Устройство для двухкоординатного управления рабочим органом | 1990 |

|

SU1815620A1 |

| Устройство для отображения графической информации на газоразрядной индикаторной панели | 1982 |

|

SU1108488A1 |

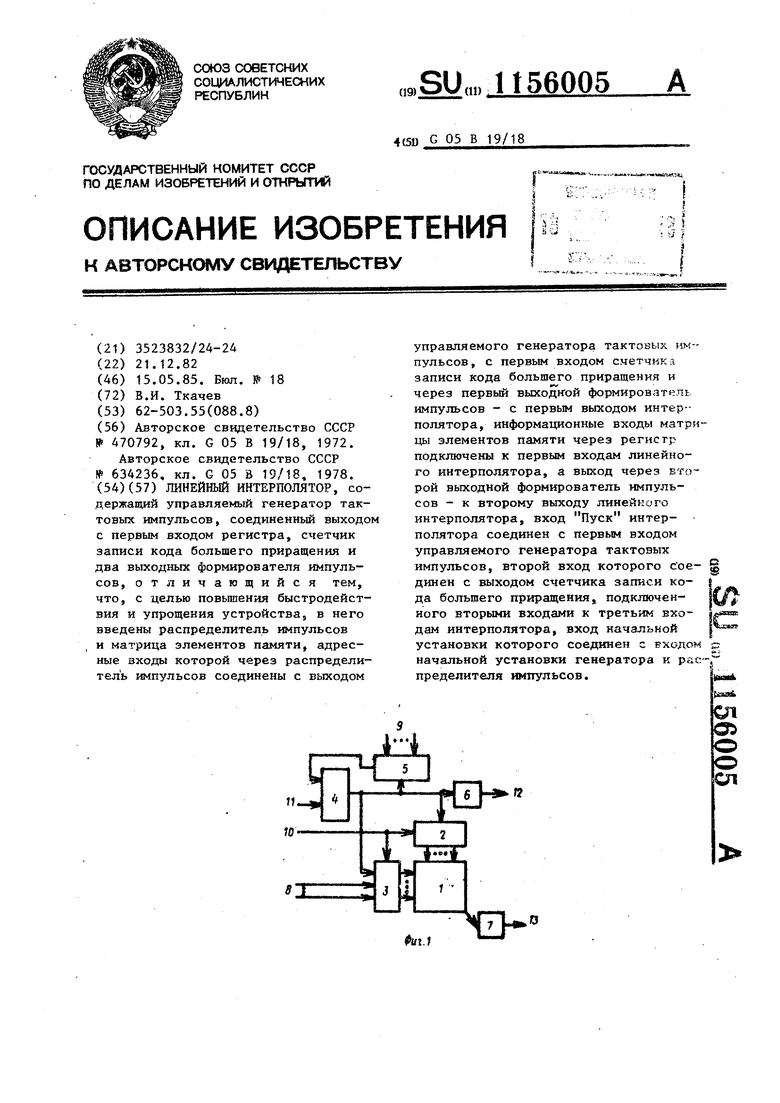

ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР, содержащий управляемый генератор тактовых импульсов, соединенный выходом с первым входом регистра, счетчик записи кода большего приращения и два выходных формирователя импульсов, отличающийся тем, что, с целью повьшения быстродействия и упрощения устройстваа в него введены распределитель импульсов и матрица элементов памяти, адресные входы которой через распределитель импульсов соединены с выходом управляемого генератора тактовых нкпульсов, с первым входом сметчика записи кода большего приращения и через первый выходкой формирователь импульсов - с первым выходом интерполятора, информационные входы матрицы элементов памяти через регистр подключены к первым входам линейного интерполятора, а выход через второй выходной формирователь импульсов - к второму выходу линейного интерполятора, вход Пуск интерполятора соединен с первым входом управляемого генератора тактовых i импульсов, второй вход которого Соединен с выходом счетчика записи кода большего приращения, подключенJ 1г™ ного вторыми входами к третьим вхо1% «, дам интерполятора, вход начальной установки которого соединен с входом начальной установки генератора и рас5-. пределителя импульсов.

Фиг.5

| Линейный интерполятор | 1971 |

|

SU470792A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Линейный интерполятор | 1975 |

|

SU634236A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-05-15—Публикация

1982-12-21—Подача