31СЧ

Адрес | | C5poc

бык

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Синтезатор речевых сигналов | 1979 |

|

SU777674A1 |

| Тон-генератор | 1990 |

|

SU1774373A1 |

| Устройство для умножения | 1984 |

|

SU1233136A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| Цифровой фильтр | 1984 |

|

SU1218454A1 |

| СИСТЕМА ПАССИВНОЙ ЛОКАЦИИ ДВИЖУЩЕГОСЯ ОБЪЕКТА | 1991 |

|

RU2050557C1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1552381A1 |

Изобретение относится к радиотехнике и может быть использовано для повышения разборчивости зашумленного речевого сигнала. Целью изобретения является повышение помехоустойчтвости речевого сигнала путем улучшения отношения сигнал/шум. Устройство содержит оперативный запоминающий блок 1, постоянный запоминающий блок 2, перемножитель 3, сумматор 4, блок 5 вычисления функции, буферные регистры 6 - 13, мультиплексоры 14 - 17, блок 18 управления. Устройство позволяет обеспечить подавление шумов, непрерывных во времени и находящихся в спектре принимаемого речевого сигнала. 2 ил.

v

ё

О О О

со

00

Изобретение относится к радиотехнике и может быть использовано для повышения разборчивости зашумленного речевого сигнала.

Целью изобретения является повышение помехоустойчивости речевого сигнала путем улучшения отношения сигнал/шум.

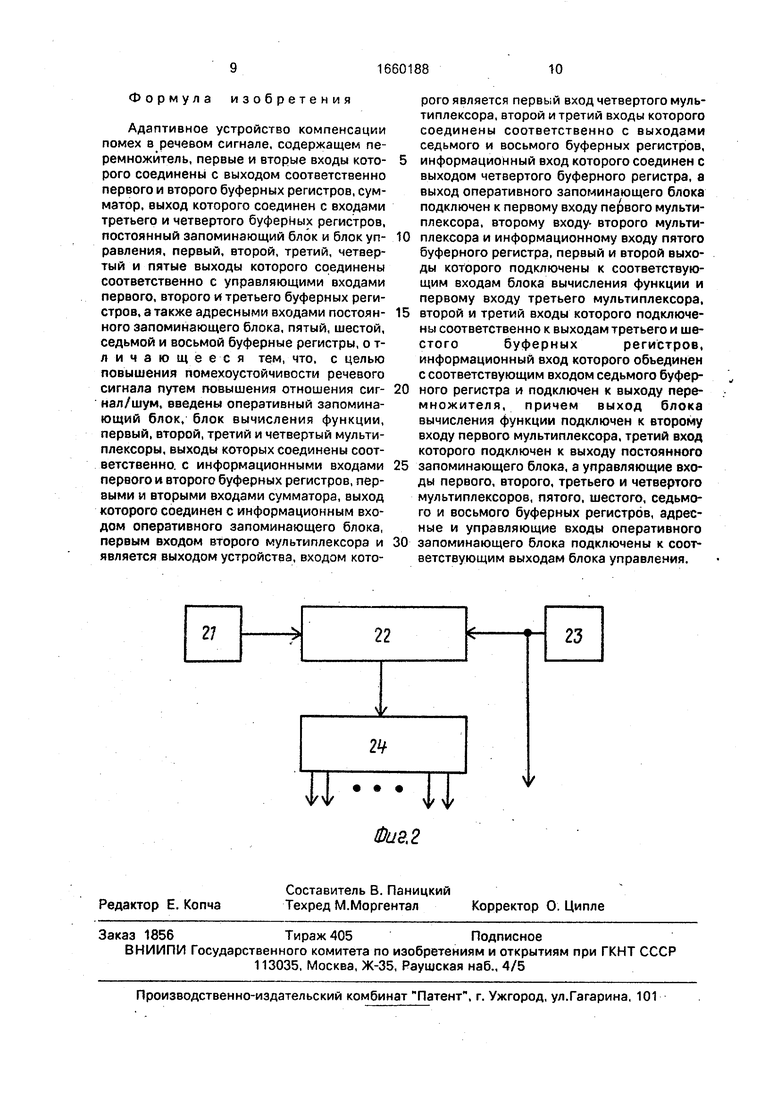

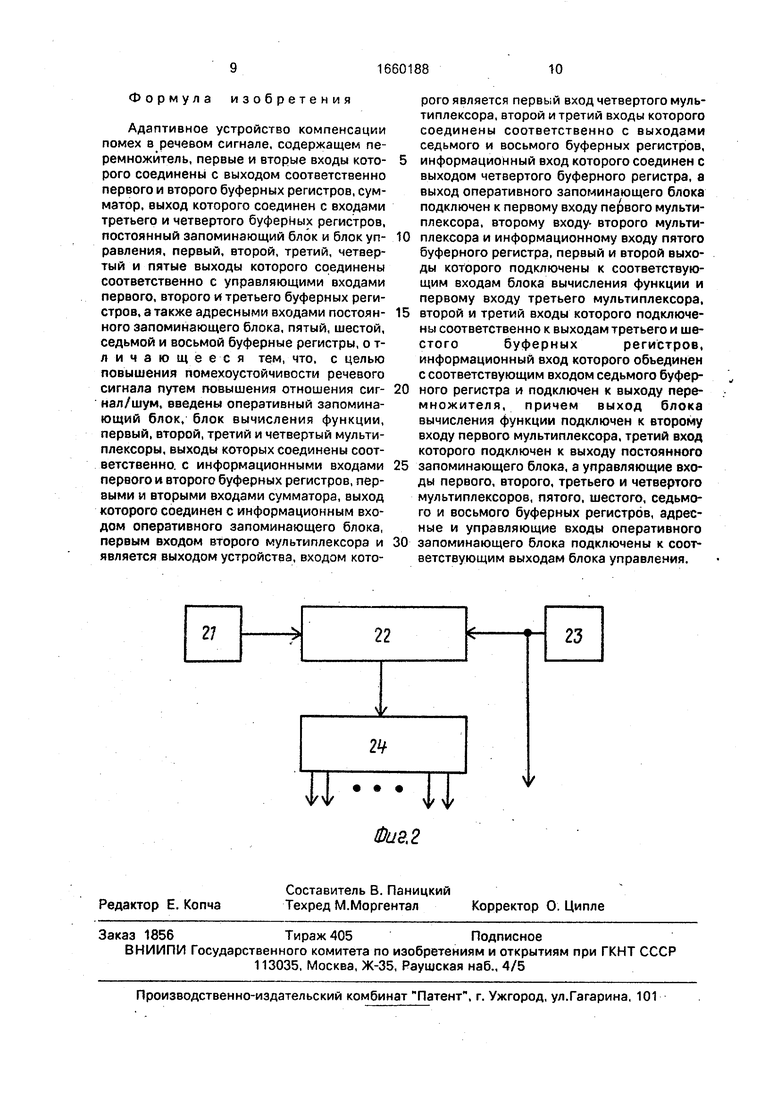

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока управления.

Устройство (фиг. 1) содержит оперативный запоминающий блок (ОЗБ) 1, постоянный запоминающий блок 2 (ПЗБ), перемножитель 3, сумматор 4, блок 5 вычисления функции, первый 6, второй 7, третий 8, четвертый 9, пятый 10, шестой 11, седьмой 12 и восьмой 13 буферные регистры, первый 14, второй 15, третий 16 и четвертый 17 мультиплексоры, блок 18 управления, вход 19 устройства, выход 20 устройства.

Блок 18 управления (фиг. 2) содержит генератор 21 тактовой частоты, счетчик 22, узел 23 формирования пускового сигнала, узел 24 постоянной памяти.

Устройство работает следующим образом.

Блок 5 вычисления функции

р( хг )(фиг. 2) выполнен на мультиплексоре, причем на первый информационный вход мультиплексора поступает информация с выхода пятого буферного регистра 10, на второй информационный вход- постоянная величина Ci, на третий информационный вход - постоянная величина С2, на управляющие входы мультиплексора поступают сигнал переполнения и знаковый разряд из пятого буферного регистра 10. /.

На третий вход второго мультиплексора 15 подается постоянная величина.

На вход устройства 19 поступает зашум- ленный речевой сигнал Zt + ъ а на выходе 20 получается речевой сигнал xt + г1 с улучшенным отношением сигнал/помеха. Процедура обработки зашумленного речевого сигнала описывается следующими уравнениями:

{W ( + i j-vtM

u-,

м.

J

} til () X t Xt

,-

,5

«Ј,, .z .

чtt, -u( 2 t x t -xt

. f«l

. .,i+, При -U Х6|;

Ч(х,Ь| С, «-0.024 при х«Н .024 при х

где К (1)- коэффициент усиления для оценки первого отсчета сигнал xt;

К (2) - коэффициент усиления для оценки второго отсчета сигнала xt - i; К (3)- коэффициент усиления для оценки функции возбуждения;

К (4) - коэффициент усиления для оценки первого коэффициента линейного предсказания;

К (5) - коэффициент усиления для оценки второго коэффициента линейного предсказания;л (i) xt-nv выходнойсигнал;х1+1 -первый

коэффициент линейного предсказания.

xt+r5 - второй коэффициент линейного предсказания.

Экспериментально установлено, что в качестве начальных условий целесообразно принять следующие значения

х0( 0; хо(4) 0,8; х0® 0,4.

Величины К (1), К (2), К (3), К (4), К (5) в процессе вычислений являются постоянными и подбираются экспериментально в диа- пазоне 0,05-0,25 в зависимости от мощности сигнала помехи, действующей на входе. Величина Ј является постоянной, экспериментально подобрана Ј -5 10 2.

Процесс вычисления сигнала xt + 1 состоит из 21 такта, которые протекают следующим образом.

В течение 1-го такта (фиг. 3) выполняется считывание из ОЗБ 1 величины xY1 и

запись ее через первый мультиплексор 14, находящийся в 1-м состоянии, в первый буферный регистр 6.

В течение 2-го такта их ОЗБ 1 считывается величина хг1 и через второй мультиплексор 15, находящийся в 1-м состоянии, записывается во второй буферный регистр 7.

В течение 3-го такта выполняется перемножение величин xt / xt перемножителем 3, на первый и второй входы которого соответственно из первого и второго буферных регистров 6 и 7 поступают величины xv и хг а результат перемножения записывается в шестой буферный регистр 11. Также

в течение 3-го такта выполняется считывание их ОЗБ величины ху и запись ее в буферный регистр 10.

В течение 4-го такта выполняется считывание величины из ОЗБ и запись ее через

первый мультиплексор 14, находящийся в 1-м состоянии, в первый буферный регистр 6. Также в течение 4-го такта выполняется

. Л ft) ч

вычисление величины р( Xt g. При нахож« (3) дении значении числа xf в пределах

л (з)

-1 Xf 1 его численное значение, поступающее из пятого буферного регистра 10 через блок 5, поступает на второй аход первого мультиплексора 14. При нахождении значения числа xY3 в области 1 блок 5 под действием управляющих сигналов из пятого буферного регистра 10, а именно знака числа и разряда переполнения, переключается во второе состояние, пропуская на свой выход постоянное число Ci 0,024. При нахождении значения числа х/ в области xf -1 блок 5 под воздействием управляющих сигналов из пятого буферного регистра 10 переключается в третье состояние, пропуская на Свой выход величину Ci 0.024.

В течение 5-го такта выполняется считывание из ОЗБ 1 величины xt® и запись ее через второй мультиплексор 15, находящийся в 1-м состоянии, во второй буферный регистр 7.

В течение 6-го такта выполняется перемножение величин xt . xt , поступающих на 1-й и 2-й входы перемножителя 3 из первого б и второго 7 буферных регистров. Результат перемножения записывается в седьмой буферный регистр 12.

В течение 7-го такта выполняется суммирование 2)xWxK+ сумматором 4, для

1 1

чего на его 1-й и 2-й входы поступают величины х/ xt и xY2W через третий и четвертый мультиплексоры 16 и 17, находящиеся в 1-м положении из шестого 11 и седьмого буферных регистров. Результат суммирования записывается в третий буферный регистр 8. Также в 7-м такте происходит

запись величины р(хуУ ) в первый буферный регистр 6 через первый мультиплексор 14, переключающийся в этом такте во 2-е состояние, и запись величины Ј во второй буферный регистр 7 через второй мультиплексор 15, находящийся во 2-м состоянии. В течение 8-го такта вычисляется величина Zt+4-2x(Ox(l+ для чего на 1-й

| вход сумматора 4 подается величина

У хк х 9 из третьего буферного регистра

8 через третий мультиплексор 16, переключаемый в 8-м такте в 3-е состояние, а на 2-й вход сумматора 4 поступает входная величина Zt + 1 через четвертый мультиплексор 17, переключаемый в этом такте во 2-е состояние. Результат суммирования записывается в четвертый буферный регистр 9. Кроме того, в 8-м такте выполняется умножение ( хН). для чего на 1-й и 2-й входы

перемножителя 3 подаются соответственно

величины р ( xf ) иЈ из первого 6 и второго 7 буферных регистров, а результат перемножения записывается в шестой 5 буферный регистр 11.

В течение 9-го такта выполняется пересылка величины Zt+t -Y хЬ1 $к 9 из чет1 1

Q вертого буферного регистра 9 в восьмой буферный регистр 13.

В течение 10-го такта вычисляется величина для чего на 1-й вход сумматора 4 через третий мультиплексор 16, находящий5 ся во 2-м состоянии.поступает из пятого буферного регистра 10 величина xV3 . а на 2-й вход сумматора 4 поступает величина Zt + Г

- хК хТ из восьмого буферного реги - (

0 стра 13 через четвертый мультиплексор 17, находящийся в 3-м состоянии. Результат суммирования записывается через второй мультиплексор 15. находящийся в 3-м состоянии, во второй буферный регистр 7. Также

5 в 10-м такте выполняется считывание из

ПЗБ 2 величины К (1) и запись ее через

первый мультиплексор 14, находящийся в

3-м состоянии, в первый буферный регистр

0 в 11-м такте выполняется перемножение K(1)t+i , для чего на -й вход перемножителя 3 из первого буферного регистра 6 поступает величина К(1), а на 2-й вход

к перемножителя 3 из второго буферного ре(z

гистра 1 поступает величина Vt-м . Результат перемножения записывается в седьмой буферный регистр 12.

В 12-м такте выполняется суммирова0 ние K(1)vt+i, для чего, на 1-й вход сумматора 4 через третий мультиплексор 16, находящийся во 2-м состоянии, поступает величина xY3 из пятого буферного регистра 10, а на 2-й вход сумматора 4 через четвертый мультиплексор 17, находящийся в 1-м состоянии, поступает величина К(1) из седь-- мого буферного регистра 12. Результат суммирования записывается в четвертый буферный регистр 9. Также в 12-м такте выполняется считывание из ПЗБ 2 величины К (2) и запись ее через первый мультиплексор 14, находящийся в 3-м состоянии, в первый буферный регистр 6.

В 13-мтакте выполняется пересылка величины xt® + К (1) VtTi из 4-го буферного регистра 9 в восьмой буферный регистр 13,

перемножение К(2) vt т 1 перемножителем 3, для чего на его первый вход из первого

5

0

буферного регистра 6 поступает величина К (2), на второй вход из второго буферного регистра 7 - величина а результат перемножения записывается в седьмой буферный регистр 12. Также в 13-м такте выполняется считывание из ОЗБ 1 величины XY и запись ее в пятый буферный регистр 10.

В 14-м такте выполняется вычисление величины xt+ 1, являющейся выходной величиной, для чего на первый вход сумматора 4 через третий мультиплексор 16, находящийся в 3-м состоянии, из третьего буферного регистра 8 поступает величина

5)хь ) х(- , а на 2-й вход через четвертый

мультиплексор 17, находящийся в третьем состоянии, величина xY3 + K(1) vt-миз восьмого буферного регистра 13. Результат суммирования записывается в ОЗБ 1. Также в 14-м такте выполняется считывание из ПЗВ 2 величины К(3) и запись ее в первый буферный регистр б через первый мультиплексор 14, находящийся в 3-м состоянии.

В 15-м такте выполняется вычисление величины xt + 1 , для чего на 1-й вход сумматора 4 поступает величина х + 1 из пятого буферного регистра 10 через третий мультиплексор 16, находящийся во 2-м положении, а на 2-й вход сумматора 4 поступает величина К (2) из седьмого буферного регистра 12 через четвертый мультиплексор 17, находящийся в 1-м положении. Результат суммирования записывается в ОЗБ 1.

В 16-м такте выполняется перемножение К (3) ffҐi перемножителем 3, для чего на 1-й вход перемножителя 3 из первого буферного регистра 6 поступает величина К (3), а на 2-й вход перемножителя 3 - величина из второго буферного регистра 7. Результат перемножения записывается в седьмой буферный регистр 12,

В 17-м такте вычисляется величина г , для чего на 1-й вход сумматора 4 через третий мультиплексор 16, находящийся во 1-м состоянии, из шестого буферного регистра

11 поступает величина Ј р ( хН/), а на второй вход сумматора 4 через четвертый мультиплексор 17, находящийся в 1-м положении, из седьмого буферного регистра 12

поступает величина К (3) Результат суммирования записывается в ОЗБ 1. Также в 17-м такте выполняется считывание ПЗБ 2 величины К (4) и запись ее через первый мультиплексор 14, находящийся в 3-м положении, в первый буферный регистр 6.

В 18-м такте также выполняется перемножение К (4) VHM перемножителем 3, для чего на 1-й вход перемножителя 3 из первого буферного регистра 6 поступает величина АЛ

К(4), а на 2-й вход величина щ -и из второго

буферного регистра 7. Результат перемножения записывается в седьмой буферный регистр 12. Также в 18-м такте выполняется

считывание из ОЗБ 1 величины xt и запись ее в пятый буферный регистр 10.

В 19-м такте вычисляется величина xt + 1 , для чего на 1-й вход сумматора 4 поступает величина через третий мультиплексор

16, находящийся во 2-м состоянии, из пятого буферного регистра 10, а на 2-й вход

сумматора 4 поступает величина К (4) . через четвертый мультиплексор 17, находящийся в 1-м состоянии, из седьмого буферного регистра 12, Результат суммирования записывается в ОЗБ 1. Также в 19-м такте выполняется считывание из ПЗБ 2 К (5) и запись ее в первый буферный регистр 6 через первый мультиплексор 14, находящийся

в 3-м состоянии,

В 20-м такте выполняется перемножение К (5) Vt+i перемножителем 3, для чего на 1-й вход перемножителя 3 поступает величина К (5) из первого буферного регистра

6, а на 2-й вход поступает величина т4+1из второго буферного регистра 7. Результат перемножения записывается в седьмой буферный регистр 12. Также в 20-м такте

выполняется считывание из ОЗБ 1 величины xY5 и запись ее в пятый буферный регистр 10.

В 21-м такте выполняется вычисление величины xt + 1 , для чего на 1-й вход сумматера 4 поступает величина через третий мультиплексор 16, находящийся во 2-м состояний, из пятого буферного регистра 10, а на 2-й вход сумматора 4 поступает величина через четвертый мультиплексор

Блок 18 управления (фиг. 2) работает Следующим образом,

При включении питания узел 23 формирования пуска вырабатывает сигнал Начальная установка, который сбрасывает счетчик 22 и ОЗБ (фиг. 1) в исходное состояние. Счетчик 22 под воздействием импульсов, поступающий с генератора 21. формирует адрес для узла 24 постоянной памяти, в котором записаны микрокоманды управления устройством для каждого такта.

Формула изобретения

Адаптивное устройство компенсации помех в речевом сигнале, содержащем пе- ремножйтель, первые и вторые входы которого соединены с выходом соответственно первого и второго буферных регистров, сумматор, выход которого соединен с входами третьего и четвертого буферных регистров, постоянный запоминающий блок и блок управления, первый, второй, третий, четвертый и пятые выходы которого соединены соответственно с управляющими входами первого, второго и третьего буферных регистров, а также адресными входами постоянного запоминающего блока, пятый, шестой, седьмой и восьмой буферные регистры, о т- личающееся тем, что, с целью повышения помехоустойчивости речевого сигнала путем повышения отношения сигнал/шум, введены оперативный запоминающий блок, блок вычисления функции, первый, второй, третий и четвертый мультиплексоры, выходы которых соединены соответственно, с информационными входами первого и второго буферных регистров, первыми и вторыми входами сумматора, выход которого соединен с информационным входом оперативного запоминающего блока, первым входом второго мультиплексора и является выходом устройства, входом кото27

рого является первый вход четвертого мультиплексора, второй и третий входы которого соединены соответственно с выходами седьмого и восьмого буферных регистров,

информационный вход которого соединен с выходом четвертого буферного регистра, а выход оперативного запоминающего блока подключен к первому входу первого мультиплексора, второму входу- второго мультиплексора и информационному входу пятого буферного регистра, первый и второй выходы которого подключены к соответствующим входам блока вычисления функции и первому входу третьего мультиплексора,

второй и третий входы которого подключены соответственно к выходам третьего и шестогобуферныхрегистров, информационный вход которого объединен с соответствующим входом седьмого буферного регистра и подключен к выходу перемножителя, причем выход блока вычисления функции подключен к второму входу первого мультиплексора, третий вход которого подключен к выходу постоянного

запоминающего блока, а управляющие входы первого, второго, третьего и четвертого мультиплексоров, пятого, шестого, седьмого и восьмого буферных регистров, адресные и управляющие входы оперативного

запоминающего блока подключены к соответствующим выходам блока управления.

22

| Патент США ISfe 4587620, кл.Н 04 В 15/00, 1986 |

Авторы

Даты

1991-06-30—Публикация

1988-09-08—Подача