(54) СИНТЕЗАТОР РЕЧЕВЫХ СИГНАЛОВ

1

Изобретение относится к приборостроению и может быть использовано, например, в вокодерной технике.

Известно устройство для синтезирование речевых сигналов, в котором для ана- 5 лиза и синтеза речи используются коэффициенты предсказания il.

К погрешностям этого устройства следует отнести потенциальную неустойчивость анализируемого фильтра и необходи- 10 мую величину разрядной сетки специализированного вычислителя.

Наиболее близким к изобретению по своей технической сущности является синте- 15 затор речевых сигналов, содержащий выходную шину, умножитель, первый вход которого соединен с шиной весовой функции, второй вход - с выходом первого мультиплексора, а выход - с первым входом 20 сумматора, подключенного выходом к входу первого оперативного запоминающего устройства, а также блок управления, подключенный выходами к управляющим входам сумматора, первого и второго мульти- 25 плексоров и двух оперативных запоминающих устройств :2.

Цель изобретения заключается в повышении достоверности синтезирования речевых сигналов.30

Достигается это за счет снабжения устройства буферным регистром и третьим мультиплексором, ггрйчем первые входы второго и третьего мультиплексоров соединены с выходом сумматора, второй вход которого соединен с выходом буферного регистра и с выходной шиной, выход третьего мультиплексора через второе оперативное запоминающее устройство соединен с первым входом первого мультиплексора и с вторым входом второго мультиплексора, соединенного выходом с входом буферного регистра, второй вход третьего мультиплексора соединен с выходом первого оперативного запоминающего устройства и с вторым входом первого мультиплексора, а управляющие входы буферного регистра и третьего мультиплексора соединены с соответствующими выходами блока управления.

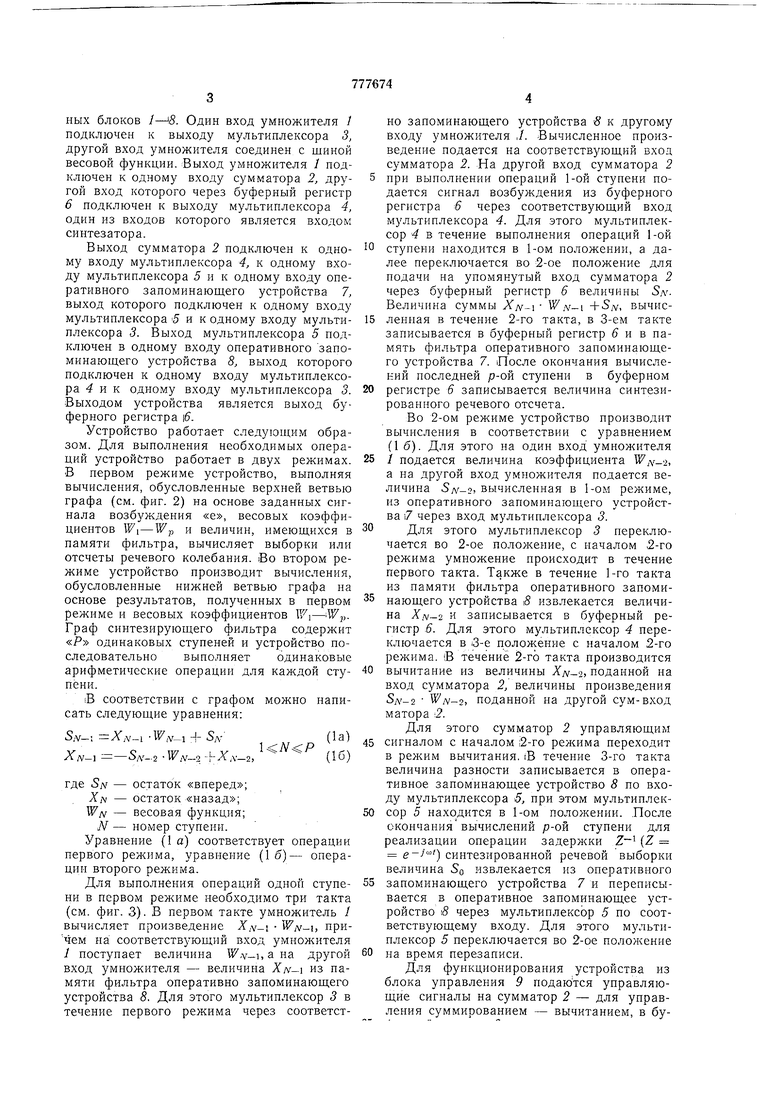

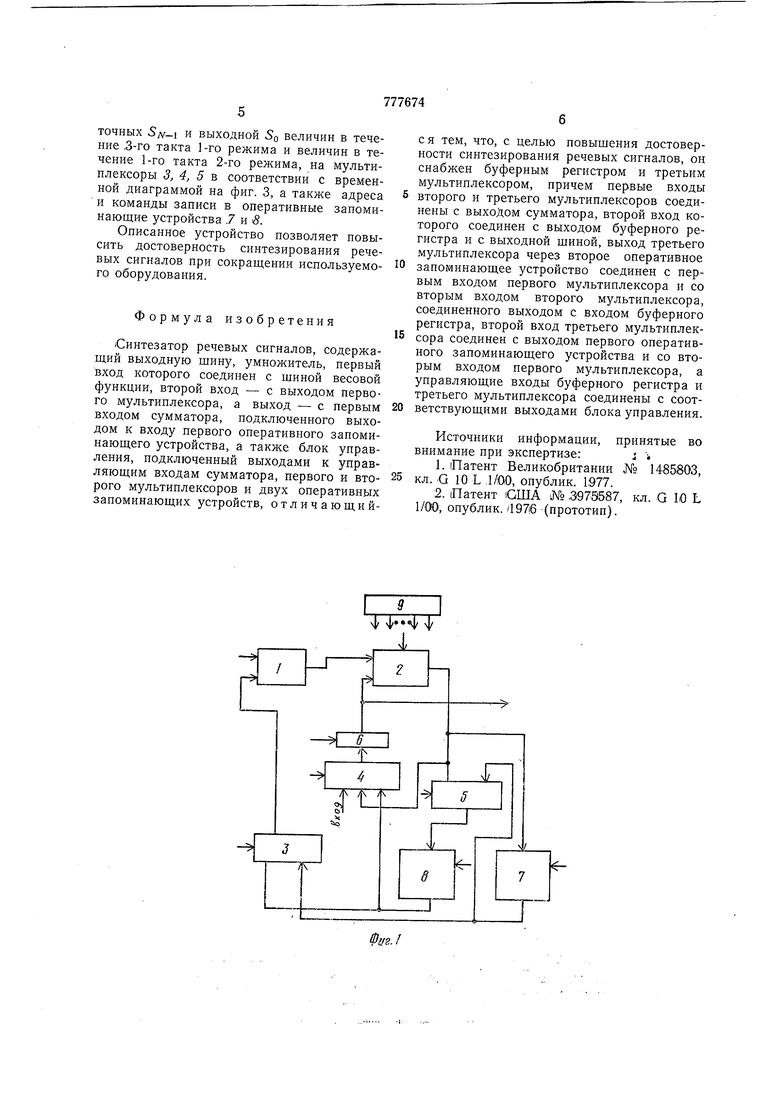

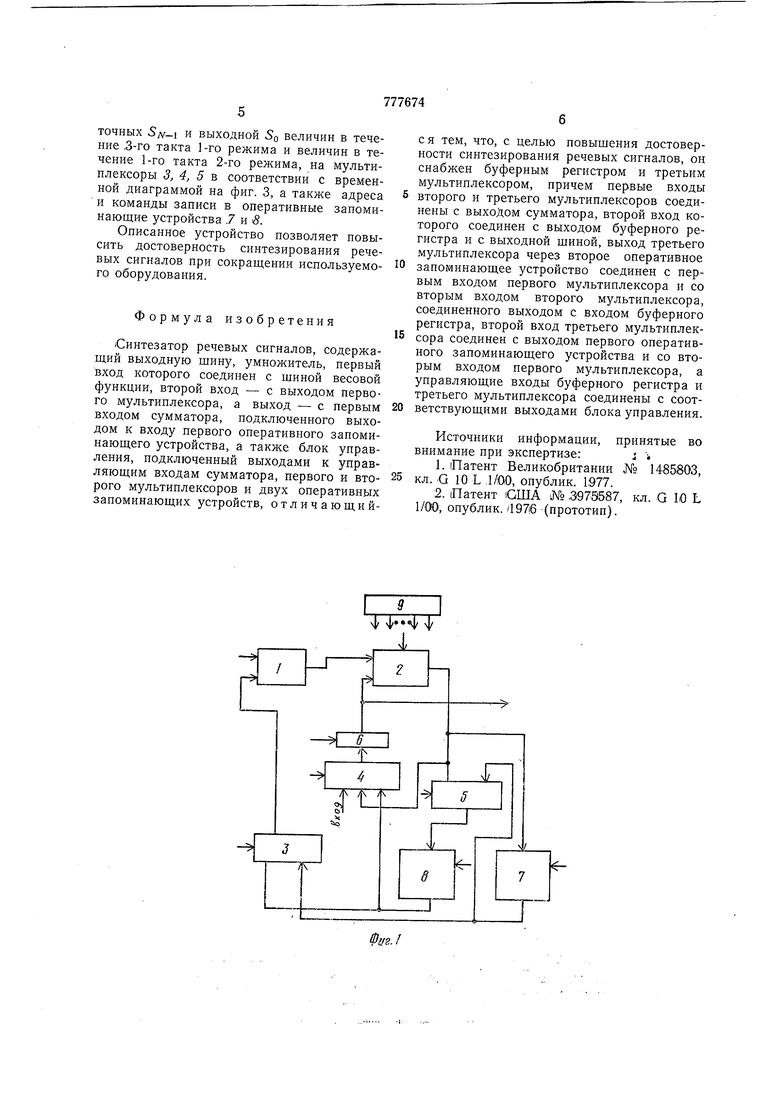

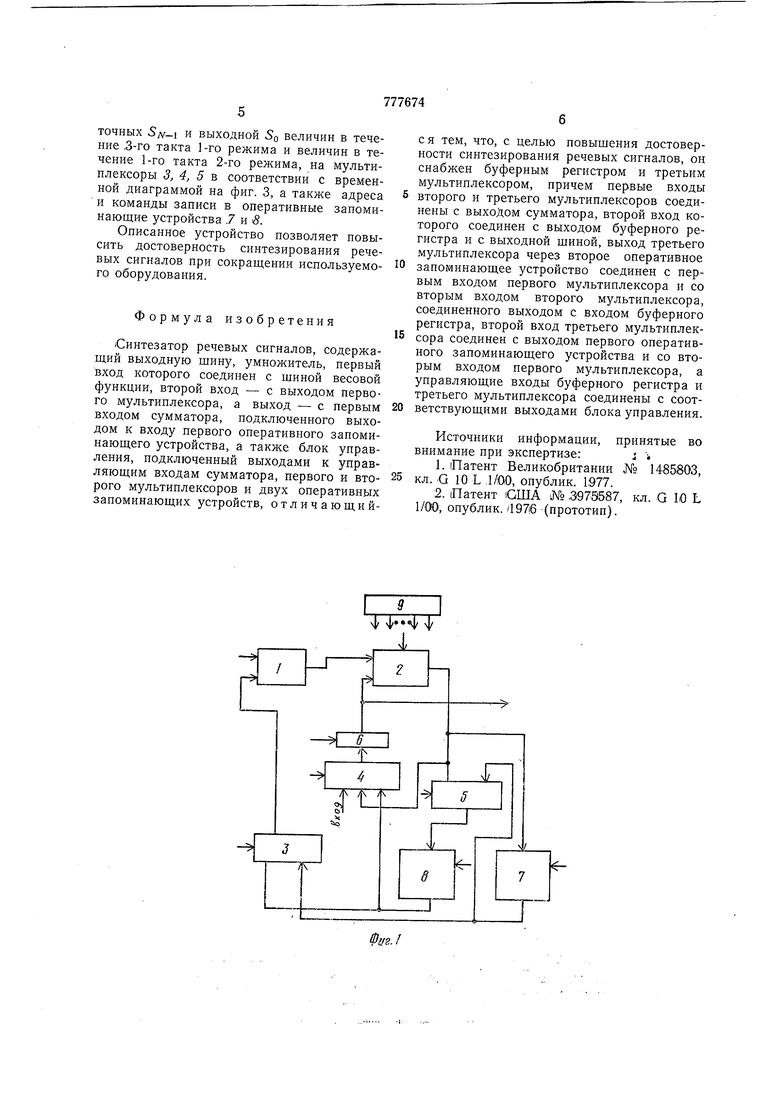

На фиг. 1 приведена структурная схема описываемого устройства; на фиг. 2 - граф синтеза; на фиг. 3 - временная диаграмма работы устройства.

Устройство содержит умножитель У, сумматор 2, мультиплексоры 3, 4 н 5, буферный регистр 6, оперативные запоминающие устройства 7, 8 и блок управления 9. Выходы блока управления 9 подключены к управляющим входам всех вышеназванных блоков . Один вход умножителя / подключен к выходу мультиплексора 3, другой вход умножителя соединен с шиной весовой функции. Выход умножителя / подключен к одному входу сумматора 2, другой вход которого через буферный регистр 6 подключен к выходу мультиплексора 4, один из входов которого является входом синтезатора.

Выход сумматора 2 подключен к одному входу мультиплексора 4, к одному входу мультиплексора 5 и к одному входу оперативного запоминающего устройства 7, выход которого подключен к одному входу мультиплексора 5 и к одному входу мультиплексора 3. Выход мультиплексора 5 подключен в одному входу оперативного запоминающего устройства 8j выход которого подключен к одному входу мультиплексора - и к одному входу мультиплексора 3. Выходом устройства является выход буферного регистра 6.

Устройство работает следующим образом. Для выполнения необходимых операций устройство работает в двух режимах. В нервом режиме устройство, выполняя вычисления, обусловленные верхней ветвью графа (см. фиг. 2) на основе заданных сигнала возбуждения «е, весовых коэффициентов Wi-Wp и величин, имеющихся в памяти фильтра, вычисляет выборки или отсчеты речевого колебания. Во втором режиме устройство производит вычисления, обусловленные нижней ветвью графа на основе результатов, полученных в первом режнме и весовых коэффициентов Wi-Wp. Граф синтезирующего фильтра содержит «Р одинаковых ступеней и устройство последовательно выполняет одинаковые арифметические операции для каждой ступени.

iB соответствии с графом можно написать следующие уравнения:

(1а)

S.V-1 - Ал-i W/v-i (16) XN-I -5л-.2 -Wiv-z -Х,-2,

где SN - остаток «вперед ;

- остаток «назад ;

WN - весовая функция; N - номер ступени.

Уравнение (1 а) соответствует операции первого режима, уравнение (1 б)- операции второго режима.

Для выполнения операций одной ступени в первом режиме необходимо три такта (см. фиг. 3). В первом такте умножитель / вычисляет произведение ..y-i л-ь причем на соответствующий вход умножителя 1 поступает величина ,у-ь а на другой вход умножителя - величина XN-I из памяти фильтра оперативно запоминающего устройства 8. Для этого мультиплексор 3 в течение первого режима через соответстно запоминающего устройства § к другому входу у.множителя ,/. Вычисленное произведение подается на соответствующий вход сумматора 2. На другой вход сумматора 2 нри выполнении операций 1-ой ступени подается сигнал возбуждения из буферного регистра 6 через соответствующий вход мультиплексора 4. Для этого мультиплексор 4 в течение выполнения операций 1-ой

ступени находится в 1-ом положении, а далее переключается во 2-ое положение для подачи на упомянутый вход сумматора 2 через буферный регистр 6 величины 5,v. Величина суммы ,v-i N- +Si, вычисленная в течение 2-го такта, в 3-ем такте записывается в буферный регистр 6 и в память фильтра оперативного запоминающего устройства 7. После окончания вычислений последней р-ой ступени в буферном

регистре 6 записывается величина синтезированного речевого отсчета.

Во 2-ом режиме устройство производит вычисления в соответствии с уравнением (16). Для этого на один вход умножителя

/ подается величина коэффициента д,2, а на дрзгой вход умножителя подается величина , вычисленная в 1-ом режиме, из оперативного запоминающего устройства 7 через вход мультиплексора 3.

Для этого мультиплексор 3 переключается во 2-ое положение, с началом 2-го режима умножение происходит в течение первого такта. Также в течение 1-го такта из памяти фильтра оперативного запоминающего устройства iS извлекается величина и записывается в буферный регистр 5. Для этого мультиплексор 4 переключается в i3-e положение с началом 2-го режима. sB течение 2-го такта производится

вычитание из величины Xiv-o, поданной на вход сумматора 2, величины произведения 5л-2 N-2, поданной на другой сум-вход матора -2.

Для этого сумматор 2 управляющим

сигналом с началом ;2-го режима переходит в режим вычитания. iB течение 3-го такта величина разности записывается в оперативное запоминающее устройство 8 по входу мультиплексора 5, при этом мультиплексор 5 находится в 1-ом положении. После окончания вычислений р-ой ступени для реализации операции задержки (Z синтезированной речевой выборки величина 5о извлекается из оперативного

запоминающего устройства 7 и переписывается в оперативное запоминающее устройство 8 через мультиплексор 5 по соответствующему входу. Для этого мультиплексор 5 переключается во 2-ое положение

на время перезаписи.

Для функционирования устройства из блока управления 9 подаются управляющие сигналы на сумматор 2 - для управления суммированием - вычитанием, в буточных Sjv-i и выходной So величин в течение ,3-го такта 1-го режима и величнн в течение 1-го такта 2-го режима, на мультиплексоры 3, 4, 5 ъ соответствии с временной диаграммой на фиг. 3, а также адреса и команды записи в оперативные запоминающие устройства .7 и .

Описанное устройство позволяет повысить достоверность синтезирования речевых сигналов при сокращении используемого оборудования.

Формула изобретения

Синтезатор речевых сигналов, содержащий выходную щину, умножитель, первый вход которого соединен с шиной весовой функции, второй вход - с выходом первого мультиплексора, а выход - с первым входом сумматора, подключенного выходом к входу первого оперативного запоминающего устройства, а также блок управления, подключенный выходами к управляющим входам сумматора, первого и второго мультиплексоров и двух оперативных запоминающих устройств, отличающийся тем, что, с целью повыщеиия достоверности синтезирования речевых сигналов, он снабжен буферным регистром н третьим мультиплексором, причем первые входы второго и третьего мультиплексоров соединены с выходом сумматора, второй вход которого соединен с выходом буферного регистра и с выходной щиной, выход третьего мультиплексора через второе оперативное запоминающее устройство соединен с первым входом первого мультиплексора и со вторым входом второго мультиплексора, соединенного выходом с входом буферного регистра, второй вход третьего мультиплексора соединен с выходом первого оперативного запоминающего устройства и со вторым входом первого мультиплексора, а управляющие входы буферного регистра н третьего мультиплексора соединены с соответствующими выходами блока управления.

Источники информации, принятые во внимание при экспертизе:; :

1.Патент Великобритании № 1485803, кл. G 10 L .1/00, опублик. 1977.

2.(Патент США № ,3979587, кл. G 10 L 1/00, опублик. 19716 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное устройство компенсации помех в речевом сигнале | 1988 |

|

SU1660188A1 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

| Цифровая адаптивная антенная система | 1990 |

|

SU1810943A1 |

| Устройство конференц-связи с дельта-модуляцией | 1989 |

|

SU1660202A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Устройство для вычисления функций в модулярной системе счисления | 1985 |

|

SU1322268A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| ГЕНЕРАТОР СЛУЧАЙНОГО ПРОЦЕССА | 1991 |

|

RU2050585C1 |

ступень.

,- cmynem

(-.

-ая

ступень р-о

5 |-t-J-1сотуда/т р-1-ая

.

J-biu решим

Диаграмаа переключений ,пиллексора /

Диаграмма переключений Mt/fHimun/ieKCopa 3 I.2

1

/Диаграмма переключений му/игтиплексо/за 5

/

Фиг. 2 I---Ступень

1-ая

--..,...,

сттет

2-01J режаг

Фаг. 3

Авторы

Даты

1980-11-07—Публикация

1979-02-06—Подача