f12

Изобретение относится к вычислительной технике и может быть использовано при умножении чисел в системе счисления с двоичньм основанием или основанием, равным целой степени двух.

Цель изобретения повьппение быстродействия и точности устройства.

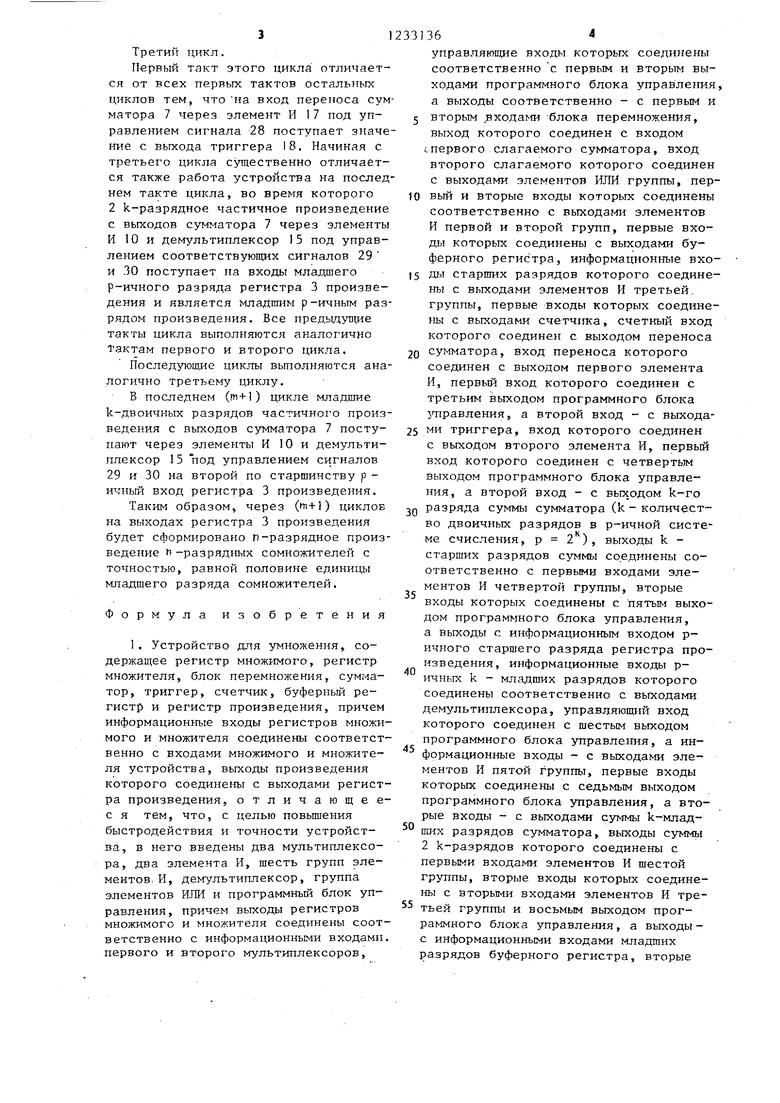

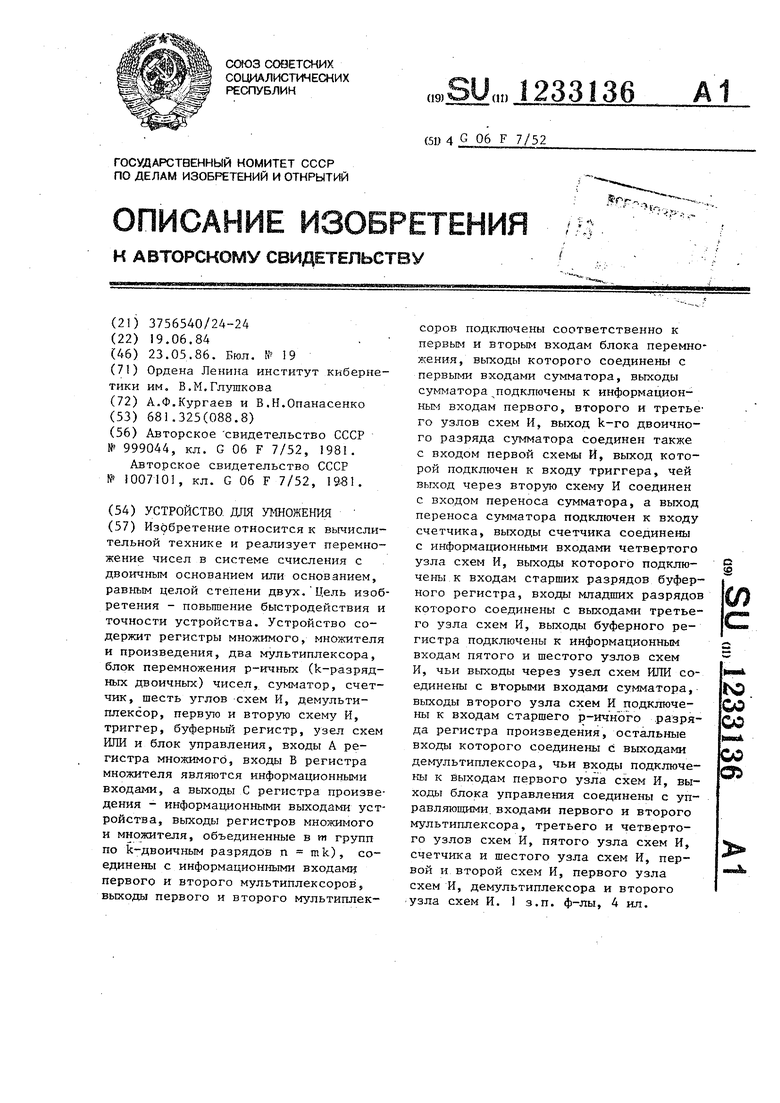

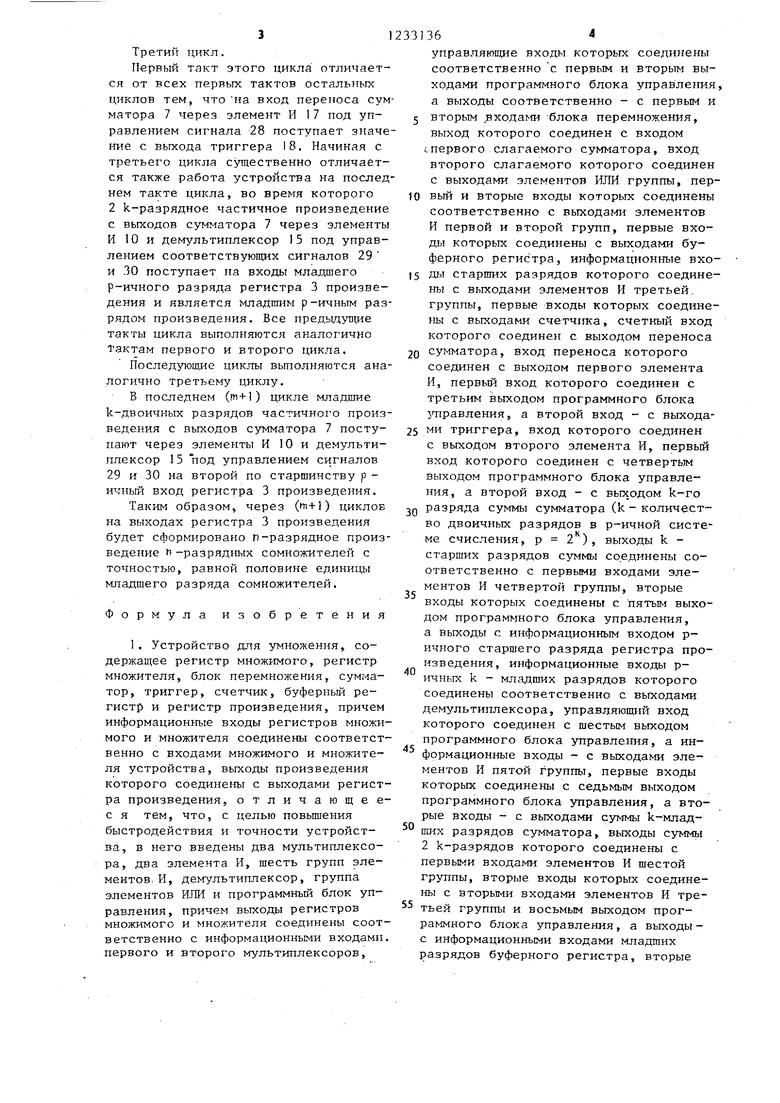

На фиг.1 приведена блок-схема предлагаемого устройства; на фиг,2 - структурная схема прогр;зммного блока; на фиг.З - временная диаграм -1а работы программного блока управления; на фиг.4 - блок-схема алгоритма управления программного блока управления.

Блок-схема устройства для умножения, содержит регистры множимого 1, множителя 2 и произведения 3, два мультиплексора 4 и 5, блок б перемножения, сумматор 7, счетчик 8, шесть - групп элементов И 9 - 1А, демульти- плексор 15, два элемента И 16 и 17, триггер,18, буферный регистр 19, , группу элементов ИЛИ 20 и программный блок 21 управления выходы 22-31 блока управления,

Программньй блок 21 управления содержит счетчик 32, блок 33 микропрограммной памяти, регистр 34 микроко- . манд, две группы элементов И 35 и 36 два элемента 37 и 38 задержки.

Устройство работает следующим образом.

Микропрограмма записана в блоке 33 микропрограммной памяти в виде последовательности микрокоманд, адреса которых следу от в естественном порядке и формируются с помощью счетчика 32,

В исходном состоянии множимое А И множитель В записаны в регистры t множимого 1 и множителя 2, в регистре 34 микрокоманд содерзкится первая ьткрокоманда5 соответствующая адресу 00...О блока 33 микропрограммной памяти. Все триггерные элементы, счетчики и регистры устройства установлены в нуль. Процесс умножения состоит из (т+1) циклов. Первый цикл содержит (т-1) тактов, второй ч, третий (т-1), и далее число тактов в каждом последующем цикле уменьшается на единицу и последний (т+1)-й: цикл состоит из одного такта . В первом такте каждого цикла про- изводится установка счетчика 8 в исходное состояние. Такт представляет собой формирование частичного произ5

1

5

0

0

5

0 5 0 5

362

ведении р-ичньтх (k-разрядньтх двоич- :ных) чисел множи1-(ого и множителя. Результатом работы одного цикла является формирование суммы частичных про изведений, имеюп1 1х одинаковые веса

Расс;мотрим поеледовательно работу устройства для различных циклов.

Первый цикл.

Под управлением сигналов 22 и 23 , мультиплексоры 4 и 5 выбирают соот- }зетств тощие р-ичные разряды множимого и множителя. В блоке 6 перемноже- i rfflH выт-гисляется произведение двух

J

k-разрядньгх двоип1ных чисел, поступаю- 1ЦИХ на его входы с выходов Ь5ульти- плексо юв„ 2 k-разрядное произведе- iffle с выходов блока 6 перемножения в каждом такте поступает на первые входы сз гматора 7, а на его вторые входы ггоступает через элементы И 13 и 14 частичное произведение, записанное па предыдуш.ем такте в буферном регистре 19 (на первом такте первого цикла - значение 00,,.0), Если такт является первым в данном цикле,, то иа вторые входы сумматора- 7 поступает частичное произведение с выходов буферного регистра 19 через элементы И 1 б со сдвигом па k-ДБоичных разрядов вправо (в сторону младших разрядов) под управлением сигнала 26, Во всех остальных тгяктах цикла на вторые входы cyivnviaTopa 7 поступает час- тичное произведение с выходов буферного регистра 19 через элементы И 14 под управлением сигнала 25. Число переносов с выхода сумматора 7 фиксируется в счетчике 8 и через элементы И 9 дод управлением сигнала 24 записывается в кащ1ом такте в старшие разряды буферного регистра 19. Одновременно с этим в младшие разряды буферного регистра 9 записьшается 2 k-paspHAHoe (цноичное) частичное произведение с выходов сумматора 7 через элементы И 2.

Вторюй цикл-.

В начаг е первого такта производится уста-НОЕ1ка счетчика 8 в исходное состояв:ие Все такты этого цикла,, кроме последнего; выполняются аналогично тактам первого цикла. На последнем такте второго цикла k-двоичный разряд с выхода сум1 - атора 7 через элемент И 16 управлением сигнала 27 йиксируется в триггере 18.

3

Третий цикл.

Первый такт этого цикла отличается от всех первых тактов остальных циклов тем, что на вкод переноса сумматора 7 через элемент И 17 под управлением сигнала 28 поступает значение с выхода триггера 18. Начиная с третьего цикла существенно отличается также работа устройства на последнем такте цикла, во время которого 2 k-разрядное частичное произведение с выходов сумматора 7 через элементы И 10 и демультиплексор 15 под управлением соответствующих сигналов 29 и -30 поступает на входы младшего р-ичного разряда регистра 3 произведения и является младш1м р-ичным разрядом произведения. Все предыдувще такты цикла выполняются аналогично Тактам первого и второго цикла.

Последующие циклы вьшолняются аналогично третьему циклу.

В последнем (m+l) цикле младшие k-двоичных разрядов частичного произведения с выходов сумматора 7 поступают через элементы И 10 и демультиплексор 15 под управлением сигналов 29 и 30 на второй по старшинству р- ичный вход регистра 3 произведения.

Таким образом, через (ш+1) циклов на выходах регистра 3 произведения будет сформировано п-разрядное произведение п-разрядьа1х сомножителей с точностью, равной половине единицы младшего разряда сомножителей.

Формула изобретения

1. Устройство для умножения, содержащее регистр множ1-1мого, регистр множителя, блок перемножения, сумматор, триггер, счетчик, буферный регистр и регистр произведения, причем информационные входы регистров множимого и множителя соединены соответственно с входами множимого и множителя устройства, выходы произведения которого соединены с выходами регистра произведения, отличающее- с я тем, что, с целью повышения быстродействия и точности устройства, в него введены два мультиплексора, два элемента И, шесть групп элементов. И, демультиплексор, группа элементов ИЛИ и программный блок управления, причем выходы регистров множимого и множителя соединены соответственно с информационными входами первого и второго мультиплексоров.

33136

управляющие входы которых соединены соответственно с первым и вторым выходами программного блока управления, а выходы соответственно - с первым и 5 вторым входами блока перемножения,

выход которого соединен с входом tпервого слагаемого сумматора, вход второго слагаемого которого соединен с выходами элементов ИЛИ группы, пер- 10 вый и вторые входы которых соединены соответственно с выходаж-г элементов И первой и второй групп, первые входы которых соединены с выходами буферного регистра, информационные вхо- 15 ДЬ1 старших разрядов которого соединены с выходами элементов И третьей, группы, первые входы которых соединены с выходами счетчика, счетный вход которого соединен с выходом переноса 20 сумматора, вход переноса которого соединен с выходом первого элемента И, первый вход которого соединен с третыда выходом программного блока зтфавления, а второй вход - с выхода- 25 ми триггера, вход которого соединен с выходом второго элемента И, первый вход которого соединен с четвертью выходом программного блока управления, а второй вход - с выходом k-ro 30 разряда суммы сумматора (k - количество двоичных разрядов в р-ичной системе счисления, р 2), выходы k - старших разрядов суммы соединены соответственно с первьми входами элементов И четвертой группы, вторые входы которых соединены с пятьм выходом программного блока управления, а выходы с информационным входом р- ичного старшего разряда регистра произведения, информационные входы р- ичных k - младших разрядов которого соединены соответственно с выходами демультиплексора, управляющей вход которого соединен с шестым выходом программного блока управления, а информационные входы - с выходами элементов И пятой группы, первые входы которых соединены с седьмым выходом программного блока управления, а вторые входы - с выходами суммы k-млад- ших разрядов сумматора, выходы сутфсы 2 k-разрядов которого соединены с первыми входами элементов И шестой группы, вторые входы которых соедине- цы с вторыми входами элементов И тре- тьей группы и восьмым выходом программного блока управления, а выходы- с информационными входами младших разрядов буферного регистра, вторые

35

W

45

50

входы элементов И первой группы соединены соответственно с девятым выходом программного блока управления, десятьп выход которого соединен с вторыми входами элементов И второй группы и тактовым входом счетчика, тактовый вход устройства соединен с входом программного блока управления

2. Устройство по п.1, о т л и - чающееся тем, что программный блок управления содержит две группы элементов И, регистр микрокоманд, блок микропрограммной памяти, два элемента задержки и йчетчик, вход которого соединен с входом программного блока управления и входами первого и второго элементов задержки

1

iL. f

выходы которых соединены соответственно с первыми входами элементов И первой и второй групп, вторые входы

которых соединены соответственно с разрядными выходами регистра микрокоманд, информационный вход которого соединен с выходами блока микропрограммной памяти, вход которого соединен с выходом счетчика, выходы элементов И первой группы соединены соответственно с первым, вторым, девятым, десятым и третьим выходами программного блока управления, восьмой,

четвертый, седьмой, шестой и пятый выходы которого соединены соответственно с выходами элементов И второй группы,

LJJTr.

25

IL

|.««Ар.

JLiAjL

ii«en)lj.,. ,„„, ,,„,„,

;

22

2Б

Редактор Н.Бобкова

Составитель ЕаЗахарченко

Техред ЛоОпейншс Корректор Е.Рошко

Заказ 2771/50Тираж 67 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-ЗЗ, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

0мгЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1985 |

|

SU1305667A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для умножения последовательного действия | 1983 |

|

SU1157541A1 |

| Устройство для умножения | 1984 |

|

SU1185328A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

| Устройство для умножения в позиционной избыточной ( @ , @ )-системе счисления | 1982 |

|

SU1067498A1 |

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| Устройство для умножения | 1982 |

|

SU1137463A1 |

Изобретение относится к вычислительной технике и реализует перемножение чисел в системе счисления с двоичным основанием или основанием, равным целой степени двух. Цель изобретения - повьтение быстродействия и точности устройства. Устройство содержит регистры множимого, множителя и произведения, два мультиплексора, блок перемножения р-ичных (k-разряд- ных двоичных) чисел, сумматор, счетчик, шесть углов -схем И, демульти- плексор, первую и вторую схему И, триггер, буферньш регистр, узел схем ИЛИ и блок управления, входы А регистра множимого, входы В регистра множителя являются информационными входами, а выходы С регистра произведения - информационными выходами устройства, выходы регистров множимого и множителя, объединенные в nt групп по k-двоичным разрядов п mk), соединены с информационными входами первого и второго мультиплексоров, выходы первого и второго мультиплексоров подключены соответственно к первым и вторым входам блока перемножения, выходы которого соединены с первыми входами сумматора, выходы сумматора подключены к информационным входам первого, второго и третье го узлов схем И, выход k-ro двоичного разряда сумматора соединен также с входом первой схемы И, выход которой подключен к входу триггера, чей выход через вторую схему И соединен с входом переноса сумматора, а выход переноса сумматора подключен к входу счетчика, выходы счетчика соединены с информационными входами четвертого узла схем И, выходы которого подключены к входам старших разрядов буферного регистра, входы младших разрядов которого соединены с выходами третьего узла схем И, выходы буферного регистра подключены к информационным входам пятого и шестого узлов схем И, чьи выходы через узел схем ИЛИ соединены с вторыми входами сумматора, выходы второго узла схем И подключены к входам старшего р-ичного .разряда регистра произведения, остальные входы которого соединены с выходами демультиплексора, чьи входы подключены к Выходам первого узла схем И, выходы блока управления соединены с уп- равляюшкми. входами первого и второго мультиплексора, третьего и четвертого узлов схем И, пятого узла схем И, счетчика и шестого узла схем И, первой и второй схем И, первого узла схем И, демультиплексора и второго узла схем И. 1 з.п. ф-лы, 4 ил. i с: ю со оо ЦпкА оо С35

| Матричное устройство для умножения | 1981 |

|

SU999044A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ДИАФРАГМЕННЫЙ НАСОС | 1926 |

|

SU7101A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-23—Публикация

1984-06-19—Подача