О

ON СО

сл

0 О

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| Устройство для адаптивной настройки корректора межсимвольных искажений | 1977 |

|

SU743212A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство коррекции | 1987 |

|

SU1499507A1 |

| Ранговый обнаружитель сигналов | 1981 |

|

SU970291A1 |

| Следящий фильтр фазоманипулированного псевдослучайного сигнала | 1986 |

|

SU1394411A1 |

| РЕЛЕ ТОКА | 2014 |

|

RU2563959C1 |

| Устройство слежения за задержкой шумоподобных сигналов | 1988 |

|

SU1628211A1 |

| Дельта-декодер | 1986 |

|

SU1432779A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

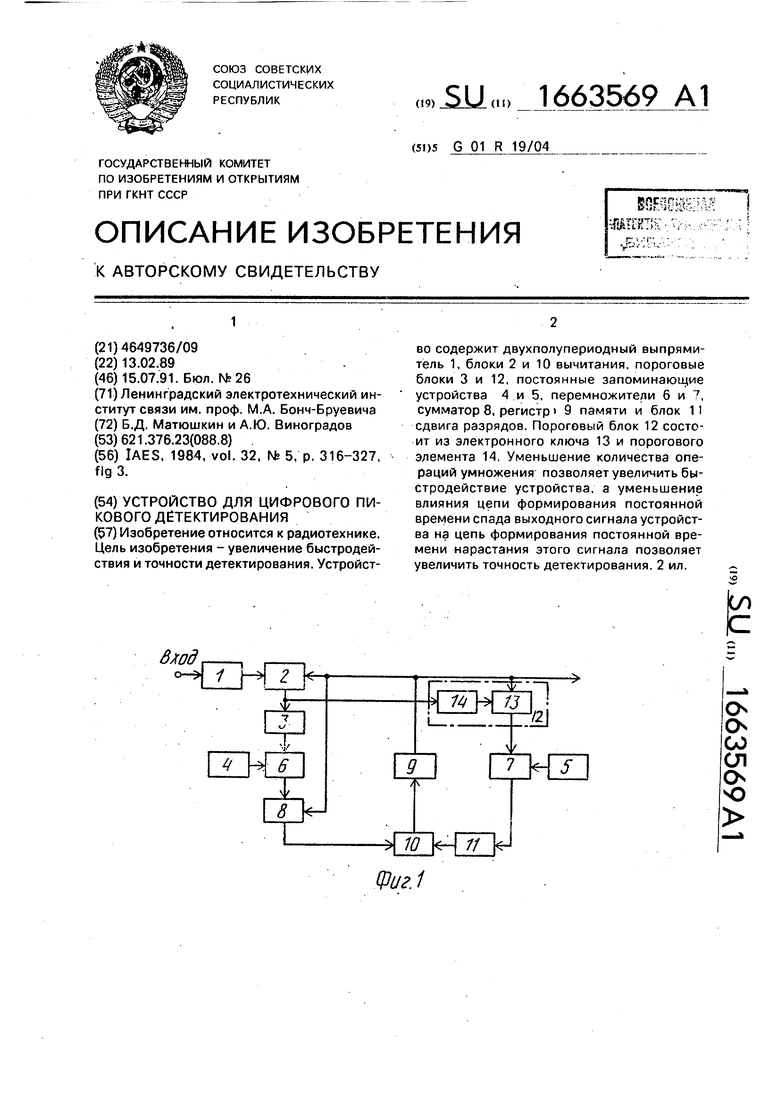

Изобретение относится к радиотехнике. Цель изобретения - увеличение быстродействия и точности детектирования. Устройство содержит двухполупериодный выпрямитель 1, блоки 2 и 10 вычитания, пороговые блоки 3 и 12, постоянные запоминающие устройства 4 и 5, перемножители 6 и 7, сумматор 8, регистр 9 памяти и блок 11 сдвига разрядов. Пороговый блок 12 состоит из электронного ключа 13 и порогового элемента 14. Уменьшение количества операций умножения позволяет увеличить быстродействие устройства, а уменьшение влияния цепи формирования постоянной времени спада выходного сигнала устройства на цепь формирования постоянной времени нарастания этого сигнала позволяет увеличить точность детектирования. 2 ил.

Фиг.1

Изобретение относится к области ради отехники и может быть использовано в радиовещательной технике, технике связи и звукозаписи.

Цель изобретения -увеличение быстродействия и точности детектирования.

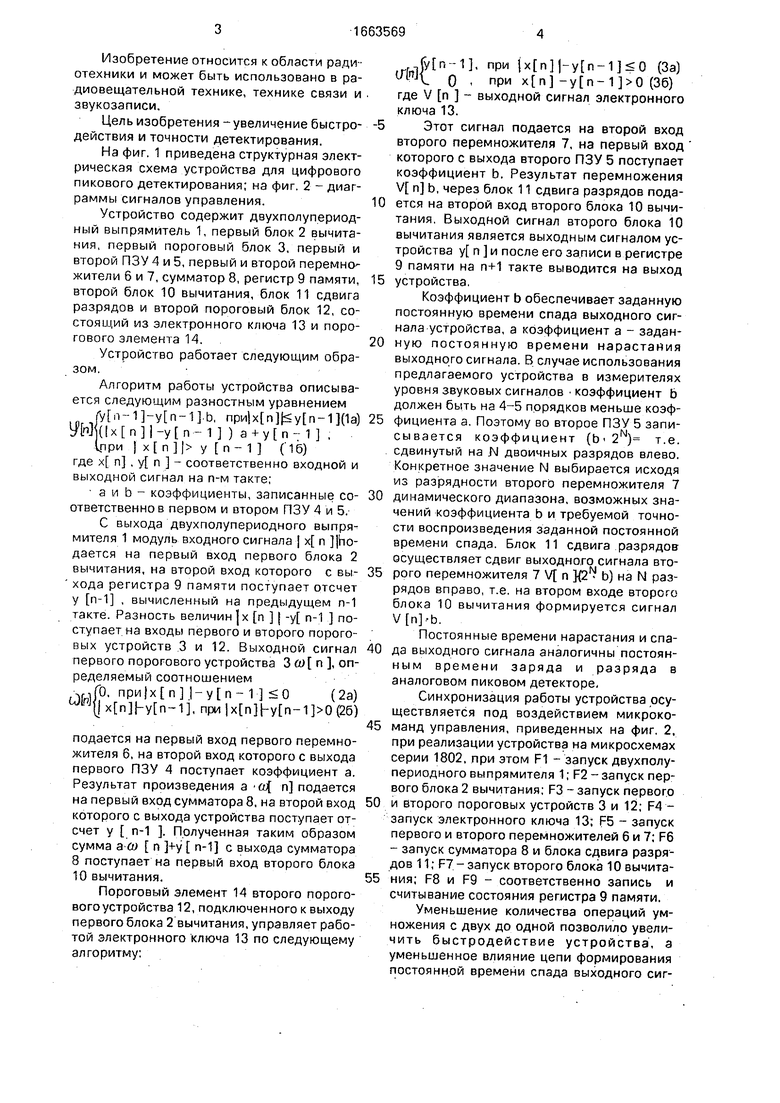

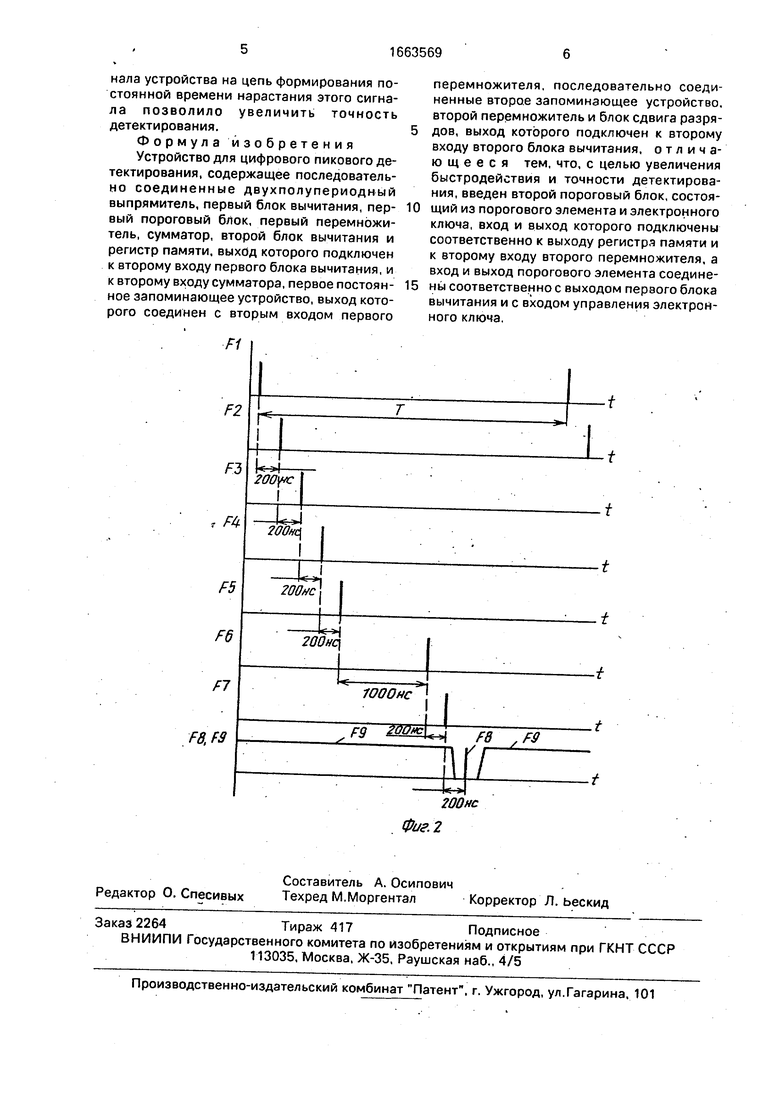

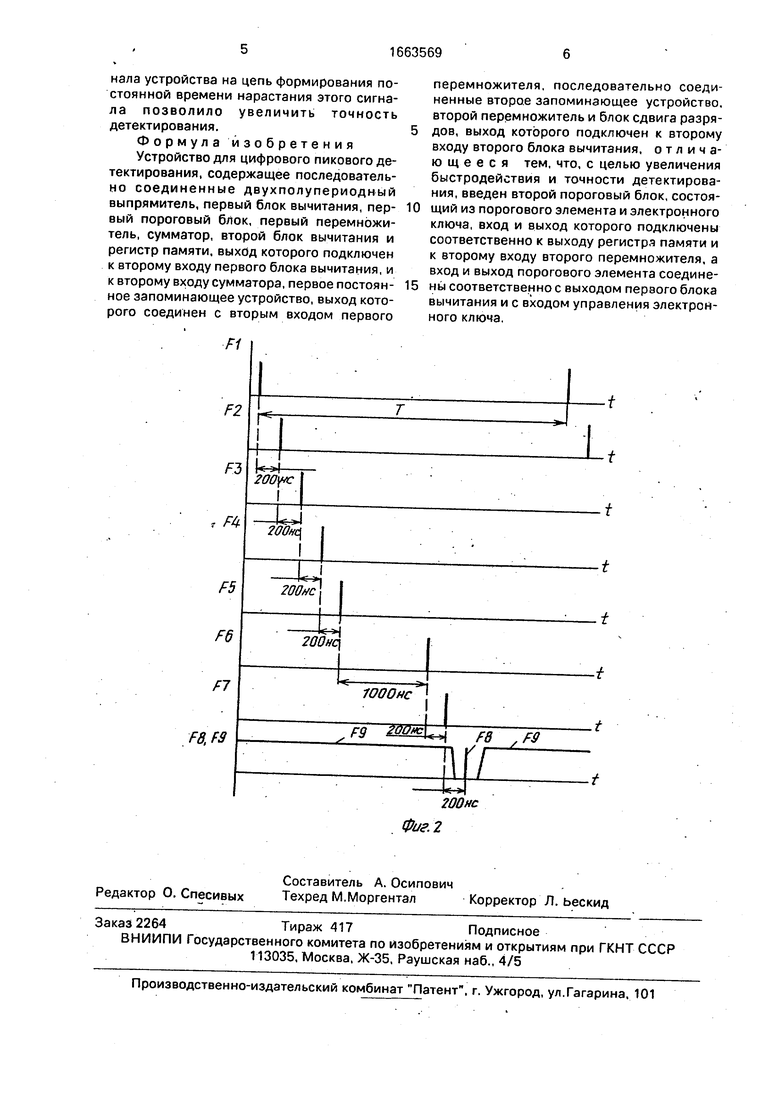

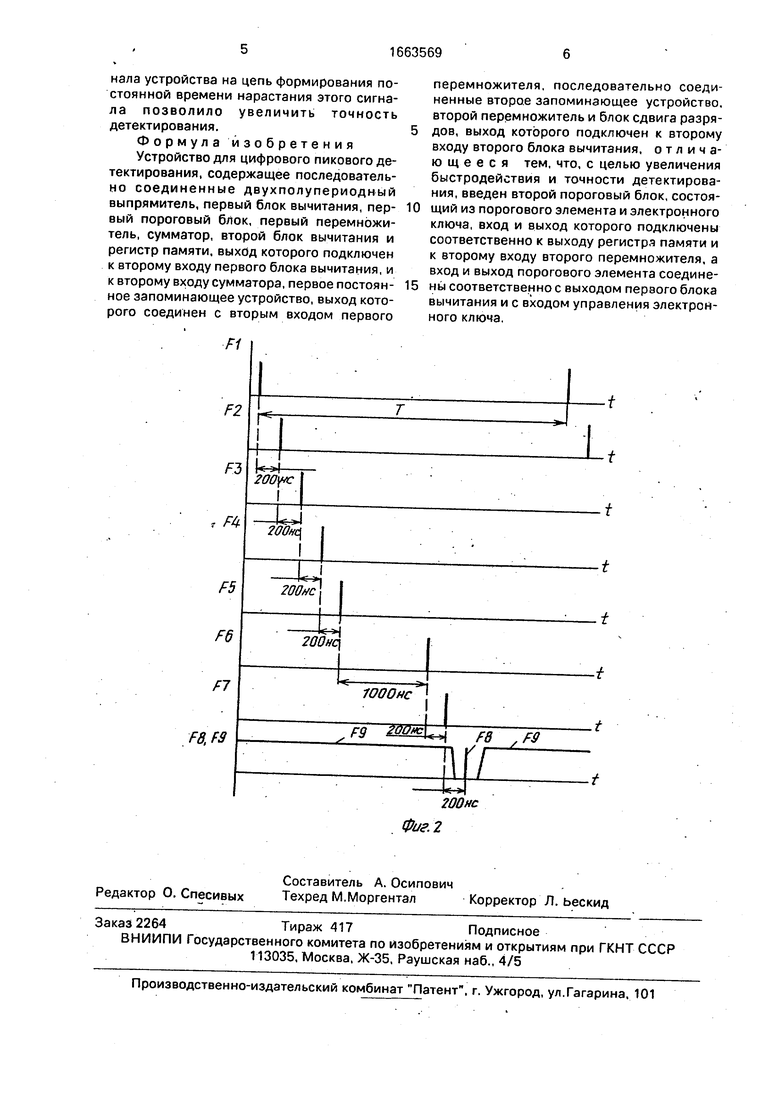

На фиг. 1 приведена структурная электрическая схема устройства для цифрового пикового детектирования; на фиг. 2 - диаграммы сигналов управления.

Устройство содержит двухполупериод- ный выпрямитель 1, первый блок 2 вычитания, первый пороговый блок 3, первый и второй ПЗУ 4 и 5, первый и второй перемножители 6 и 7, сумматор 8, регистр 9 памяти, второй блок 10 вычитания, блок 11 сдвига разрядов и второй пороговый блок 12, состоящий из электронного ключа 13 и порогового элемента 14.

Устройство работает следующим образом

Алгоритм работы устройства описывается следующим разностным уравнением

. при)(1а) УЫ( ) а + .

1лри | у п-1 (16) где х п , у п 3 - соответственно входной и выходной сигнал на n-м такте;

а и b - коэффициенты, записанные соответственное первом и втором ПЗУ 4 и 5.

С выхода двухполупериодного выпрямителя 1 модуль входного сигнала | х п Подается на первый вход первого блока 2 вычитания, на второй вход которого с выхода регистра 9 памяти поступает отсчет у п-1 , вычисленный на предыдущем п-1 такте. Разность величин | х п | -у п-1 поступает на входы первого и второго пороговых устройств 3 и 12. Выходной сигнал первого порогового устройства 3 со п 3, определяемый соотношением

ГО. при|х п 1 3 0(2а)

сОЙ

х пЗЬ-у п-13,при|х пЗЫп-1 0(2б)

подается на первый вход первого перемножителя 6, на второй вход которого с выхода первого ПЗУ 4 поступает коэффициент а. Результат произведения а № пЗ подается на первый вход сумматора 8, на второй вход которого с выхода устройства поступает отсчет у п-1 . Полученная таким образом сумма а (о п 3+у п-1 с выхода сумматора 8 поступает на первый вход второго блока 10 вычитания.

Пороговый элемент 14 второго порогового устройства 12, подключенного к выходу первого блока 2 вычитания, управляет работой электронного ключа 13 по следующему алгоритму:

(, при (За) №JC 0 . при (36) где V п 1 - выходной сигнал электронного ключа 13.

Этот сигнал подается на второй вход второго перемножителя 7, на первый вход которого с выхода второго ПЗУ 5 поступает коэффициент Ь. Результат перемножения Vf n b, через блок 11 сдвига разрядов пода0 ется на второй вход второго блока 10 вычитания Выходной сигнал второго блока 10 вычитания является выходным сигналом устройства у п 3 и после его записи в регистре 9 памяти на п+1 такте выводится на выход

5 устройства

Коэффициент b обеспечивает заданную постоянную времени спада выходного сигнала устройства, а коэффициент а - задан0 ную постоянную времени нарастания выходного сигнала. В случае использования предлагаемого устройства в измерителях уровня звуковых сигналов коэффициент b должен быть на 4-5 порядков меньше коэф5 фициента а. Поэтому во второе ПЗУ 5 запи- сывается коэффициент (Ь 2 ) т.е. сдвинутый на N двоичных разрядов влево. Конкретное значение N выбирается исходя из разрядности второго перемножителя 7

0 динамического диапазона, возможных значений коэффициента b и требуемой точности воспроизведения заданной постоянной времени спада. Блок 11 сдвига разрядов осуществляет сдвиг выходного сигнала вто5 рого перемножителя 7 V п {2 Ь) на N разрядов вправо, т.е. на втором входе второго блока 10 вычитания формируется сигнал

Постоянные времени нарастания и спа0 да выходного сигнала аналогичны постоянным времени заряда и разряда в аналоговом пиковом детекторе,

Синхронизация работы устройства осуществляется под воздействием микроко5 манд управления, приведенных на фиг. 2, при реализации устройства на микросхемах серии 1802, при этом F1 - запуск двухполупериодного выпрямителя 1; F2 - запуск первого блока 2 вычитания; F3 - запуск первого

0 и второго пороговых устройств 3 и 12; F4 - запуск электронного ключа 13; F5 - запуск первого и второго перемножителей 6 и 7; F6 - запуск сумматора 8 и блока сдвига разрядов 11; F7 - запуск второго блока 10 вычита5 ния; F8 и F9 - соответственно запись и считывание состояния регистра 9 памяти.

Уменьшение количества операций умножения с двух до одной позволило увеличить быстродействие устройства, а уменьшенное влияние цепи формирования постоянной времени спада выходного сигнала устройства на цепь формирования постоянной времени нарастания этого сигнала позволило увеличить точность детектирования.

Формула изобретения Устройство для цифрового пикового детектирования, содержащее последовательно соединенные двухполупериодный выпрямитель, первый блок вычитания, первый пороговый блок, первый перемножитель, сумматор, второй блок вычитания и регистр памяти, выход которого подключен к второму входу первого блока вычитания, и к второму входу сумматора, первое постоянное запоминающее устройство, выход которого соединен с вторым входом первого

0

5

перемножителя, последовательно соединенные второе запоминающее устройство, второй перемножитель и блок сдвига разрядов, выход которого подключен к второму входу второго блока вычитания, отличающееся тем, что, с целью увеличения быстродействия и точности детектирования, введен второй пороговый блок, состоящий из порогового элемента и электронного ключа, вход и выход которого подключены соответственно к выходу регистра памяти и к второму входу второго перемножителя, а вход и выход порогового элемента соединены соответственно с выходом первого блока вычитания и с входом управления электронного ключа.

| IAES, 1984, vol | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

| Способ амидирования жидких сульфохлоридов ароматического ряда | 1921 |

|

SU316A1 |

Авторы

Даты

1991-07-15—Публикация

1989-02-13—Подача