о о ел со

VI

VI

Изобретение относится к вычислительной технике, электросвязи и может использоваться в измерительных системах для вычисления спектральных характеристик сигнала, а также в качестве фильтра.

Целью изобретения является расширение области применения устройства за счет разложения исходной функции в любом базисе.

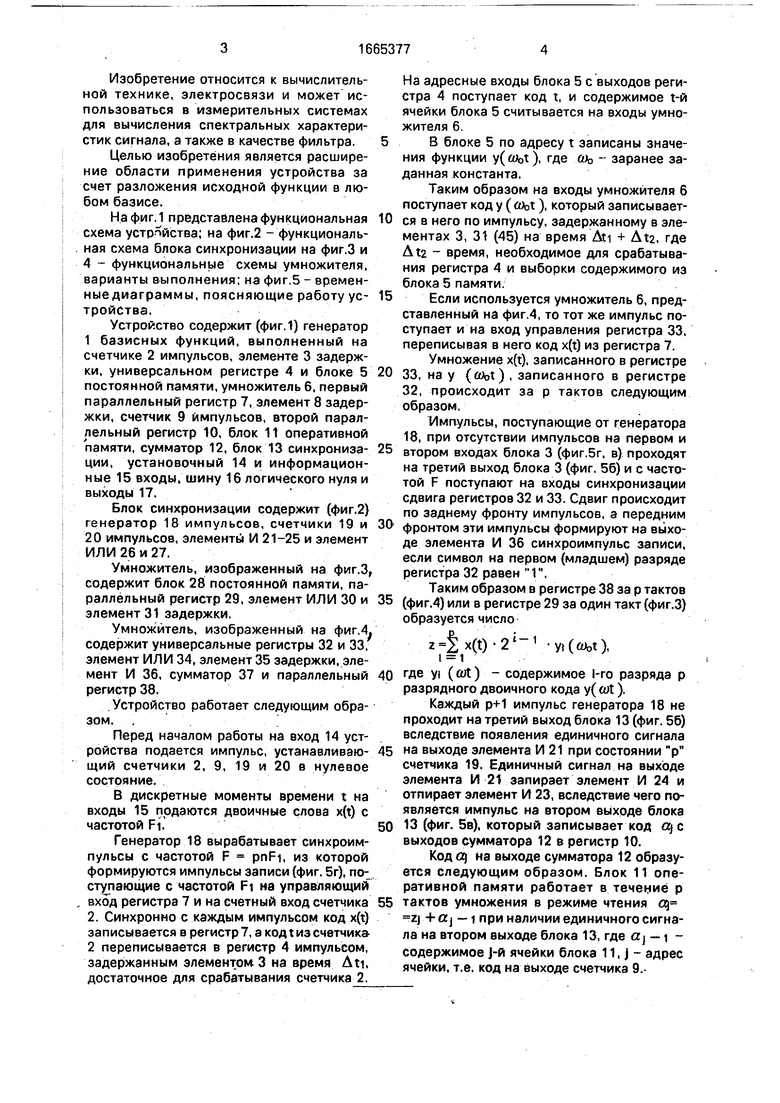

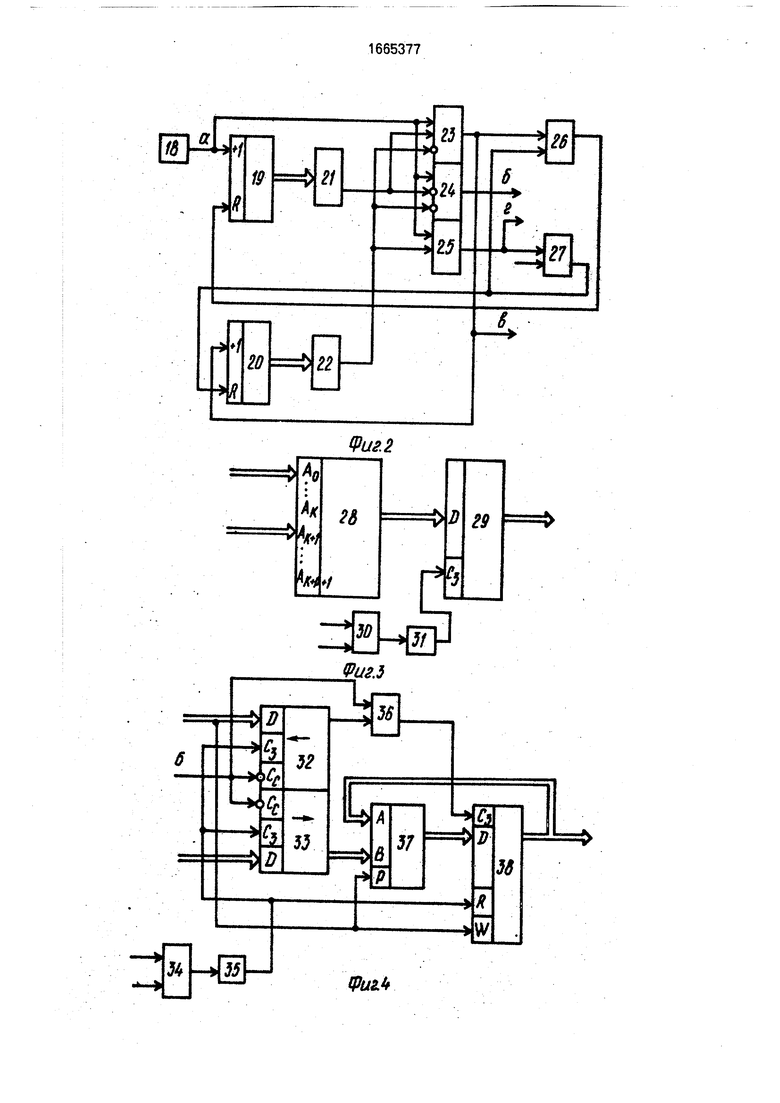

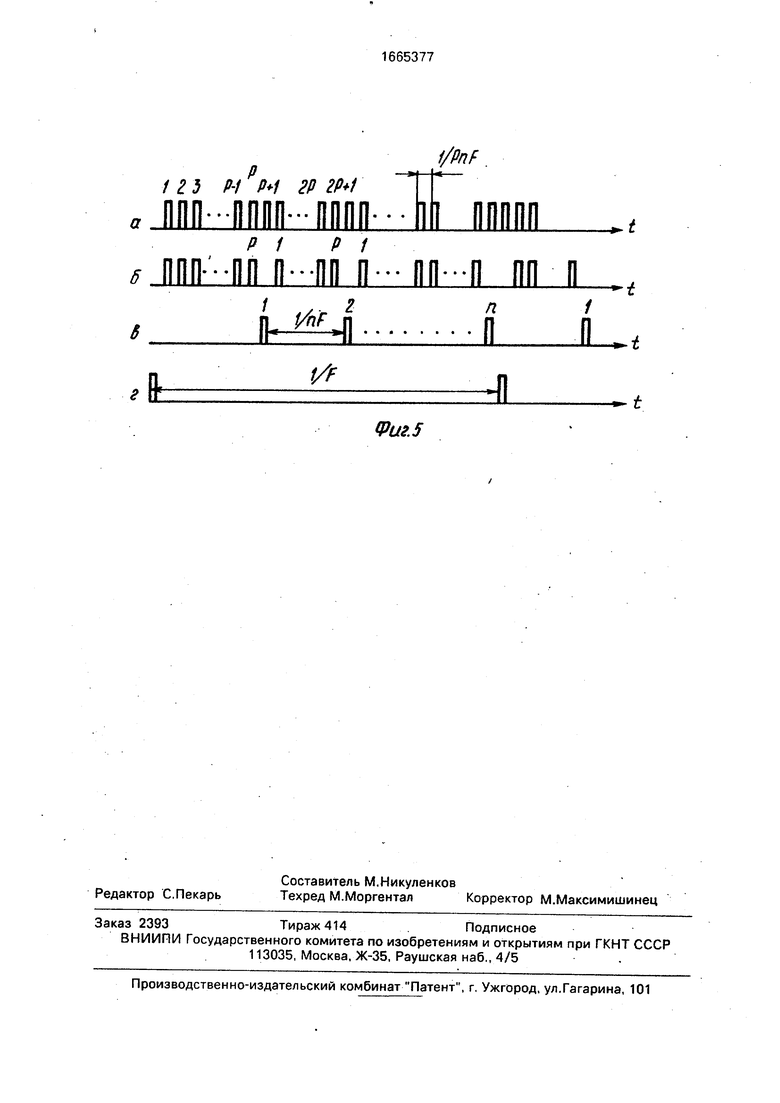

На фиг.1 представлена функциональная схема устройства; на фиг.2 - функциональная схема блока синхронизации на фиг.З и 4 - функциональные схемы умножителя, варианты выполнения; на фиг.5 - временные диаграммы, поясняющие работу устройства.

Устройство содержит (фиг.1) генератор 1 базисных функций, выполненный на счетчике 2 импульсов, элементе 3 задержки, универсальном регистре 4 и блоке 5 постоянной памяти, умножитель б, первый параллельный регистр 7, элемент 8 задержки, счетчик 9 импульсов, второй параллельный регистр 10, блок 11 оперативной памяти, сумматор 12, блок 13 синхронизации, установочный 14 и информационные 15 входы, шину 16 логического нуля и выходы 17.

Блок синхронизации содержит (фиг.2) генератор 18 импульсов, счетчики 19 и 20 импульсов, элементы И 21-25 и элемент ИЛИ 26 и 27.

Умножитель, изображенный на фиг.З, содержит блок 28 постоянной памяти, параллельный регистр 29, элемент ИЛИ 30 и элемент 31 задержки,

Умножитель, изображенный на фиг,4. содержит универсальные регистры 32 и 33, элемент ИЛИ 34, элемент 35 задержки, элемент И 36, сумматор 37 и параллельный регистр 38.

Устройство работает следующим образом. .

Перед началом работы на вход 14 устройства подается импульс, устанавливающий счетчики 2, 9, 19 и 20 в нулевое состояние.

В дискретные моменты времени t на входы 15 подаются двоичные слова x(t) с частотой Fi.

Генератор 18 вырабатывает синхроимпульсы с частотой F pnFi, из которой формируются импульсы записи {фиг. 5г), по- ступающие с частотой FI на управляющий вход регистра 7 и на счетный вход счетчика 2. Синхронно с каждым импульсом код x(t) записывается в регистр, а код t из счетчика 2 переписывается в регистр 4 импульсом, задержанным элементом 3 на время Ati, достаточное для срабатывания счетчика 2.

На адресные входы блока 5 с выходов регистра 4 поступает код t, и содержимое t-й ячейки блока 5 считывается на входы умножителя 6.

В блоке 5 по адресу t записаны значения функции y(ttfot ), где (Оо - заранее заданная константа.

Таким образом на входы умножителя 6 поступает код у ( оы ), который записывается в него по импульсу, задержанному в элементах 3, 31 (45) на время Ati + Ata, где At2 - время, необходимое для срабатывания регистра 4 и выборки содержимого из блока 5 памяти.

Если используется умножитель 6, представленный на фиг.4, то тот же импульс поступает и на вход управления регистра 33, переписывая в него код x(t) из регистра 7. Умножение x(t), записанного в регистре

33, на у (ftfet) , записанного в регистре 32, происходит за р тактов следующим образом.

Импульсы, поступающие от генератора 18, при отсутствии импульсов на первом и

втором входах блока 3 (фиг.бг, в) проходят на третий выход блока 3 (фиг. 56) и с частотой F поступают на входы синхронизации сдвига регистров 32 и 33. Сдвиг происходит по заднему фронту импульсов, а передним

фронтом эти импульсы формируют на выходе элемента И 36 синхроимпульс записи, если символ на первом (младшем) разряде регистра 32 равен 1.

Таким образом в регистре 38 за р тактов

(фиг.4) или в регистре 29 за один такт (фиг.З) образуется число

z-ixCt) -1 -yj(fflbt), i 1

где yt (ftrt) - содержимое 1-го разряда р разрядного двоичного кода y(),

Каждый р+1 импульс генератора 18 не проходит на третий выход блока 13 (фиг. 56) вследствие появления единичного сигнала

на выходе элемента И 21 при состоянии р счетчика 19. Единичный сигнал на выходе элемента И 21 запирает элемент И 24 и отпирает элемент И 23, вследствие чего появляется импульс на втором выходе блока

0 13 (фиг. 5в), который записывает код Щ с выходов сумматора 12 в регистр 10.

Код О) на выходе сумматора 12 образуется следующим образом. Блок 11 оперативной памяти работает в течение р

5 тактов умножения в режиме чтения cq zj + aj - i при наличии единичного сигнала на втором выходе блока 13, где «j - i - содержимое j-й ячейки блока 11, j - адрес ячейки, т.е. код на выходе счетчика 9.К

Записав своим передним фронтом код а в регистр 10, сигнал с второго выхода блока 13 переводит блок 11 в режим записи и записывает код а в j-ю ячейку блока 11, т.е. заменяет «j - t в этой ячейке на а.

Задержавшись элементом 8 на время, достаточное для выполнения записи в блок 11, импульс с второго выхода блока 13 прибавляет своим передним фронтом единицу к содержимому счетчика 9, одновременно сдвигая содержимое регистра 4 на один разряд в сторону Старшего разряда, Таким образом на адресный вход блока 5 поступает код tj 2tj-i, т.е. при формировании j-ro импульса на втором выходе блока 13 (после появления импульса на первом выходе блока 13) на первые входы умножителя 6 поступает число

1 у( Wol I

1осле умножения на выходах умножи-

теля 6 появится число

(t)-y(2J 1 r-ftfet).

I Юсле поступления Т-импульсов с первого выхода блока 13 в j-й ячейки блока 11 будет содержаться число

«j(T) S x(t)-y(2j-1 -aw).

t 1

которое представляет коэффициенты разложения функции x(t) в базисе функции

I 1

уш в точках щ 2 . Например, если y(t) cos ал, то

x(t)-cos(2-1 -оы)

t 1

и представляет собой коэффициенты гармонического разложения.

В качестве y(t) можно выбрать любую базисную функцию. Устройство для вычисления спектральных коэффициентов для различных базисных функций будут различаться только содержимым блока 5.

Таким образом устройство позволяет вычислить коэффициенты разложения в разных базисах либо в разных частотных диапазонах одной базисной функции, либо разного числа коэффициентов разложения путем подключения различных выходов счетчиков 19 и 20 к входам элементов И 21 и 22.,

.Формула изобретения

Устройство для вычисления обобщен- ного спектра, содержащее умножитель, выходы которого соединены с одноименными

,.

первыми информационными входами сум матора, и генератор базисных функций, выполненный на счетчике, установочный вход которого является установочным входом ус,.

5

20

25

30

35

404550

55

тройства, отличающееся тем, что, с целью расширения области применения устройства путем разложения исходной функции в любом базисе, в него введены регистры, элемент задержки, счетчик, блок оперативной памяти, блок синхронизации, шина логического нуля и в генератор введены элемент задержки, блок постоянной памяти и регистр, выходы которого соединены с одноименными входами блока постоянной памяти, выходы счетчика и элемента задержки соединены соответственно с одноименными первыми информационными и управляющим входами регистра, генератора и первым управляющим входом умножителя, второй информационный вход регистра генератора подключен к одному из его выходов, первый установочный вход счетчика объединен с входом блока синхронизации и подключен к установочному входу устройства, первый выход блока синхронизации соединен со счетным входом счетчика генератора,входом элемента задержки генератора, управляющим входом первого регистра и с вторым установочным входом счетчика, выходы блока постоянной памяти генератора соединены с одноименными первыми информационными входами умножителя, второй выход блока синхронизации соединен с управляющими входами блока оперативной памяти, второго регистра и входом элемента задержки, выход которого соединен с тактовым входом регистра генератора, вторым управляющим входом умножителя и счетным входом счетчика, выходы которого соединены с одноименными адресными входами блока оперативной памяти, третьи информационные входы регистра генератора подключены к шине логического нуля, информационные входы первого регистра являются информационными входами устройства, выходы первого pernQTpa соединены с одноименными вторыми информационными входами умножителя, третий выход блока синхронизации соединен с тактовым входом умножителя, вход Перенос сумматора подключен к одному из выходов блока постоянной памяти генератора, выходы сумматора соединены с одноименными информационными входами второго регистра, выходы которого соединены с одноименными информационными входами блока оперативной памяти, выходы которого соединены с одноименными вторыми информационными входами сумматора и являются выходами устройства.

t/faF.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| Цифровой анализатор спектра в ортогональном базисе | 1983 |

|

SU1124326A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| Устройство для реализации быстрых преобразований | 1986 |

|

SU1416981A1 |

| ГЕНЕРАТОР СТОХАСТИЧЕСКИХ ОРТОГОНАЛЬНЫХ КОДОВ | 2016 |

|

RU2615322C1 |

| Цифровой функциональный генератор | 1985 |

|

SU1282104A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СТОХАСТИЧЕСКИХ ОРТОГОНАЛЬНЫХ КОДОВ | 2021 |

|

RU2773107C1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для вычисления функций | 1987 |

|

SU1472901A1 |

| Устройство для сжатия информации | 1986 |

|

SU1324047A1 |

Изобретение относится к вычислительной технике, электросвязи и может использоваться в измерительных системах. Цель изобретения - расширение области применения устройства путем разложения исходной функции в любом базисе. Устройство содержит генератор 1 базисных функций, счетчики 2, 9 импульсов, элементы 3, 8 задержки, регистры 4, 7, 10, блок 5 постоянной памяти, умножитель 6, блок 11 оперативной памяти, сумматор 12 и блок 13 синхронизации. 5 ил.

Фиг. 5

| Многоканальный корреляционно-спектральный анализатор | 1974 |

|

SU524182A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сжатия информации | 1983 |

|

SU1187196A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1991-07-23—Публикация

1989-07-17—Подача