Изобретение относится к электросвязи, может быть использовано в цифровых коммутационных системах и является усовершенствованием известного устройства по авт.св. № 1401639.

Цель изобретения - повышение точности контроля.

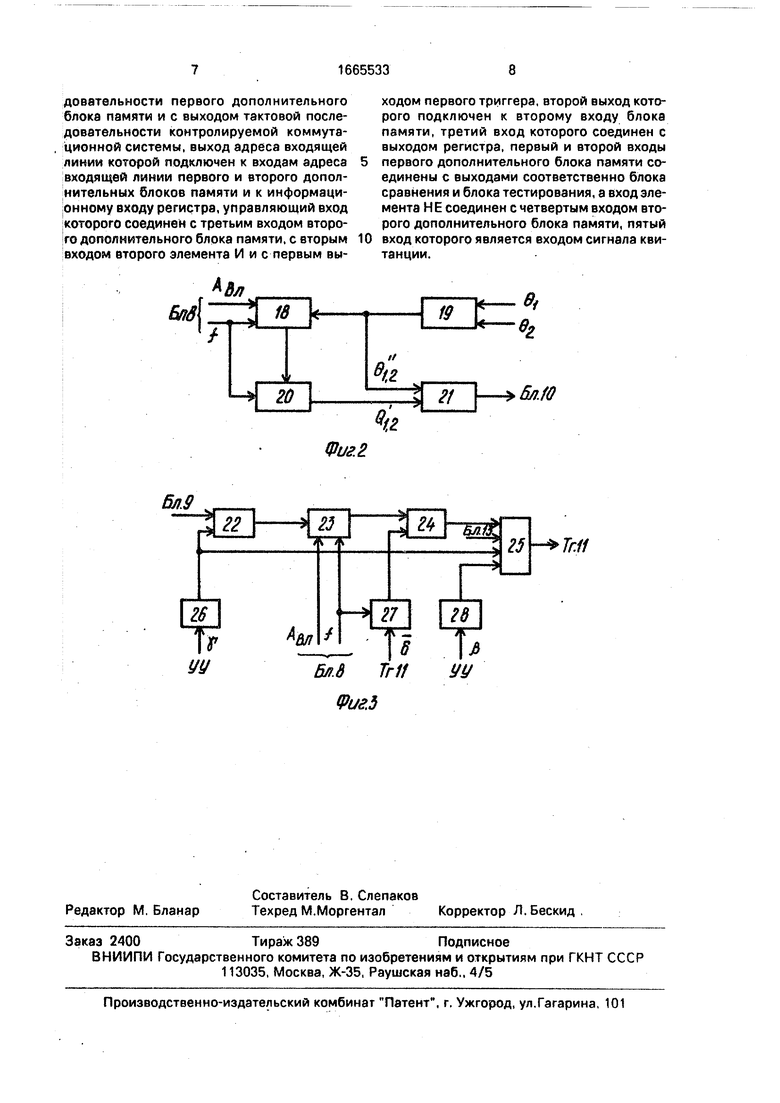

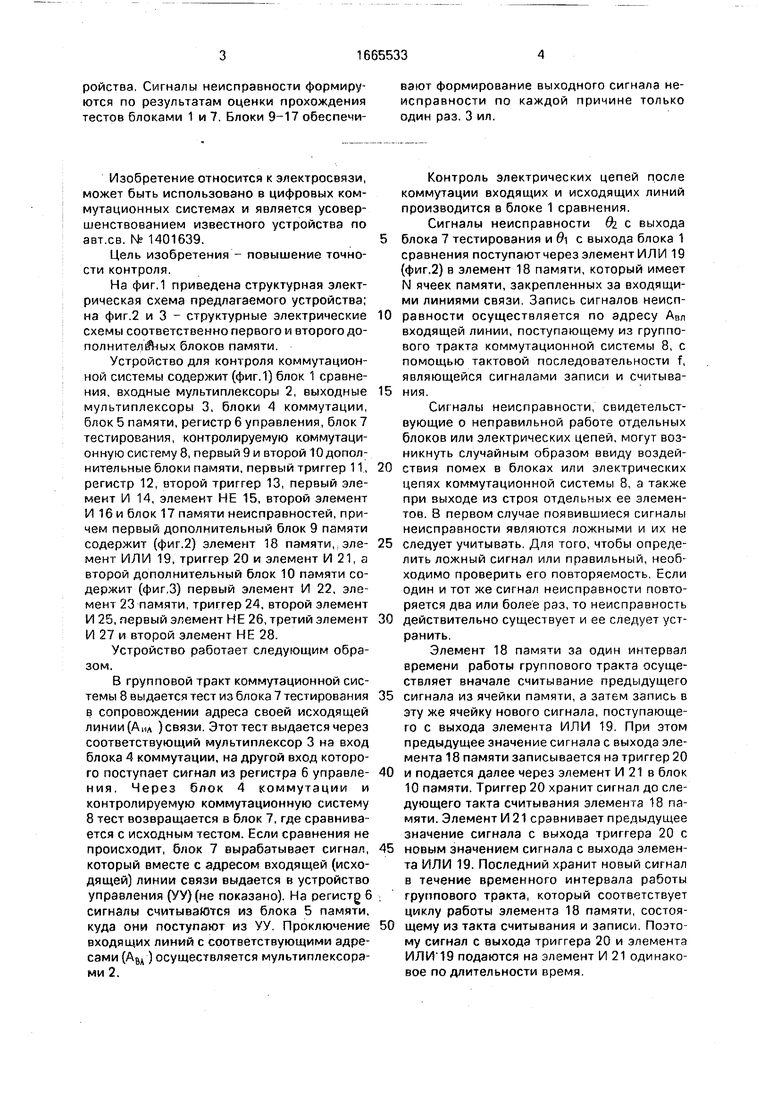

На фиг.1 приведена структурная электрическая схема предлагаемого устройства; на фиг.2 и 3 - структурные электрические схемы соответственно первого и второго до- полнителйных блоков памяти.

Устройство для контроля коммутационной системы содержит (фиг.1) блок 1 сравнения, входные мультиплексоры 2, выходные мультиплексоры 3, блоки 4 коммутации, блок 5 памяти, регистр 6 управления, блок 7 тестирования, контролируемую коммутационную систему 8, первый 9 и второй 10 дополнительные блоки памяти, первый триггер 11, регистр 12, второй триггер 13, первый элемент И 14, элемент НЕ 15, второй элемент И 16 и блок 17 памяти неисправностей, причем первый дополнительный блок 9 памяти содержит (фиг.2) элемент 18 памяти, эле- мент ИЛИ 19, триггер 20 и элемент И 21, а второй дополнительный блок 10 памяти содержит (фиг.З) первый элемент И 22, элемент 23 памяти, триггер 24, второй элемент И 25, первый элемент НЕ 26, третий элемент И 27 и второй элемент НЕ 28.

Устройство работает следующим образом.

В групповой тракт коммутационной системы 8 выдается тест из блока 7 тестирования в сопровождении адреса своей исходящей линии (А НА ) связи. Этот тест выдается через соответствующий мультиплексор 3 на вход блока 4 коммутации, на другой вход которого поступает сигнал из регистра 6 управле- ния. Через блок 4 коммутации и контролируемую коммутационную систему 8 тест возвращается в блок 7, где сравнивается с исходным тестом. Если сравнения не происходит, блок 7 вырабатывает сигнал, который вместе с адресом входящей (исходящей) линии связи выдается в устройство управления (УУ)(не показано). На регистр 6 сигналы считываются из блока 5 памяти, куда они поступают из УУ. Проключение входящих линий с соответствующими адресами (АВА) осуществляется мультиплексорами 2.

Контроль электрических цепей после коммутации входящих и исходящих линий производится в блоке 1 сравнения.

Сигналы неисправности & с выхода блока 7 тестирования и В с выхода блока 1 сравнения поступают через элемент ИЛИ 19 (фиг,2) в элемент 18 памяти, который имеет N ячеек памяти, закрепленных за входящими линиями связи. Запись сигналов неисправности осуществляется по адресу АВл входящей линии, поступающему из группового тракта коммутационной системы 8, с помощью тактовой последовательности f, являющейся сигналами записи и считывания.

Сигналы неисправности, свидетельствующие о неправильной работе отдельных блоков или электрических цепей, могут возникнуть случайным образом ввиду воздействия помех в блоках или электрических цепях коммутационной системы 8, а также при выходе из строя отдельных ее элементов. 8 первом случае появившиеся сигналы неисправности являются ложными и их не следует учитывать. Для того, чтобы определить ложный сигнал или правильный, необходимо проверить его повторяемость. Если один и тот же сигнал неисправности повторяется два или более раз, то неисправность действительно существует и ее следует устранить,

Элемент 18 памяти за один интервал времени работы группового тракта осуществляет вначале считывание предыдущего сигнала из ячейки памяти, а затем запись в эту же ячейку нового сигнала, поступающего с выхода элемента ИЛИ 19. При этом предыдущее значение сигнала с выхода элемента 18 памяти записывается на триггер 20 и подается далее через элемент И 21 в блок 10 памяти. Триггер 20 хранит сигнал до следующего такта считывания элемента 18 памяти. Элемент И 21 сравнивает предыдущее значение сигнала с выхода триггера 20 с новым значением сигнала с выхода элемента ИЛИ 19. Последний хранит новый сигнал в течение временного интервала работы группового тракта, который соответствует циклу работы элемента 18 памяти, состоящему из такта считывания и записи. Поэтому сигнал с выхода триггера 20 и элемента ИЛИ 19 подаются на элемент И 21 одинаковое по длительности время.

Если сигналы неисправности совпадают, то неисправность является повторяющейся, а сигнал является истинным, поэтому он проходит через элементы И 21 и 22 (фиг.З) и записывается в элемент 23 памяти по построению и функционированию аналогичный элементу 18 памяти. Таким образом, в элементе 23 памяти записываются истинные сигналы неисправности, которые затем считываются, записываются на триггер 24 с помощью элемента И 22, далее проходят через элемент И 25 и поступают на первый триггер 11 (фиг.1), который обеспечивает выдачу сигналов неисправности в УУ. Сигналы неисправности выдаются в УУ вместе с адресом Авл, поступающим из регистра 12. Запись адреса Авл на регистр 12 осуществляется из группового тракта коммутационной системы с помощью первого триггера 11. После записи на первый триггер 11 сигнала неисправности с его левого (нулевого) плеча подается сигнал д 0 на регистр 12, обеспечивая запрет на поступление в этот регистр новых адресов А , на элементы И 22 и 14, запрещая переключение триггеров 24 и 13, а с его правого (единичного) плеча выдается сигнал а 1 на вход блока 17 памяти неисправностей и на выход устройства. Записанный на регистр 12 адрес А поступает на блок 17 памяти неисправностей и обеспечивает запись выдаваемых в УУ сигналов неиспр авности в ячейки памяти блока 17. Сигнал 6 0 поступает также через второй элемент И 16 в блок 17 памяти неисправностей в виде сигнала записи, обеспечивая запись выдаваемого в УУ сигнала неисправности. Блок 17 памяти неисправностей обеспечивает хранение сигналов неисправности, выданных в УУ.

Так как первый триггер 11 запрещает изменение состояний триггеров 24 и 13, то единичное состояние первого тоиггера 11 сохраняется до тех пор, пока УУ примет выдаваемый сигнал неисправности и выдает после его принятия сигнал квитанции/3 1, который проходит через элемент НЕ 28 и в виде сигнала /3 0 проходит далее через элемент I/I 25 и возвращает первый триггер 11 в нулевое состояние. При этом сигнал д 1, а сигнал (. Сигнал открывает элементы И 22 и 14, обеспечивая подачу импульсов f на управляющие входы триггеров 24 и 13, которые начинают принимать сигналы неисправности из элементов 23 и 17 памяти.

Сигнал 6 0 поступает в блок 17 памяти неисправностей в виде информации, которая Не записывается в этот блок так как с помощью сигналов 6 1 и 0 Ос выхода

второго элемента И 16 поступает сигнал считывания, равный 1, на блок 17, т.е. блок 17 памяти неисправностей все время находится в состоянии считывания, обеспечивая

считывание сигналов неисправности с помощью адресов АВл, поступающих через регистр 12. Последний состоит из D-триггеров (типа защелка), на управляющие входы которых подается сигнал . Считываемые

из ячеек памяти блока 17 сигналы неисправности поступают на второй триггер 13 и поочередно записываются в него с помощью тактов f. Эти сигналы с нулевого плеча второго триггера 13 подаются далее на элемент

И 25. При этом, если на второй триггер 13 записан сигнал неисправности, то он инвертирует сигнал, Это озна 1эет, что если сигнал неисправности уже вид-н в УУ, то второй раз его выдавать не следует, чтобы уменьшить нагрузку на УУ. Поэтому с помощью сигнала с выхода второго триггера 13 запрещается прохождение на первый триггер 11 через элемент И 25 повторного сигнала неисправности из элемента 23 памяти через

триггер 24.

Таким образом, в УУ выдаются сигналы неисправности только один раз и после выдачи записываются в блок 17 памяти неисправностей.

С помощью полученных сигналов неисправности УУ обеспечивает тереключение неисправного оборудования на резерв и за- мену этого оборудования. Из УУ поступает сигнал у 1, который с помощью элементов

НЕ 26 и 15 обеспечивает обнуление элементов 23 и 17 памяти. При этом первый триггер 11 остается в нулевом состоянии, как сигналом у 0 с выхода элемента НЕ 26 закрывается элемент И 25. После обнуления

устройство для контроля коммутационной системы снова начинает накапливать и выдавать в УУ сигналы неисправности. Формула изобретения Устройство для контроля коммутационной системы по авт.св. № 1401639, отличающееся тем, что, с целью повышения точности контроля, введены регистр, последовательно соединенные первый и второй дополнительные блоки памяти, первый

триггер, первый элемент И и второй триггер и последовательно соединенные элемент НЕ, второй элемент И и блок памяти неисправностей, выход которого подключен к второму входу блока второго триггера, выход

которого подключен к второму входу второго дополнительного блока памяти, вход тактовой последовательности которого соединен с вторыми входами первого элемента И и первого триггера, с входом тактовой последовательности первого дополнительного блока памяти и с выходом тактовой последовательности контролируемой коммутационной системы, выход адреса входящей линии которой подключен к входам адреса входящей линии первого и второго дополнительных блоков памяти и к информационному входу регистра, управляющий вход которого соединен с третьим входом второго дополнительного блока памяти, с вторым входом второго элемента И и с первым вы0

ходом первого триггера, второй выход которого подключен к второму входу блока памяти, третий вход которого соединен с выходом регистра, первый и второй входы первого дополнительного блока памяти соединены с выходами соответственно блока сравнения и блока тестирования, а вход элемента НЕ соединен с четвертым входом второго дополнительного блока памяти, пятый вход которого является входом сигнала квитанции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля коммутационной системы | 1986 |

|

SU1401639A1 |

| Многомодульная коммутационная система для асинхронных цифровых сигналов | 1986 |

|

SU1394459A1 |

| Устройство сопряжения разноскоростных асинхронных цифровых сигналов | 1988 |

|

SU1667266A1 |

| Устройство для приема цифровых сигналов | 1989 |

|

SU1646065A1 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1275549A1 |

| Устройство для приема цифровых сигналов | 1986 |

|

SU1394444A1 |

| Устройство временной коммутации асинхронных цифровых сигналов | 1989 |

|

SU1700762A1 |

| Устройство ввода информации | 1986 |

|

SU1417015A1 |

| Устройство сопряжения асинхронных разноскоростных цифровых сигналов | 1990 |

|

SU1755386A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение точности контроля. Устройство содержит блок 1 сравнения, входные мультиплексоры 2, выходные мультиплексоры 3, блоки 4 коммутации, блоки 5, 9 и 10 памяти, регистр 6 управления, блок 7 тестирования, триггеры 11, 13, регистр 12, элементы И 14 и 16, элемент НЕ 15 и блок 17 памяти неисправностей. Контролируемая коммутационная система 8 вырабатывает тактовую последовательность, синхронизирующую работу всех блоков устройства. Сигналы неисправности формируются по результатам оценки прохождения тестов блоками 1 и 7. Блоки 9 - 17 обеспечивают формирование выходного сигнала неисправности по каждой причине только один раз. 3 ил.

Ml /

Ьл

Фиг.2

| Устройство для контроля коммутационной системы | 1986 |

|

SU1401639A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-07-23—Публикация

1989-02-16—Подача