э

ч ел ел

N

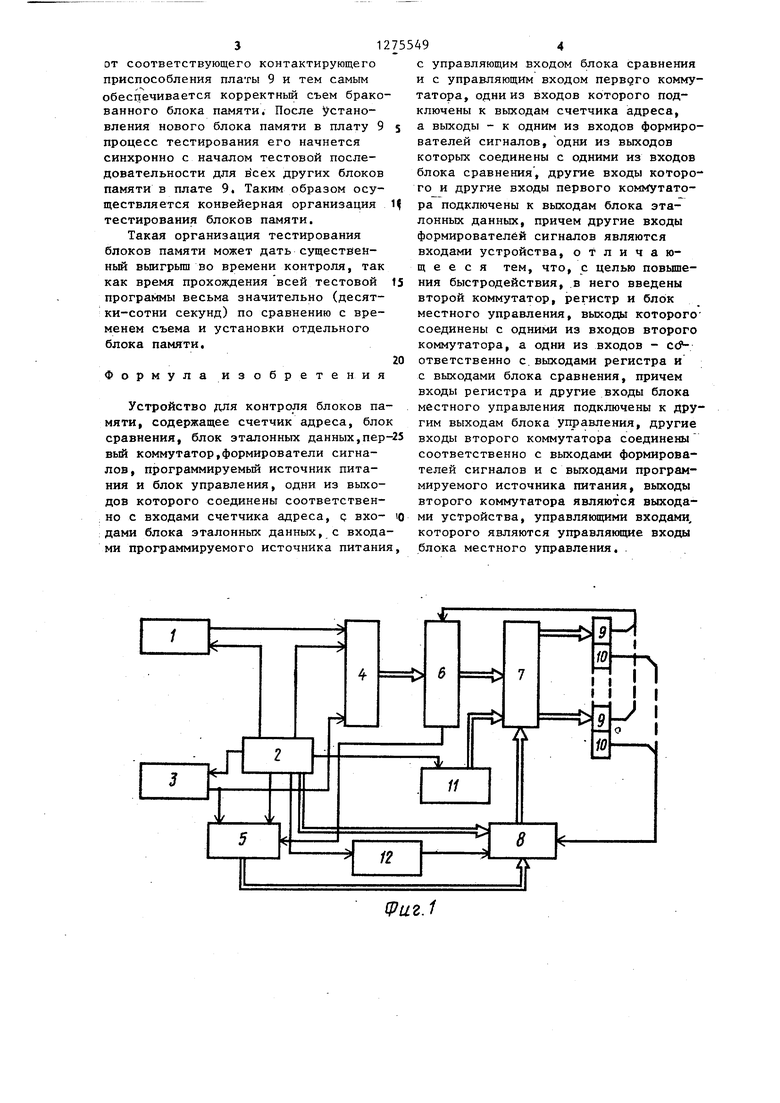

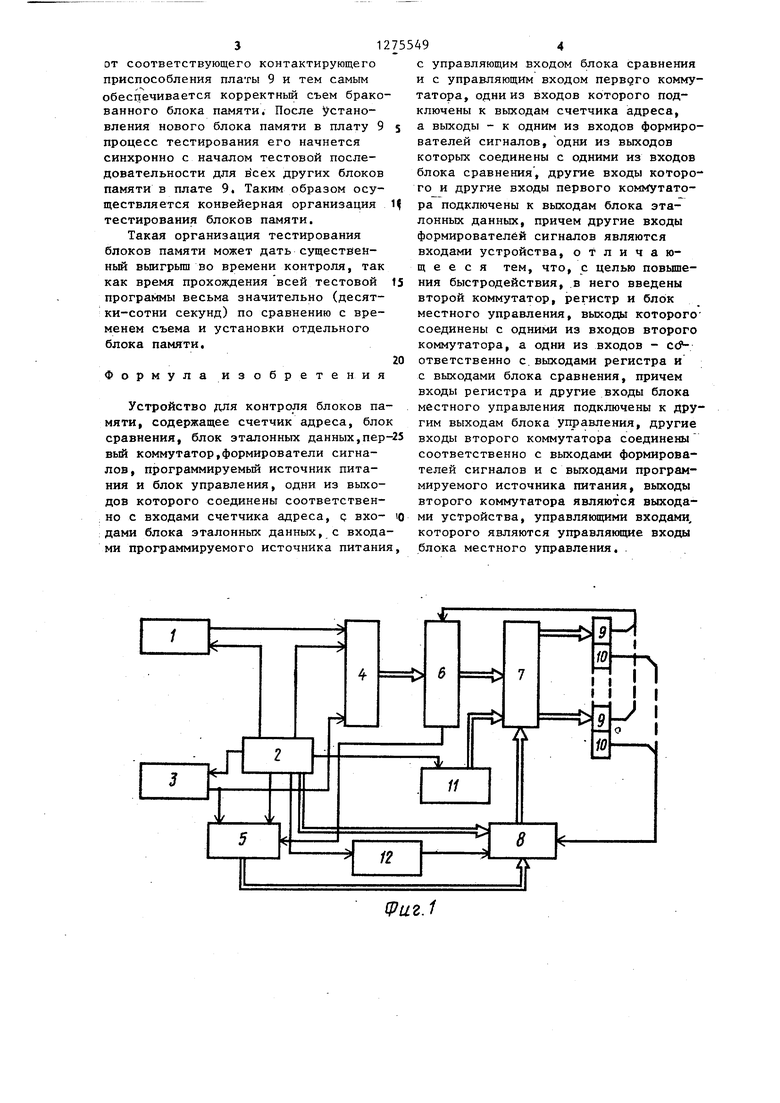

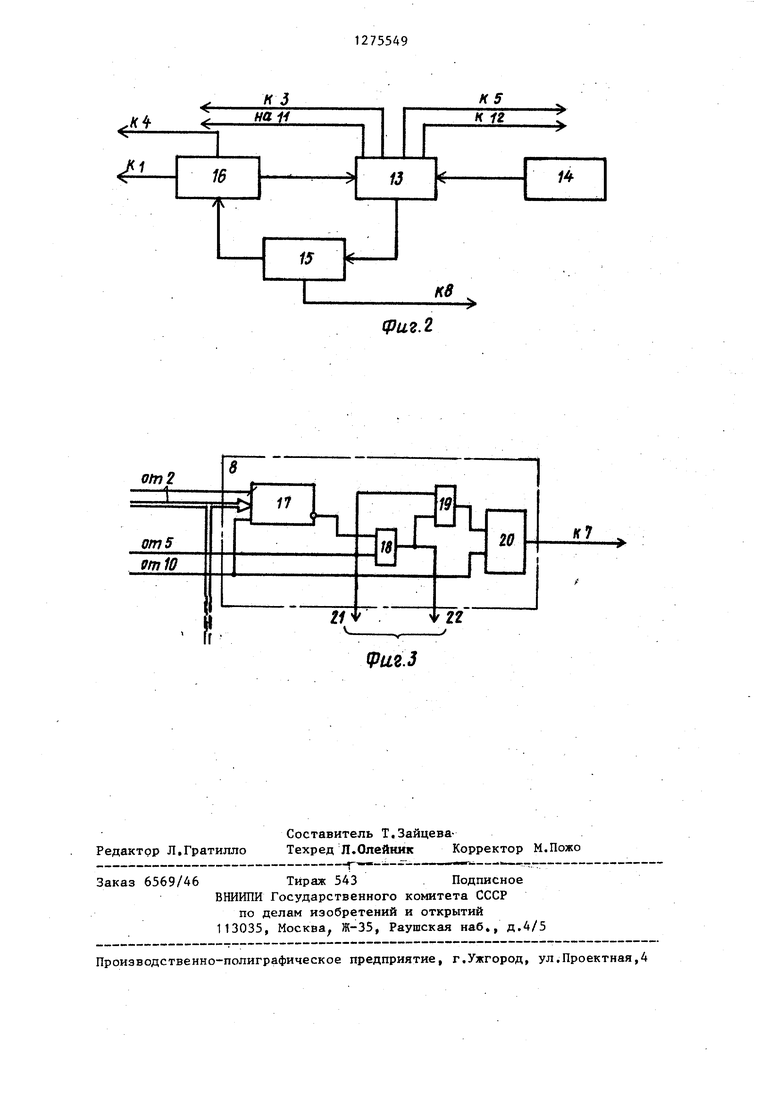

СО I1 Изобретение относится к вычислительной технике и может быть применено при создании контрольно-испытательной аппаратуры для контроля блоков памяти. Целью изобретения является повьппе ние быстродействия устройства. На фиг,1 представлена функциональ ная схема предложенного устройства; на фиг,2 и 3 - функциональные схемы блока 5шр авлен: я и одного канала блока местного управления соответственно, варианты вьтолнения. Предложенное устройство содержит (фиг-. 1) счетчик 1 адреса, блок 2 управления, блок 3 эталонных данных, первый коммутатор А, блок 5 сравнения, формирователи 6 сигналов, второ KOMMytaTop 7, блок 8 местного управ-ления, кроме того койта.ктную плату 9 с датчиками 10 сигнала наличия контролируемого блока памяти, программи руемый источник 11 питания и регистр 12. Блок 2 управления содержит (фиг.2 накопитель 13 программ контроля,пуль 14 управления, счетчик 15 циклов и г нератор 16 управляющих сигналов,В кая дом канале, предназначенном для контроля одного блока памяти, блока 8 местного управления, содержится (фиг.З) счетчик 17 тестов, элементы И 18 и ИЛИ 19 и триггер 20, Блок 8 имеет индикаторные выходы 21 и 22, Число каналов в блоке 8 соответствует числу контролируемых блоков памяти, размещаемых одновременно в контактной плате 9. , Устройство работает следующим образом. Блок 2 со(ержит программы .с набором команд, определякяцих контроль рлока памяти в режиме циклического перебора тестовых последовательностей и модификаций напряжений питания В накопитель 13 (фиг,2) с пульта 14 записывается программа контроля. На- копитель 13 в зависимости от сигналов, поступающих из генератора 16,вы дает сигналы на блок 13, блок 5,исfo ник 11 питания и регистр 12, Генератор 16 управляет работой коммутатора 4, формирует сигналы обмена с контролируемыми блЬками памяти, Счет чик 15 по сигналам из накопителя 13 выдает на генератор. 16 разрешение на смену режима реализуемого теста. Счетчик 1 (фиг.1) ho командам блока 2 формирует адреса, по которым запи9сываются или с.которых считываются данные. Блок 3 по командам блока 2 формирует записываемые и эталонные данные в режиме чтения. Блок 5 осуществляет сравнение считьгааемой информации с эталонными данными по соответствующим сигналам блока 2, На управляющие входы блока 5 поступает эталонная информация из блока 3 в режиме считывания. На выходах блока 5 формируется .сигнал в случае несовпадения эталонных данных с данньлми, соответствующими контролируемому блоку памяти из группы параллельно тестируемых блоков памяти. Сигнал несбответствий с выходов блока 5 передается в 6hoK 8. Повьшение быстродействия устройства достигается за счет обеспечения возможности параллельного контроля с конвейерной организацией тестирования блоков памяти. Предварительно в регистр 12, который является общим для всех каналов блока 8, по сигналам из накопителя 13 заносится информация о количестве тестов, составляющих тестовую программу проверки блока памяти, В начальный момент содержимое регистра 12 заносится в счетчик 17« . По мере загрузки проверяемых бло|сов пдмяти в контактирукнцие приспособления платы 9 соответствующими датчиками 10 формируются сигналы нулевого уровня, которые поступают В соответствующие каналы блока 8, на установочные входы счетчиков 17 и триггеров 20, В процессе прохождения тестовой программы контроля осуществляется одновременное уменьшение на единицу состояний счетчиков 17 по сигналам с блока 2 или до конца прохождения тестовой программы контроля-в случае благоприятного исхода тестирования, или до появления сигнала несоответствия с выхода блока 5 по какому-либо каналу, В последнем случае счетчик 17 соответствующего канала фиксирует номер тестовой последовательности, на котором произошел сбой или отказ в контролируемом блоке памяти, и на выходе триггера 20 вырабатывается сигнал, который поступает на соответствующий вход коммутатора 7, в результате происходит отключение шин адреса, данных управления и питания от соответствующего контактирующего приспособления платы 9 и тем самым обесгтечивается корректный съем бракованного блока памяти. После Установления нового блока памяти в плату 9 процесс тестирования его начнется синхронно с началом тестовой последовательности для других блоков памяти в плате 9. Таким образом осуществляется конвейерная организация тестирования блоков памяти. Такая организация тестирования блоков памяти может дать сущестеенньй выигрыш во времени контроля, так как время прохождения всей тестовой программы весьма значительно (десятки-сотни секунд) по сравнению с временем съема и установки отдельного блока памяти. Формула изобретения Устройство для контроля блоков па мяти, содержащее счетчик адреса, бло сравнения, блок эталонных данных,пер вый коммутатор,формирователи сигналов, программируемый источник питания и блок управления, одни из выходов которого соединены соответственно с входами счетчика адреса, с входами блока эталонных данных, с входа ми программируемого источника питани 12 494 с управляющим входом блока сравнения и с управляющим входом первдго коммутатора, одни из входов которого подключены к выходам счетчика адреса, а выходы - к одним из входов формирователей сигналов, одни из выходов которых соединены с одними из входов блока сравнения, другие входы которого и другие входы первого коммутатора подключены к выходам блока эталонных данных, причем другие входы формирователей сигналов являются входами устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены второй коммутатор, регистр и блок местного управления, вьгходы которого соединены с одними из входов второго коммутатора, а одни из входов - cd ответственно с. выходами регистра и с выходами блока сравнения, причем входы регистра и другие входы блока местного управления подключены к Другим выходам блока управления, другие входы второго коммутатора соединены соответственно с выходами формирователей сигналов и с вьпсодами программируемого источника питания, выходы второго коммутатора являются выходами устройства, управляющими входами, которого являются управляющие входы блока местного управления. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков | 1989 |

|

SU1705782A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для контроля блоков постоянной памяти | 1982 |

|

SU1049984A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

Изобретение относится к вычислительной технике и может быть применено при разработке контрольно-испытательной аппаратуры для контроля блоков памяти. Целью изобретения является повышение быстродействия устройства. Устройство- со; ержит счетчик адреса, блок управления, блок сравнения, первый коммутатор, формирователи сигналов, блок эталонных;даннвйс программируемый источник питания,, а также введенные блок местного управления, регистр и второй коммутатор. Повышение быстродействия достигается путем обеспечения контроля многих блоков памяти, закрепляемых в контактной плате, снабженной датчиками сигнала наличия контролтруемого бло1са памяти. 3 ил.

fPUZ.I

(PU2.2

к7

| Устройство для контроля блоковпОлупРОВОдНиКОВОй пАМяТи | 1979 |

|

SU799021A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Электронная промышленность,1982, № 4, с.36-40. | |||

Авторы

Даты

1986-12-07—Публикация

1985-07-09—Подача